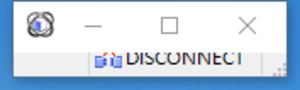

我在打开cs+ for cc的时候,为什么会变成这么小的窗口,如图所示,该怎么放大?

-

创建于2023-03-10

1个回答

-

- 小龙同学 Lv5 (0)

- 你好,你可以点击中间的方框进行放大,或者点击右下角变成双向箭头后,拖放该图标进行放大到想要的大小。

- 创建于2023-03-10

- |

- +1 赞 0

- 收藏

平台合作

相关推荐

请问下RH850系列使用CS+ For CC (CC-RH)如何step by step调试在C中嵌入的汇编代码? 我调试的时候用不能用step by step 麻烦指导一下,谢谢了!

你好,可以在CS+ FOR CC调试状态下,打开菜单栏view->disassemble,此时所有的程序都可以用汇编都可以正常调试。

瑞萨CS+ FOR CC v3.0无法打开RH850/F1KM系列的MCU工程,该如何解决?

瑞萨CS+ FOR CC v3.0无法打开RH850/F1KM系列的MCU工程,是因为较早版本的编译器内没有安装瑞萨RH850/F1KM系列的mcu设备文件,当编译器更新的CS+ FOR CC v6.0以上时,编译器内部就可选安装RH850/F1KM系列的mcu设备文件。也可以下载RH850/F1KM系列的mcu设备文件进行独立安装。

如何查看CS+ for CC环境下RH编译器版本?

RH编译器版本可以在CS+ for CC软件菜单栏【Help】下点击【About】查看。

IDE是CS+ for CC在Debug时设置不了断点;

建议通过快捷键“Ctrl+B”清除所有断点后,重新全部编译;

关于“汽车级MCU RH850使用FCL初始化不成功”,我现在遇到和您一样的问题,程序也是卡死在R_FCL_CopySections()不动了,您的“首先,在link option中定义预留段”这步设置是在哪儿的,我用的IAR找不到这个设置,请问您用的编译器是什么?

一般用的是瑞萨官方的CS+ FOR CC编译器,IAR的话应该是在.icf文件中要预留FCL的section段。

使用CS+ for CC编译器,默认输出的map文件太简单,如何设置输出详细的map??

在Link Options==》List中设置。

在CS+ for cc上开发R5F524T,想进行对ROM区(FFFE0000~FFFFFFFF)的读写,应该如何操作?

读取的话 您可以尝试下*((unsigned char *)(0xFFFE0000))这样是否可以访问。写的话我看RX24T手册这段空间是只读的。

CS+ for CC每次点编译都是全部编译(没动任何文件),即使把所有设置初始化也是一样的,但是新工程编译后再次点编译直接就能出结果是什么原因

如果没改动或者只改动一个文件,不需要点rebuild(Shift+F7),只需要点build(F7)即可。

http://cache.baiducontent.com/c?m=9d78d513d99200b8599d837e7d01d717470fd0777b978e1a2592d50ad2735a325a7ba6fe623510739292253a41f05e5c9da16b2d2a5f77f2dad58c41dbb0852858d2616b2e&p=b472c54ad5c34bf802b1cc2d021488&newp=82798956889d12a05abd9b7d0d1c98231610db2151d0da01298ffe0cc4241a1a1a3aecbf22231104d0c1796c00a44c59e1f632703d0034f1f689df08d2ecce7e&user=baidu&fm=sc&query=CS%2B+lib&qid=b10802c90001274b&p1=6 参考链接的例子,编译通不过,有大神帮看看吗?

这个是CS+开发环境自定义段的使用问题,可以通过瑞萨官方提供的Code Generator生成工程,然后参考以下链接,完成编译和自定义段的使用。[Notes] CS+ Code Generator for RL78 (CS+ for CC),CS+ Code Generator for RL78 (CS+ for CA,CX),【经验】瑞萨CS+软件工具开发RL78 MCU入门教程【经验】瑞萨RL78 MCU CS+建立和使用库文件详解

RL78 在使用CS+ for CC 时,boot 和App合并时报错?

你好,可能有以下原因 1、不能识别的相对路径,因为例程的默认安装路径在C盘下面.需要根据自己版本修改,sub_mot.txt也需要放在指定路径的文件夹里面. 2、可能是书写的语法出现问题,需要看一下语法。

瑞萨电子IDE环境CS+中如何设置仿真运行从RESET开始,而不是从main开始?

打开CS+ for CC,双击选择RH850 E1(LPD)(Debug Tool)->Download File Setting->Debug Information->Excute to the specified symbol after CPU Reset->No,在连接仿真器运行之后,将会从 jr32 __start ; RESET 处开始执行。

有没有RL78 CAN bootloader例子?用CS+ for CC

官网没有提供CAN bootloader完整的例子,不过我们有相关的支持案例,如网址:https://www.sekorm.com/news/6580.html 可以尝试联系我们FAE人员提供协助

请问下CC-RL中产生map文件里面的RomData section指的是哪里?

你好,如果是使用e2 studio的时候,可以通过图1看到memory的使用情况。如果是CS+ for CC,可以通过如下设置看到memory使用情况CC-RL (Build Tool)--> Link Options --> Others --> Display total size of sections:选择 Yes(-Total_size)。其中.moinotr是调试的存放信息,如果不进行调试,仅烧写到MCU的mot文件中是不会包括.moinotr1和.monitor2的。其中.vect、.callt0、.option_byte、.constf、.data、sdata、.security_id、.SLIB、.moinotr1、.monitor2、.const也都是算在ROMDATA中的。 program section是text和textf、RLIB加起来的。 ramdata section是bss,dataR,sbss,sdataR加起来的

RH850 CS+ for CC 如何获取自定义段的长度? 我自定义了一个段 #pragma section AA unit8_t A; unit16_t B; unit16_t C; #pragma section default 我怎么计算出我的段 AA 的大小? 然后在上电的时候 从EEL中copy同样大下的数据到AA中?

瑞萨RH850芯片使用 CS+ for CC可以从编译完的map文件中看出占用的FALSH大小,也可以通过计算存放变量的数据长度累加计算。