Silicon Labs针对数据中心交换机的时序解决方案组合,解决同步和异步架构问题

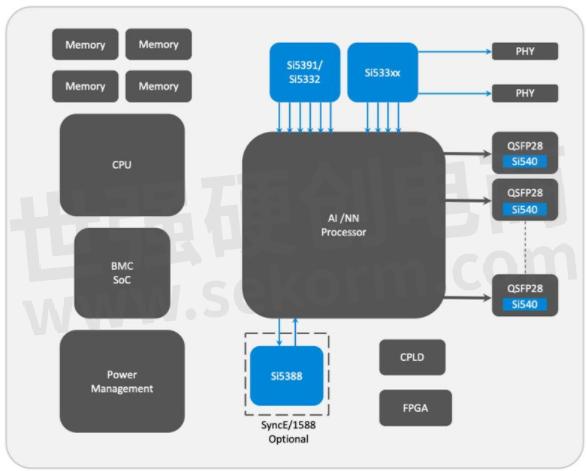

在数据中心交换机SoC平台中采用56G和112G SerDes可以显著提高带宽,但是随着这些数据速率和带宽水平的提高,参考时钟的RMS相位抖动要求降低一半,这带来了新的设计挑战。SILICON LABS(芯科科技)为100G/400G交换机平台提供广泛的时序产品组合,通过sub-100fs系列Si54x振荡器、Si5391时钟发生器、Si5395/4/2抖动衰减器,以及IEEE 1588网络同步器硬件和软件解决方案解决同步和异步架构问题。

针对交换机设计选择时序解决方案,首先要梳理所有参考时钟、性能水平以及设计中所需的相关时序功能(常称为时钟树)。交换机SoC和PHY数据表中通常会列出频率、输出格式和相关RMS相位抖动要求。在梳理时钟树和选择实施理想的时序解决方案时,建议考虑以下方面:

1、时序体系结构:在概述详细的时钟树之前,第一步是定义交换机设计是异步(或自由运行)还是同步,以及是否需要IEEE 1588 PTP同步支持。同步设计需要锁定来自另一个源的输入时钟,并且需要使用抖动衰减器在频率产生之前过滤来自输入参考时钟的抖动。或者,异步设计在本地产生所有频率,通常使用时钟发生器或振荡器。

2、性能:RMS相位抖动是选择时序解决方案之前要审查的格外重要的参数。随着数据速率和带宽水平的提高,参考时钟的RMS相位抖动要求提高了一倍,通常会将系统抖动容许量减半。用于400G交换机的最新一代交换机SoC和PHY集成了56G/112G SerDes,要求参考时钟的RMS相位抖动小于150fs,而较低的40G/100G带宽设计使用28G SerDes,对参考时钟的RMS相位抖动要求为300fs。建议按照重要性对时钟树进行总结,将RMS相位抖动要求最严格的时钟列在顶部。Silicon Labs的振荡器、时钟发生器和抖动衰减器根据RMS相位抖动性能水平进行分类,便于用户选择符合特定要求的合适器件。

3、频率灵活性:数据中心交换机设计通常需要不同频率的组合(在不同输出电压下具有不同输出格式级别)。 Silicon Labs获得专利的DSPLL和MultiSynth技术可提供高度时钟合成能力,可在多达12个输出上的整数和小数相关输出频率实现0ppm合成误差,同时可尽可能地减少外部元件并提供业界出众的抖动性能。Si5332/Si5391时钟发生器和Si5395抖动衰减器能够同时提供312.5M、156.25M、100M、50M和25M输出时钟,可满足单IC解决方案中整个数据中心交换机时钟树的要求。

4、功能集和集成:Silicon Labs的时序解决方案配备了许多功能,可以进一步优化和简化用户的交换机设计,例如无中断切换、信号损耗、降低EMI的扩频功能、频率选择功能、输出使能控制、多配置文件选择,以及集成晶体参考源。抖动性能至关重要,因此Silicon Labs的产品在所有的电源引脚上都纳入了片上LDO,从而实现处于业界前列的PSNR性能。通过片上实现抑制外部电源和板级噪声极大减少了电源滤波所需的外部组件数量,从而降低了电路板空间和成本,并确保了输出时钟抖动性能符合数据表规格限值。

5、定制:Silicon Labs的ClockBuilder Pro软件工具可指导用户针对自己的时钟树要求轻松、逐步地生成特定的时钟发生器或抖动衰减器配置文件。配置文件完成后,ClockBuilder Pro可针对用户的设计专门分配一个定制部件号,提供相关数据表附录,并允许用户将其保存以备后用。Silicon Labs的Si54x Ultra系列振荡器的部件编号生成可以直接在其网站上进行配置。

6、IEEE 1588:随着数据中心在通信基础设施中变得愈发重要,IEEE 1588 PTP将很快成为数据中心网络交换设备的标准,就像其在5G无线基础设施和核心/城域路由中一样。Silicon Labs提供了一种新的PTP时序方法,该方法支持G.8262、G.8262.1和G.8273.2 T-BC C类和D类。提供了一整套网络同步器、AccuTime软件和模块解决方案,非常适合数据中心交换应用中的分布式时序体系结构。

7、供应情况: 在短时间内采购足够的组件满足原型或生产构建并非易事。Silicon Labs采用以解决方案为导向的方法开发灵活、可编程的芯片,此类芯片可通过ClockBuilder Pro轻松配置,从而在制造流程中实现无缝集成,以在2周内为用户提供预编程样品,并在短短4周内完成生产。 Silicon Labs的现场编程器还能够即刻对空白设备进行编程,或使用I2C重新配置设备。

方框图

合适的Silicon Labs产品列表

- |

- +1 赞 0

- 收藏

- 评论 2

本文由宝丁转载自Silicon Labs,原文标题为:脊/叶和架顶式 (ToR) 交换机,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

Silicon Labs提供用于加速器卡设计的定制时钟发生器,降低组件数量、PCB面积和整体系统成本

Silicon Labs(芯科科技)广泛的可编程时钟发生器解决方案组合可以轻松定制,以便将加速器卡设计中所需的所有参考时钟合并到单一IC解决方案中,从而减少组件数量、PCB面积和整体系统成本。

【选型】Silicon Labs 时钟和振荡器芯片选型指南

目录- 计时解决方案 晶体振荡器(XO) 压控晶体振荡器(VCXO) 时钟发生器 时钟缓冲器 抖动衰减器 无线时钟 网络同步器

型号- SI56X,SI5382,SI5383,SI5380,SI5381,SI5386,SI5331X,SI5384,SI590,SI5315X,SI591,SI595,SI510,SI598,SI511,SI596,SI597,SI514,SI515,SI512,SI513,SI516,SI52142,SI52143,SI52144,SI51210,SI5394,SI5391,SI5392,SI5397,SI5332X,SI5395,SI569,SI54X,SI567,SI52111,SI52112,SI570,SI571,SI5344H,100G,SI53212,SI5332,SI53208,SI5330X,SI5335,SI53204,SI5334,SI5338,SI547,SI545,SI546,SI549,SL18860,SI5311X,SI5342,SL18861,SI5340,SI52208,SI5341,SI5346,SI52202,SI5347,SI5344,SI52204,SI5345,SI550,SI5348,SI554,SI552,SI5342H,SI5350,SI53306,SI5351,SI53102-AX,SI52212,SI5336X,SI561,SI562,SI560,SI565,SI566,SI564,SI51214,SI51211,SI51218,SI52146,SI52147,SI532,SI533,SI530,SI531,SI534,SI5334X,SI540,SI544,SI541,SI542

【应用】十路输出时钟的时钟发生器Si5341用于5G CU平台的时钟链路设计,时钟频点范围100Hz~1028MHz

本文推荐使用Silicon Labs高性能时钟发生器Si5341用于5G CU的主控平台时钟设计,有多达十路输出时钟,时钟频点范围是100Hz~1028MHz,涵盖了5G CU主控平台所需的全部频点,时钟路数足够多,可以尽量减少晶振的用量。

【经验】Silicon Labs时钟发生器SI5332时钟差分信号变单端输出问题及处理方法

Silicon Labs时钟发生器SI5332在使用CB Pro软件配置好电平之后,有工程师会有疑问,原本配置好的3.3V 125MHz lVDS电平 OUT/OUTB是否可以在配置不动的情况下单独分开做两个125MHZ单端时钟输出?本文将为你解析。

高性能抖动衰减器和时钟发生器的推荐晶体、XO、TCXO和OCXO参考手册

描述- 本资料为高性能抖动衰减器和时钟发生器推荐了晶振(XTAL)、晶振振荡器(XO)、温度补偿晶振(TCXO)和恒温晶振(OCXO)的列表。这些器件经过测试和认证,适用于Silicon Labs的高性能抖动衰减器和时钟发生器。资料中提供了基于测试样本的信息,并建议客户监控规格符合性和质量。此外,资料还提供了XTAL、XO、TCXO和OCXO的推荐型号、规格参数以及选择指南。

型号- TG-5500CA-67N40.0000MB,7X,ROX3827T3,NT7050BB,RTX7050A,NT7050BC,NX3225SA-48.000M-CS07559,TG-5500CA-08N 12.8000MB,SI5382,SI5383,SI5380,SI5381,SI5386,OH300-61003CF-012.8M,SI5384,S0242-X-001-3,SI5388,SI5389,O22S-L119-10.0MHZ-S,NZ2520SDA-54M-CUS5094C,CX3225SB48000D0FPJC1,TG-5500CA-68N,NZ2520SDA,OG2522CAN CSGJHG 12.8000MB,T75B-V319,TG-5500CA TCXO,CS-044,CS-043,E2S48.000F08M22SI,SI5391,SI5342-47,TG-5500CA-08N12.8000MB,T100F-012.8M,SI5395,SI537X,T100,7M54070010,NT7050BB-40M-ENA4199B,CX3225SB48000D0WPTC1,SI5392-97,TG-5500CA,RPT5032J,S0242-X-002-3,SI538X,7M54072004,E3S48.000F08M22SI,7M54072002,7M54072003,T200F-012.8M,7M54072001,STP3158LF,7X54070001,7M48070012,ROX2522S4,SI5344H,NX3225SA,NH14M09WA,SI539X,O22S-K319,S0242,E3SB,OH300,T75B-S319-12.80MHZ-S,O22S-K319-12.8MHZ-S,CX3225SB48000D0WPSC1,7X4807007,NH14M09TA,STP3268LF,E6518LF,SI5340,SI5341,CX3225SB,NZ2520SDA-48M-CUS5242A,SI5348,SI5342H,7N48071002,7N48071001,513872,T75B-V319-12.80MHZ,7M48072002,7M48072001,E6127LF,OH300-50503CF-012.8M,OG2522CANCSGJHG12.8000MB,STP3158LF6,NT14M09TA-12.8M-NSA3543A,TG-5500CA-67N,TG-5500CA-68N49.1520MB,CX3225SB54000D0FPJC1,NT7050BC-12.8M-NSA3517A,SI534X,NX3225SA-54.000M-CS07551,E3SB54.00,OG2522CAN,STP3268LF7,NH14M09WA-12.8M-NSA3540A,SI5371,SI5372,XTL571500-S315-006,O22S-L11,XTL571500-S315-007,RPT7050A,0F08M22SI,7M,7N,T200,T75B-S319 TCXO

【经验】网络同步时钟发生器SI5383的秒脉冲输出延时对齐方式的实现方法

Silicon Labs的网络同步时钟发生器SI5383支持直接锁定输入1 pps秒脉冲,将秒脉冲输入的信号进行频率合成一些其它频点时钟信号输出,这些输出是1 pps信号的同步信号。因为布板走线长度不一样,导致信号到达各个器件的时间会有一定的相位差,本文介绍一种消除该差的方法。

【应用】10路差分输出!DSP时钟电路中少不了这款时钟发生器

SI5341最大能支持10路差分输出,低抖动,完全满足DSP所需的时钟性能需求。

【经验】如何对时钟发生器Si5332进行烧录

Si5332是Silicon Labs公司推出的一款经典的时钟发生器产品。本文将主要介绍如何对这款产品进行烧录。首先把ClockBuilder Pro Field Programmer烧录工具和烧录座连接,使用USB线缆与电脑连接;然后打开ClockBuilder Pro客户端工具,最后一步就是对Si5332进行烧录操作。

【经验】时钟发生器SI5340输入切换失效问题的分析和解决

SI5340是Silicon Labs推出的一款经典高端时钟发生器,有用户在评估使用SI5340A-D-GM芯片时碰到输入选择问题,表现为选择对应的输入选通电平时,输入源没有跟随输入变化。本文将具体分析并解决该问题。

【经验】抖动衰减器Si5345如何匹配选择8K单端输入时钟信号?

Silicon Labs的Si5345的输入时钟最低频率刚好是8kHz信号,通常对于这个最低频率的处理,需要特别注意。很多应用时会直接采用直流耦合的方式进行匹配,但是对于Si5345来说,这个8k不能简单直接使用DC耦合。通常8kHz时钟信号在通信吕一般由两种,一种是正常的占空比40~60%之间的时钟信号,还有一种是占空比远远小于1%的窄脉冲时钟信号,这两种时钟信号的处理实际应用是完全不同的。

如何实现SI5342、SI5344和SI5345抖动衰减器锁相环动态调整?

Silicon Labs的超高性能抖动衰减器SI5342/SI5344/SI5345已经在通信客户中获得大量的应用。Silicon Labs SI5342/SI5344/SI5345时钟发生器内置Silicon Labs第四代专利锁相环DSPLL,自带I2C、SPI可编程接口,能够实现用户在线编程改变输出频率,实现在线调试和频率更新。本文讲述了实现抖动衰减器锁相环动态调整的方法步骤。

Si5397/96 双/四 DSPLL™ 任意频率、任意输出抖动衰减器 数据表

描述- Si5397/96是一款高性能、多路输出的DSPLL时钟倍频器,适用于需要高集成度和独立时序路径的应用。该产品具备任意频率转换能力,提供超低相位抖动性能,支持多种输入和输出选项,广泛应用于高速网络通信和同步以太网等领域。

型号- SI5397J-A-EVB,SI5397B-A-GM,SI5396J-A-GM,SI5396L-A-EVB,SI5396C-A-EVB,SI5397K-A-GM,SI5396M-A-GM,SI5396 J,SI5396 M,SI5396 K,SI5397 J,SI5396 L,SI5397 K,SI5396 A,SI5396 B,SI5397 A,SI5397A-AXXXXX-GM,SI5397L-A-GM,SI5396A-A-GM,SI5397 D,SI5396D-A-GM,SI5396J-A-EVB,SI5396 C,SI5397 B,SI5396 D,SI5397 C,S5397,SI539FG-RXXXXX-GM,SI5396B-A-GM,SI5396K-A-GM,SI5397A-A-GM,SI5396A-AXXXXX-GM,SI5397C-A-GM,SI5397,SI5396C-A-GM,SI5397J-A-GM,SI5396,SI5397D-A-GM,SI5397M-A-GM,SI5396L-A-GM,SI5397A-A-EVB

【产品】四路独立DSPLL超低抖动衰减器,简化设计复杂度

针对Si5347-B版本实际应用过程中碰到的Bug和客户提出的应用需求,Silicon Labs最新推出了一款可用于在8kHz~750MHz输入时钟抖动衰减时钟发生器Si5347-D,其实用的可编程延时调节、精准的缓变率调节及可配置的自由振荡模式等功能大大简化了系统设计的复杂度。

【经验】网络同步时钟发生器Si5383配置1588同步时钟的CBPro方案

Silicon Labs的Si5383是一个内置多个DSPLL的网络同步时钟发生器,有用户需要配置一组Si5383的时钟profile用于实现1588网络同步设计(1588伺服软件用户自行解决),其设计要求中存在无法满足的情况,本文就将具体说明并给出解决方案。

电子商城

现货市场

服务

提供是德(Keysight),罗德(R&S)测试测量仪器租赁服务,包括网络分析仪、无线通讯综测仪、信号发生器、频谱分析仪、信号分析仪、电源等仪器租赁服务;租赁费用按月计算,租赁价格按仪器配置而定。

提交需求>

朗能泛亚提供是德(Keysight),罗德(R&S)等品牌的测试测量仪器维修服务,包括网络分析仪、无线通讯综测仪、信号发生器、频谱分析仪、信号分析仪、电源等仪器维修,支持一台仪器即可维修。

提交需求>

登录 | 立即注册

提交评论