【经验】智多晶FPGA上实现LTE削峰算法PC-CFR

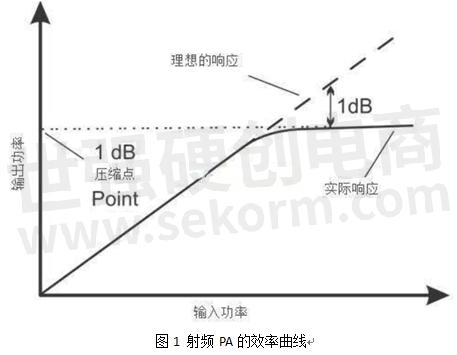

如今的4G LTE以及5G NR下行信号都是OFDM调制,OFDM符号是由多个独立的子载波调制而成,当各个载波的相位相近时,各个调制符号的功率进行叠加,使得瞬时功率较大,导致较高的峰均比(PAPR)。一般的功率放大器的动态范围是有限的,当信号的功率超过了放大器的线性范围,将导致信号的非线性失真和系统性能下降。我们用一个图来阐述:

当输入PA的信号功率逐渐加大,在线性区范围内,其输出也是线性的,当输出开始出现非线性时,即达到PA的1dB压缩点,传统的做法是进行功率回退,保证PA工作在线性区内,那么功放效率就变低了,原因是OFDM信号的高PAPR特性,使得部分峰值进入PA的饱和点,LTE信号的PAPR实际会达到12dB。

CFR算法

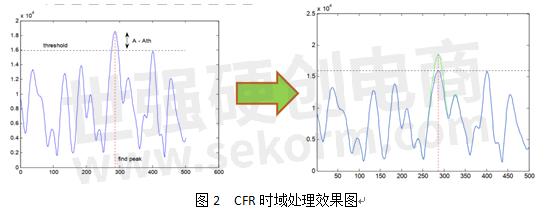

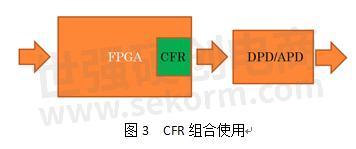

CFR(Crest Factor Reduction)算法是一种直接在数字域上面处理的方法,对于超出设定门限值的信号,直接在数字域上进行处理和消除,如图2所示,它可用于缩小一个传输信号的动态范围,以便用于传输该信号的放大器能够在运行时减少回退。在典型的无线系统中,CFR一般会搭配数字预失真(DPD)组合使用,或者后端直接挂APD芯片。目前CFR算法有PW-CFR、NS-CFR和PC-CFR,常用的还是PC-CFR,其削峰能力最佳,本文就针对PC-CFR算法,在智多晶AD9365射频开发板上进行测试和实现。

FPGA实现

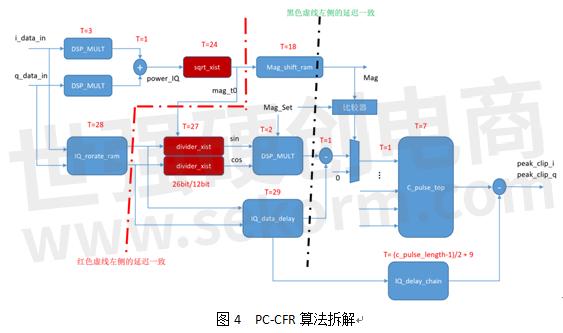

PC-CFR的基本原理是提取出超过门限的信号值,再经过脉冲成型滤波,得到与输入信号频谱相匹配的谱状脉冲,之后与原始输入高PAPR信号进行抵消,得到一个被“削掉”峰值的低PAPR信号。我们把PC-CFR算法用框图拆解,可以参考图4所示:

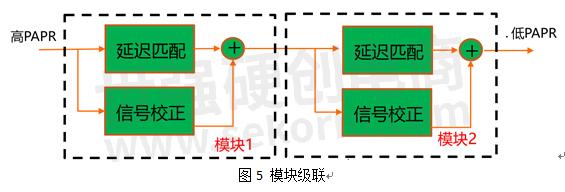

这里主要用到乘法器、开平方根、除法器等IP,其中乘法&除法器已经集成到HqFPGA编译工具里,开平方根IP之后也会集成进去供用户直接调用,目前是以源码形式在工程里实现。在C_pulse_top里实现了8个峰值的抵消能力,为了实现更好的削峰效果,我们级联了2个算法模块,可以达到深度削峰。

CFR测试

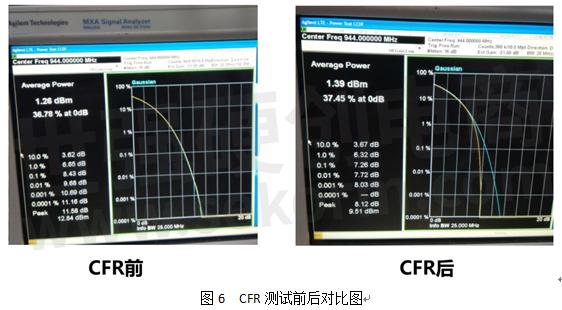

用keysight信号源开启FDD-LTE 20M带宽,频点944MHz,设置一定的削峰门限值并在综测仪上观测CCDF曲线图。

可以看到0.01%的峰值在CFR前是9.68dB,CFR之后降到7.72dB,抵消差不多2dB,EVM测试后恶化大概2.5%左右。需要注意,削峰算法是直接从时域上改变了信号的相位,因此抵消越多,EVM会变得越差,实际应用需要取一个折中。经过CFR模块的信号,PAPR降低了,再输出给后端DPD模块或者APD芯片,组合起来可以显著提高功放效率。

- |

- +1 赞 0

- 收藏

- 评论 2

本文由天安云谷门面担当转载自西安智多晶,原文标题为:智多晶FPGA上实现LTE削峰算法PC-CFR,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

评论

全部评论(2)

-

![]()

![]() 大熊猫 Lv4. 资深工程师 2021-01-10有没有评估过用你们这个FPGA做萧峰的一个资源

大熊猫 Lv4. 资深工程师 2021-01-10有没有评估过用你们这个FPGA做萧峰的一个资源 -

![]()

![]() 用户69995512 Lv2. 工程师 2020-11-20有代码吗

用户69995512 Lv2. 工程师 2020-11-20有代码吗

相关推荐

【经验】如何在FPGA上实现低成本开根号运算?

开根号运算是科学计算和工程应用中基本而重要的运算之一,在QuartusII和ISE开发软件中,都集成了开根号的ip核,这些底层源码对于用户来说是不可见的,那么如何在西安智多晶的FPGA中实现开根号运算,是本文要探讨的课题。

【经验】西安智多晶5000系列FPGA内嵌MCU调试测试指南

西安智多晶推出的Seal 5000 FPGA SA5Z-30系列内部合封Cortex M3硬核,最高主频可达200Mhz,32KB数据RAM和128KB指令RAM。本文针对FPGA内嵌M3硬核的使用做简洁的开发过程。

【经验】解析智多晶合封系列FPGA中DDR2的应用

合封系列FPGA可以应用在需要大量缓存数据的场合,比如工业数据采集卡、视频处理应用以及无线通信中的数据采集板,如果各位读者朋友们有需要用到FPGA+DDR2架构的,可以联系智多晶,智多晶会提供完整的DDR2 Control IP,甚至亲手为用户写好应用层部分的程序,并为用户调试好。

【选型】国产FPGA SL2-25E-8U324替代XC6SLX16 CSG324用于工业伺服控制器,有效应对交期问题

客户在工业伺服控制器中用到一款Xilinx FPGA,但因为交期问题需要国产化替代,使用型号是XC6SLX25-CSG324,主要用于做逻辑控制和与MCU交互数据、进行数据处理,给客户推荐了西安智多晶SL2-25E-8U324,可以兼容替代。

【应用】国产海狮系列FPGA SL2E-5E用于扩展外设接口,集成flash,工作频率高达300MHz

西安智多晶的SL2E-5E是一款集成了5K逻辑单元的小规模FPGA,但是比CPLD容量更大,能实现更多的逻辑设计,同时该FPGA内部集成了Flash,不需要再外接配置用的Flash,简化了电路设计。

Seal(海豹)SA5Z-30 FPGA 产品手册

型号- 海豹5000系列,SA5Z-30-D2,SA5Z-30-ES,SA5Z-30-D0-UBGA324,SA5Z-30-D0,SA5Z-30-D1,SA5Z-30-D1-UBGA213,SA5Z-30-D2-8U213C5,SA5Z-30,SA5Z-30-D1-8U213C4,SA5Z-30-D2-8U213C6,SA5Z-30-D2-UBGA213,SEAL 5000系列,SA5Z-100-D1-8U324C,SA5Z-30-D0-8U324C6,SA5Z-30 系列,SA5Z-30-D1-8U213C,SA5Z-30-D2-8U213C

SA5Z-30 FPGA 器件概述

型号- SA5Z-30-D3-U256,SA5Z-30,SA5Z-30-D0-U324,SA5Z-30-D1-U213,SA5Z-30-D0-U324C,SA5Z-30-D2-U256,SA5Z-30 系列,SA5Z-30-D2,SA5Z-30-D3,SA5Z-30-D0,SA5Z-30-D1

【IC】智多晶28nm FPGA家族SEAL5000系列新发SA5Z-100,采用低功耗28nm@LUT6工艺

2022年的下半年,西安智多晶28nm SEAL5000家族系列喜迎重量级新成员SA5Z-100,采用先进低功耗的28nm@LUT6工艺,集成高达8个通道13.1Gbps的高速SerDes,支持PCIe2.0 x4以及HDMI2.1等接口协议。

【应用】基于智多晶Sealion 2000系列FPGA的工业控制解决方案,具有低功耗优势

智多晶Sealion 2000系列FPGA基于低功耗工艺设计,旨在满足低成本高性价比客户的需求,使系统设计师在降低成本的同时又能够满足不断增长的应用要求,在低成本、低功耗FPGA市场处于领导地位。

SA5Z-50 FPGA 器件概述

型号- SA5Z-50-D0-7F484,SA5Z-50,SA5Z-50-D0-U324,SA5Z-50-D0-F484,SA5Z-50-D0-7U196,SA5Z-50-D0-U196,SA5Z-50-D0-8U324C,SA5Z-50-D0,SA5Z-50 系列,SA5Z-50-D1

Sealion(海狮)SL2E-7E/V FPGA产品手册

型号- SL2E-7V-UBGA400,SEALION 2000 系列,SL2E-7V,SEALION 2000,SL2E-7V-E144,SL2,SL2E-7E,SEALION SL2E-7E,SEALION SL2E-7V,SL2S-12E-8F256C,SL2E-7V-U256

电子商城

现货市场

登录 | 立即注册

提交评论