【应用】国产海狮系列FPGA SL2E-5E用于扩展外设接口,集成flash,工作频率高达300MHz

本文介绍的板卡主要功能是多串口设备通信采集板卡,通过串口采集的数据会送到加密模块进行加密处理。

1. 应用介绍

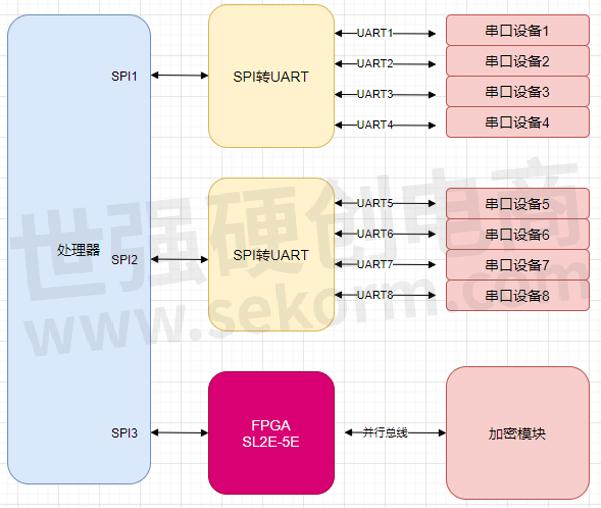

板卡部分功能框图如下所示。

图 1 板卡主要功能框图

该板卡采用处理器的2个SPI接口通过SPI转4 UART器件扩展了8个UART通信接口,分别接到8个串口设备。除此之外,处理器还需要和一个加密模块进行通信,加密模块采用的是local bus并行总线接口,而处理器本身并不具有并行总线,只能通过外部器件进行扩展。因为加密模块的通信速率只需要大概500Kbit,而处理器的SPI接口速率可以达到10Mbps,因此完全可以采用SPI接口来实现。因为现在几乎找不到带并行总线的转换芯片,即使有,也不一定能符合加密模块的时序要求,所以考虑采用FPGA来实现。这里选择了西安智多晶的SL2E-5E 5K系列的FPGA,它具有体积小,使用灵活的特点,不需要外接配置芯片,很适合这个应用。

本文介绍了SL2E-5E的设计和使用方法,供其他人作为设计参考。

2. SL2E-5E介绍

SL2E-5E是西安智多晶海狮系列的FPGA。SL2E-5E主要性能特点如下:

●具有5040个逻辑单元

●集成108Kbit存储器

●支持1.2Gbps的MIPI接口

●支持 400Mbps DDR2 SDRAM 接口

●编程/区域擦除周期:最小 100,000 cycles

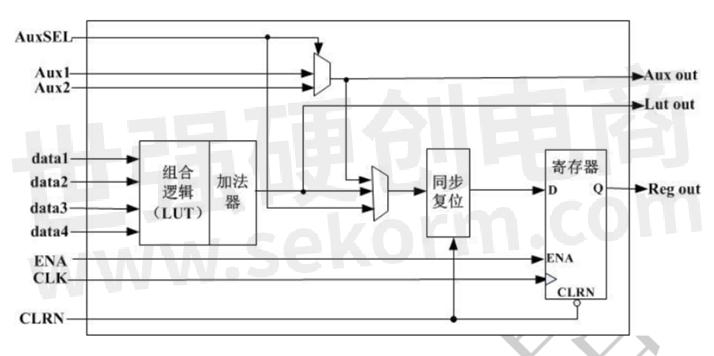

SL2E-5E的逻辑单元框图如下所示。

图 2 SL2E-5E逻辑单元框图

3. SL2E-5E原理图设计

SL2E-5E原理图设计如下图所示。

图 3 SL2E-5E原理图

图中上方为SL2E-5E芯片电路图,其中上半部分的右侧为SPI接口,接处理器,左侧为并行local bus,接加密模块。左下角B2引脚为时钟输入,这里外接了25MHz的有源晶振,在FPGA内部可以直接用25MHz作为时钟,也可以通过内部PLL进行倍频后使用。

原理图下方分别为JTAG接口、3.3V电源滤波电容和1.2V内核电源电路。JTAG接口用来给FPGA下载程序。3.3V和1.2V需要每个引脚配置1颗1μF陶瓷电容作为去耦使用。1.2V内核电源根据厂家建议,需要提供最大1A电流,这里选用圣邦微的SGM6010把3.3V转换为1.2V给FPGA内核供电,最大可以输出3A电流。

4. SL2E-5E实物图

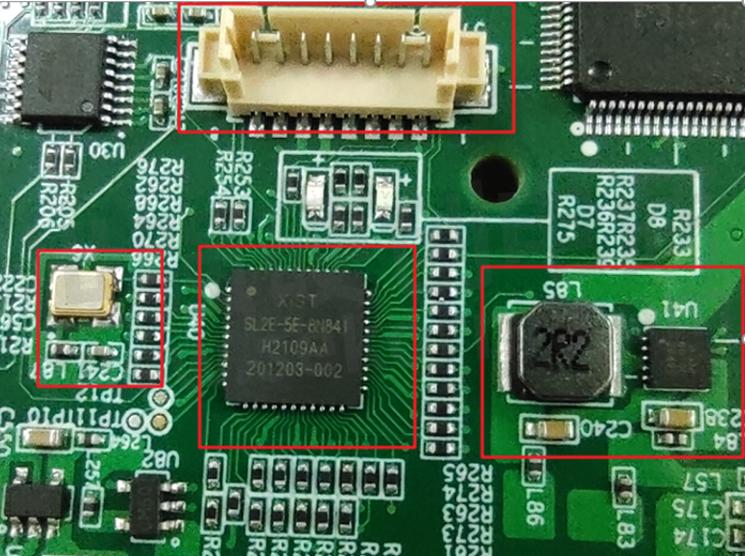

SL2E-5E的PCB实物图如下所示。

图 4 SL2E-5E PCB图

其中上方为JTAG接口,中间为SL2E-5E芯片,右边为3.3V转1.2V芯片,左边为25M有源晶振。PCB的设计主要的原则就是SL2E-5E相关器件尽量靠近,比如晶振,1.2V电源等。因为设计上没有用到高速信号,所以PCB的布线也不需要特殊处理。

5. 结论

西安智多晶的SL2E-5E是一款集成了5K逻辑单元的小规模FPGA,但是比CPLD容量更大,能实现更多的逻辑设计,同时该FPGA内部集成了Flash,不需要再外接配置用的Flash,简化了电路设计。此外选的FPGA型号为SL2E-5E-8N84I,芯片封装为QFN84,尺寸只有7mmx7mm,有效节约了PCB空间。这一设计是用SPI接口扩展一个并行接口,速率并不高,采用SL2E-5E完全可以满足要求。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由深蓝的鱼提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【应用】国产智多晶FPGA助力自动化测试设备扩展上百GPIO口,解决MCU端口不足痛点,核电压为1.2V

在一款自动化测试设备上,需要控制5个步进电机、86个电磁铁和几十个指示灯,以及外部通讯接口,使用的雅特力的AT32F407RCT7,由于控制逻辑并不复杂,需要使用的IO会比较多,因此需要对MCU的IO口进行扩展。客户希望在扩展的控制芯片增加步进电机的驱动,只需要发送指令就可以控制电机的旋转。推荐了智多晶的FPGA SL2E-5E-8M121I。

【应用】基于智多晶Sealion 2000系列FPGA的工业控制解决方案,具有低功耗优势

智多晶Sealion 2000系列FPGA基于低功耗工艺设计,旨在满足低成本高性价比客户的需求,使系统设计师在降低成本的同时又能够满足不断增长的应用要求,在低成本、低功耗FPGA市场处于领导地位。

【应用】智多晶海狮2000系列FPGA用于小基站AAU,具有丰富的逻辑资源,核电压1.2V/3.3V

基站中必须使用FPGA来实现物理层协议中的数字功能,推荐使用智多晶海狮2000系列FPGA。

【经验】如何在FPGA上实现低成本开根号运算?

开根号运算是科学计算和工程应用中基本而重要的运算之一,在QuartusII和ISE开发软件中,都集成了开根号的ip核,这些底层源码对于用户来说是不可见的,那么如何在西安智多晶的FPGA中实现开根号运算,是本文要探讨的课题。

【选型】国产FPGA SL2-25E-8U324替代XC6SLX16 CSG324用于工业伺服控制器,有效应对交期问题

客户在工业伺服控制器中用到一款Xilinx FPGA,但因为交期问题需要国产化替代,使用型号是XC6SLX25-CSG324,主要用于做逻辑控制和与MCU交互数据、进行数据处理,给客户推荐了西安智多晶SL2-25E-8U324,可以兼容替代。

【经验】西安智多晶5000系列FPGA内嵌MCU调试测试指南

西安智多晶推出的Seal 5000 FPGA SA5Z-30系列内部合封Cortex M3硬核,最高主频可达200Mhz,32KB数据RAM和128KB指令RAM。本文针对FPGA内嵌M3硬核的使用做简洁的开发过程。

【产品】基于智多晶SL2-25E FPGA芯片的软件无线电(SDR)评估板,适用于项目开发初期验证、教学及培训

为了更好让无线通信客户评估智多晶FPGA芯片,西安智多晶为客户打造了一个专业的软件无线电(SDR)评估板,可用于客户前期的项目预研,其核心器件是西安智多晶的SL2-25E FPGA芯片,F256封装。这个评估板卡非常适合小带宽、低成本的通信项目,专网或公网的应用。

【经验】智多晶FPGA上实现LTE削峰算法PC-CFR

CFR算法是一种直接在数字域上面处理的方法,对于超出设定门限值的信号,直接在数字域上进行处理和消除。目前CFR算法有PW-CFR、NS-CFR和PC-CFR,常用的还是PC-CFR,其削峰能力最佳,本文就针对PC-CFR算法,在智多晶AD9365射频开发板上进行测试和实现。

Seal(海豹)SA5Z-30 FPGA 产品手册

型号- 海豹5000系列,SA5Z-30-D2,SA5Z-30-ES,SA5Z-30-D0-UBGA324,SA5Z-30-D0,SA5Z-30-D1,SA5Z-30-D1-UBGA213,SA5Z-30-D2-8U213C5,SA5Z-30,SA5Z-30-D1-8U213C4,SA5Z-30-D2-8U213C6,SA5Z-30-D2-UBGA213,SEAL 5000系列,SA5Z-100-D1-8U324C,SA5Z-30-D0-8U324C6,SA5Z-30 系列,SA5Z-30-D1-8U213C,SA5Z-30-D2-8U213C

SA5Z-30 FPGA 器件概述

型号- SA5Z-30-D3-U256,SA5Z-30,SA5Z-30-D0-U324,SA5Z-30-D1-U213,SA5Z-30-D0-U324C,SA5Z-30-D2-U256,SA5Z-30 系列,SA5Z-30-D2,SA5Z-30-D3,SA5Z-30-D0,SA5Z-30-D1

【IC】智多晶28nm FPGA家族SEAL5000系列新发SA5Z-100,采用低功耗28nm@LUT6工艺

2022年的下半年,西安智多晶28nm SEAL5000家族系列喜迎重量级新成员SA5Z-100,采用先进低功耗的28nm@LUT6工艺,集成高达8个通道13.1Gbps的高速SerDes,支持PCIe2.0 x4以及HDMI2.1等接口协议。

【经验】解析智多晶合封系列FPGA中DDR2的应用

合封系列FPGA可以应用在需要大量缓存数据的场合,比如工业数据采集卡、视频处理应用以及无线通信中的数据采集板,如果各位读者朋友们有需要用到FPGA+DDR2架构的,可以联系智多晶,智多晶会提供完整的DDR2 Control IP,甚至亲手为用户写好应用层部分的程序,并为用户调试好。

电子商城

现货市场

登录 | 立即注册

提交评论