【选型】采用锁相环频率合成技术时钟芯片Si5342H和i5344H用在数据中心相干模块,时钟抖动90ps

目前数据中心越来越多,对于产品可靠性越来越高,数据中心其中一个核心部件就是相干光模块,目前100G、200G、400G相干光模块使用也越来越多,相干模块需要的时钟频率高,需要时钟抖动小,可以随意可配,一般时钟芯片无法满足要求,我们找到了SILICON LABS,厂家推荐了其优势产品Si5342H和i5344H。

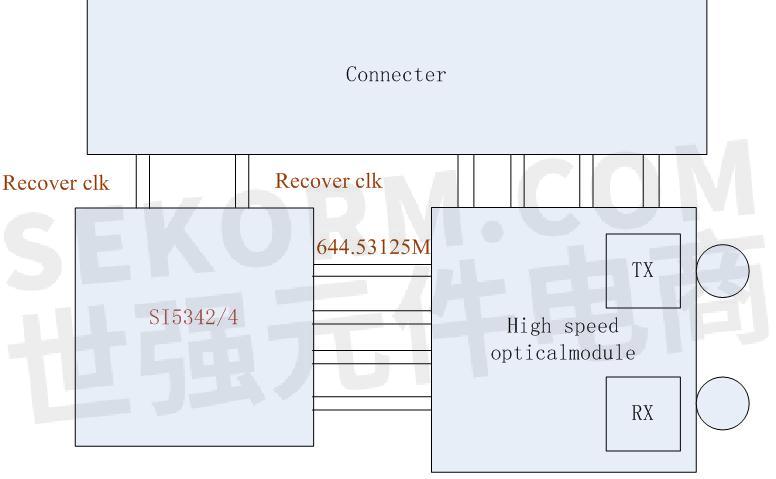

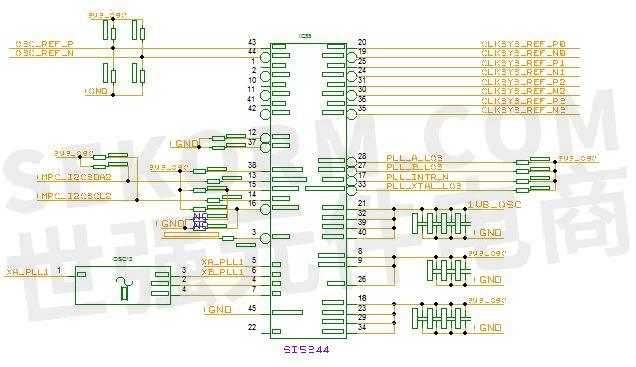

Si5342H和i5344H时钟芯片采用锁相环频率合成技术,支持最高2.7GHz的时钟信号输出,且最高支持2或者 4路高频率时钟输出。该产品可以单芯片解决多个晶振布局的多晶振时钟问题,提供一站式时钟模块功能需求,即节省了空间,也不会带来分离器件的噪声。此外,Si5342H/44H采用Silicon Labs公司独有的DSPLL技术,jitter可以减少到100fs以内,能够满足相干模块的时钟需求,基于此,我们尝试使用此芯片进行设计,相干模块系统框图如图1所示,SI5344时钟图如图2所示。

图1 相干模块系统框图

图2 SI5344时钟图

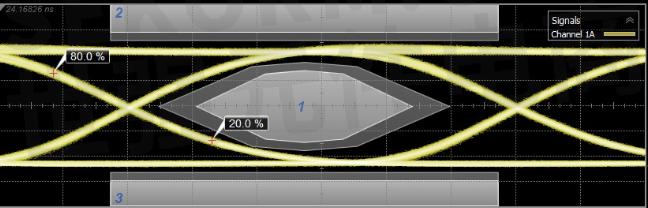

采用SI5344的DSPLL技术+MultiSynth技术,输出频率用于发射器和接收器时钟的超高性能抖动衰减PLL,输出频率644.53125M,外部参考时钟由Si532提供。我们对设计好的板卡进行整机测试,以验证时钟的温度性,整机测试结果如图3所示,光眼图测试波形如图4所示。

测试项目 | 测试方法 | 测试结论 |

高温测试 | 在40度情况下,连续16小时,测试数据收发包是否正常。 | 通过 |

低温测试 | 在-10度情况下,连续16小时,测试数据收发包是否正常。 | 通过 |

常温测试 | 在25度情况下,连续16小时,测试数据收发包是否正常。 | 通过 |

光眼图测试 | 测试光眼图是否在参考模板内。 | 通过 |

图3 整机测试结果

图4 光眼图测试波形

数据中心相干模块在选取时钟发生器的时候需要注意:

1. DSPLL技术+MultiSynth的时钟发生器选取的时候,需要注意被供时钟的路数,输出时钟还能根据供应电压(1.5V, 1.8V, 2.5V, 3.3V)和信号格式 (LVPECL, LVDS, CMOS, HCSL, SSTL, HSTL),输出时钟的注意抖动参数,本项目时钟抖动90ps,能够满足要求,另外需要考虑时钟是否需要带时钟恢复功能;

2. 在时钟发生器布线时,单端需要严格控制50欧阻抗,差分必须严格控制100欧阻抗;

3. 在时钟发生器布线时,最好芯片下面包铜处理,芯片下不要走其他无关的信号,这样保证比较好EMC性能;

4. 整改芯片需要保证时钟芯片和被接芯片能够电平匹配好,这个尤为重要;

5. Silicon Labs是晶振的全球领导企业,DSPLL技术+MultiSynth的时钟发生器能够满足设计要求。

- |

- +1 赞 0

- 收藏

- 评论 16

本文由drwyh提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

评论

全部评论(16)

-

![]()

![]() 喜欢笑的那个她 Lv7. 资深专家 2018-11-14好

喜欢笑的那个她 Lv7. 资深专家 2018-11-14好 -

![]()

![]() Ai少年风华 Lv6. 高级专家 2018-11-07学习

Ai少年风华 Lv6. 高级专家 2018-11-07学习 -

![]()

![]() 超超0821 Lv5. 技术专家 2018-11-07内容可学习,不错。

超超0821 Lv5. 技术专家 2018-11-07内容可学习,不错。 -

![]()

![]() qditz Lv9. 科学家 2018-11-06了解了解

qditz Lv9. 科学家 2018-11-06了解了解 -

![]()

![]() 风火轮 Lv4. 资深工程师 2018-11-02了解下

风火轮 Lv4. 资深工程师 2018-11-02了解下 -

![]()

![]() Paulwang Lv8. 研究员 2018-10-30还不错

Paulwang Lv8. 研究员 2018-10-30还不错 -

![]() MagicMoon Lv8 2018-10-30学习学习

MagicMoon Lv8 2018-10-30学习学习 -

![]()

![]() 桃梅 Lv7. 资深专家 2018-10-29不错

桃梅 Lv7. 资深专家 2018-10-29不错 -

![]() 用户38678025 Lv3 2018-10-28这个是好东西!收藏一下!

用户38678025 Lv3 2018-10-28这个是好东西!收藏一下! -

![]()

![]() 幸福 Lv7. 资深专家 2018-10-28不错

幸福 Lv7. 资深专家 2018-10-28不错

相关推荐

【选型】三点关键因素决定5G基站时钟选择SI5386A-E-GM还是LMK04828

Silicon Labs SI5386A-E-GM集成DSPLL核心技术的JESD204B去抖时钟芯片,广泛用于5G基站设备中。SI5386A-E-GM和LMK04828都是目前比较主流的无线时钟发生器,但是相对于SI5386A-E-GM来说,LMK04828部分性能、应用特点是无法媲美的。

【经验】时钟发生器Si5341型号定制以及输出串扰问题解决方法

Silicon Labs公司推出的时钟发生器Si5341最大能够支持10路差分输出,输出频率范围100Hz~712.5MHz,输出抖动范围均小于100 fs(0.1 ps),并且Si5341内部带有模拟锁相环,配合Silicon Labs的专利MultiSynth技术,能够以0 ppm合成所需的频点,本文将详细介绍Si5341型号定制以及输出串扰问题解决方法。

【经验】如何实现SI534X/SI538X时钟发生器SPI在线编程?

Silicon Labs SI534X、SI538X时钟发生器包括基于模拟PLL的SI5340、SI5341和基于DSPLL技术的SI5342、SI5344 、SI5345、SI5342H、SI5344H、SI5346、SI5347、SI5348以及无线专用时钟SI5380、SI5382、SI5386等时钟芯片产品。目前在光通信、数据中心、服务器、小基站、光模块等产品中有广泛的应用

Si5355任意频率1–200 MHZ四频8输出时钟发生器

描述- Si5355是一款高度灵活的时钟发生器,能够合成高达200 MHz的任意频率,具有四个输出银行,每个银行支持两个相同频率的CMOS输出。该设备采用Silicon Laboratories的专利MultiSynth分数除法技术,所有输出均保证具有0 ppm频率合成误差。Si5355支持多种配置,可通过ClockBuilder™在线工具进行定制,适用于多种应用,如打印机、存储、音频/视频、网络、计算和通信等。

型号- SI5355,SI5356-RVB,SI5355-BXXXXX-GMR

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

Si5364 SONET/SDH精密端口卡时钟IC

描述- Si5364是一款高性能的时钟切换和时钟发生器,适用于SONET/SDH系统中的高精度时钟应用。该器件具有超低抖动时钟输出,支持19、155或622 MHz的四个独立时钟输出,并具备自动或手动控制的时钟输入切换功能。Si5364采用Silicon Laboratories的DSPLL技术,提供优异的抖动性能,并简化设计。该器件适用于核心交换机和数字交叉连接等应用。

【经验】高性能去抖时钟发生器Si5347输入输出延时调整功能的应用注意事项

Silicon Labs Si5347是一款内置4个DSPLL的高性能去抖时钟发生器,实时增加了I/O延时调节功能(即输入输出延时调整功能)。本文将主要讲解需要使用调节功能时需要着重注意的事项。

【经验】关于SI5383时钟芯片寄存器配置的两点注意事项

Silicon Labs Si5383是一个内置多个DSPLL的网络同步时钟发生器,支持1PPS输入/输出,支持SyncE和IEEE 1588。本文介绍关于SI5383时钟芯片寄存器配置的两点注意事项。

创新的DSPLL®和MultiSynth时钟架构支持高密度10/40/100g线路卡设计

描述- 本文介绍了Silicon Labs推出的新一代时钟发生器和抖动衰减器,旨在支持高速、灵活、低抖动的时钟合成,适用于10/40/100G以太网和OTN设备。这些设备采用第四代DSPLL架构,提供高集成度、低抖动性能,并支持“即飞”频率重新配置,简化系统设计,降低成本。文章还比较了Si5345/44/42时钟发生器与传统时钟架构的性能差异,并展示了其在高密度线路卡设计中的应用优势。

【经验】一种去抖时钟信号发生器SI5345匹配问题引起的失锁问题解决方法

Silicon Labs公司推出的高性能去抖时钟信号发生器SI5345是一款经典的时钟产品,目前已经应用于各种通信、工业、医疗、仪器等行业中,其强大的抖动抑制能力让同行产品相形见绌,这得益于其集成的第四代高性能DSPLL核心技术。有如此优良的表现,使得SI5345的应用越来越多,但是工程师们在使用SI5345的时候也碰到一些应用问题,需要引起大家的注意。

浅谈新型去抖时钟发生器SI5345的工作状态机工作流程

SI5345是Silicon Labs公司的一款基于第四代DSPLL专利技术的新型去抖时钟发生器产品,同时配合Silicon Labs特有的MultiSynth频率合成技术,支持整数频率合成和小数频率合成,拥有极佳的输出频率抖动指标,目前已经广泛用于各种数据通信及仪器设备产品中,是广大硬件工程师设计时钟链路不可或缺的一款时钟芯片。

用于Altera FPGA的Silicon Labs振荡器、缓冲器和时钟发生器

描述- Silicon Labs提供多种频率灵活的时钟、时钟发生器、时钟缓冲器和振荡器,适用于Altera FPGAs的时钟需求。这些产品利用DSPLL和MultiSynth技术,实现低抖动频率合成和分配。产品包括可编程VCXO、低抖动缓冲器等,适用于不同Altera平台,如Stratix V、Arria V、Cyclone V等。

抖动衰减时钟芯片Si5381内部有4个独立DSPLL,其中DSPLLB的结构不同于其它的三个DSPLL,请简述各个DSPLL的具体作用?

Si5381内部自带4个独立的DSPLL,其中专门为实现无线基站设备时钟配置的锁相环是DSPLLB,DSPLLB的输出范围最高可达1.47456 GHz,环路带宽范围是10 Hz ~ 100 Hz,支持高速接口JESD204B的DCLK 和 SYSREF时钟处理。其它DSPLLA/C/D可以作为普通时钟发生器DSPLL使用,其输出范围和带宽范围相对DSPLLB要窄,可以作为普通本地总线、交换芯片等设备的参考钟使用。

【产品】四路独立DSPLL超低抖动衰减器,简化设计复杂度

针对Si5347-B版本实际应用过程中碰到的Bug和客户提出的应用需求,Silicon Labs最新推出了一款可用于在8kHz~750MHz输入时钟抖动衰减时钟发生器Si5347-D,其实用的可编程延时调节、精准的缓变率调节及可配置的自由振荡模式等功能大大简化了系统设计的复杂度。

Si5334引脚控制任意频率、任意输出四路时钟发生器

描述- Si5334是一款高性能、低抖动的时钟发生器,能够在四个差分输出时钟上合成任意频率。该设备接受外部参考时钟或晶体,并生成四个差分时钟输出,每个输出均可独立配置,频率范围高达350 MHz,并支持特定频率至710 MHz。Si5334采用Silicon Labs的专利MultiSynth技术,每个输出时钟具有非常低的抖动和零ppm频率误差。设备支持多种信号格式和参考电压,适用于多种应用,如以太网交换机、PCI Express、处理器和FPGA时钟等。

电子商城

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥8.1764

现货: 102,628

品牌:SILICON LABS

品类:Mighty Gecko Multi-Protocol Wireless SoC

价格:¥27.0929

现货: 90,767

现货市场

品牌:SKYWORKS

品类:HIGH-FREQUENCY, ULTRA-LOW JITTER ATTENUATOR CLOCK WITH DIGITALLY-CONTROLLED OSCILLATOR

价格:¥365.2522

现货:173

品牌:SILICON LABS

品类:Switch Hall Effect Magnetic Position Sensor

价格:¥2.2924

现货:126,000

服务

提供语音芯片、MP3芯片、录音芯片、音频蓝牙芯片等IC定制,语音时长:40秒~3小时(外挂flash),可以外挂TF卡或U盘扩容。

最小起订量: 1pcs 提交需求>

提供蓝牙BLE芯片协议、蓝牙模块、蓝牙成品测试认证服务;测试内容分Host主机层,Controller控制器层,Profile应用层测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

正在努力加载……

正在努力加载……

登录 | 立即注册

提交评论