想提高网络数据中心的速率?非要频率灵活时钟发生器不可!

消费移动装置如:Netflix、Hulu、YouTube、Spotify、Pandora等在线游戏的云串流服务使网络带宽的需求暴增,并带动了网络基础设施供应商纷纷开发数据中心系统来支持大幅提升的数据速率,像是10G、40G和100Gbps。另外,提供网络型运算和存储服务的商用云计算日益普及也进一步推升了现今的数据中心对于应用灵活、高带宽网络的需求。

为了适应这些要求,高速网络和数据中心设备必须要具备频率灵活性的时钟发生器IC解决方案来支持更快的数据速率。因此,SiliconLabs计时产品资深营销经理PhilCallahan特别撰文说明如何协助设计人员打造高弹性、高带宽的互联网基础设施设备,并介绍一款具备高效能、频率弹性的Si5341/40时钟发生器,该元件能产生任何频率,并达到绝佳的抖动性能(在整数模式中不到100 fs RMS,在小数合成模式中不到150 fs RMS),将成为未来高速网路和数据中心不可或缺的关键设计元素。

基于云的Apps带动综合式数据中心网络对于频率灵活时钟发生器的需求

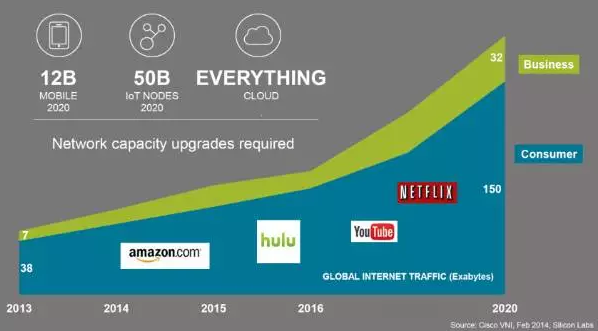

消费移动装置如:Netflix、Hulu、YouTube、Spotify、Pandora等在线游戏的云串流服务使网络带宽的需求暴增,并带动了网络基础设施供应商纷纷开发数据中心系统来支持大幅提升的数据速率,像是10G、40G和100Gbps。另外,提供网络型运算和存储服务的商用云计算日益普及也进一步推升了现今的数据中心对于应用灵活、高带宽网络的需求。图1是说明这些普及基于云串流服务对于互联网流量带宽成长的影响。

Cisco的VisualNetworking Index (VNI) Forecast(2014年6月)预估了以下的市场趋势:

• 到2018年时,Netflix、YouTube、Pandora和Spotify等云应用与服务将占移动数据总流量的九成。

• 2018年的全球网络流量将比2013年大上三倍,相当于每个月33B DVDs,或每小时46M DVDs的流量。

到2018年时,消费在线游戏的流量将比2013年大上四倍。

图1:Cisco VNI,2014年6月

基于云的应用带动数据中心的网络统合

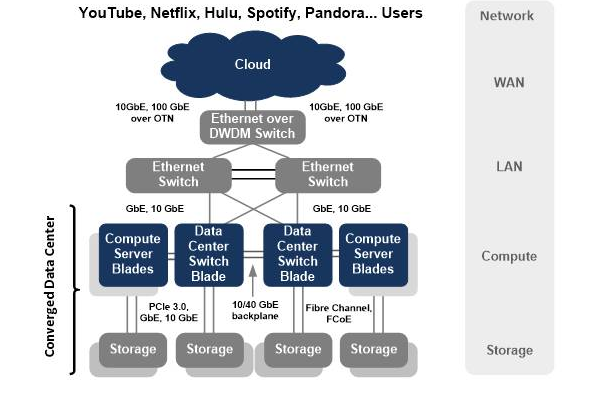

如果要稳定播放Netflix的视频或Spotify的高质量音频串流,服务供应商就必须布建数据中心的硬件来支持三个主要的网络,如图2所示。

• LAN/WAN网络通常是包含1 Gb、10 Gb和/或100 Gb的以太网交换机连接数据中心LAN的网状交换结构,以及光传输网络(OpticalTransport Networking)与WAN的互连。这些网络是将数据中心的内容传到云,最终传给用户。

• 运算网络包含许多以电缆互连的服务器和交换机“刀片(blade)”、PCB背板或光链路。这些互连合并使用了1 Gb、10 Gb的以太网、PCIe,在某些情况则是InfiniBand。运算网络中的网络接口不但必须支持高速率的数据,还必须支持非常低的延迟,这点对于串流视频和音频服务的质量至关重要。

存储网络主要是采用光纤信道、Gb或10Gb以太网交换器,以及利用PCIe来直接链接的存储子系统。这些网络所存储的内容相当大量,所以需要可应付高速的协议。

图2:数据中心网络图

为了满足内容提供商对于互联网带宽迅速扩展的需求,数据中心的运算和存储网络必须变得较为扁平,并加强横向互连。这种较为扁平的架构就是所谓的“综合式数据中心”,数据中心内的服务器对服务器以及服务器对存储通讯都必须靠它来改善,并且会直接影响到延迟与串流服务的质量。除了具有延迟效能上的优点,综合式数据中心的架构也有很高的扩展性,能从事运算服务器和存储硬件资源的软件虚拟化,以支持服务带宽瞬息万变的需求。有些厂商把这个架构称为软件定义网络(SDN)。

传统的时钟树设计对综合式数据中心来说太过复杂

随着数据中心的运算和存储网络与高速的以太网、光纤信道以及嵌入式可插式高密度板卡的横向互连PCIe链路,这对系统工程师也产生了新的要求,尤其是时钟树的设计人员。设计人员必须找到时钟树的解决方案,同时支持高带宽网络协议日益提高的功能密度与广度,并缩减PCB的尺寸、功耗与成本。

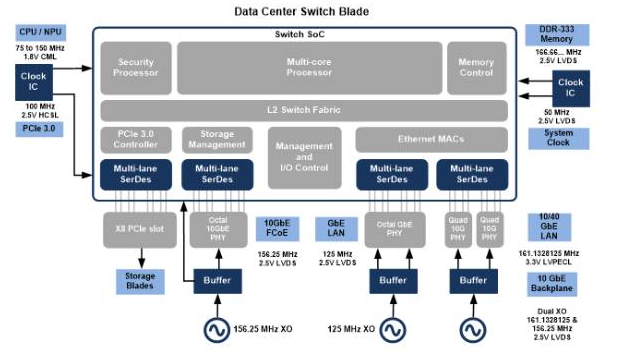

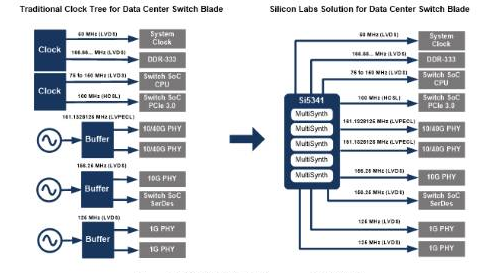

我们以传统的时钟树设计法来考虑数据中心交换器板卡,如图3所示。无论这个板卡是用多个IC安装在PCB上,还是以系统单芯片(SoC)解决方案为主,运算交换器板卡的主要功能都是支持LAN、运算服务器板卡和存储装置之间的同步、高带宽、低延迟通讯。数据中心交换器板卡是在支持把高速的LAN与多协议的存储流量整并到扩充性很高的网络中。不过,用来支持数据中心交换器板卡的传统时钟树很复杂(参见图3),需要八个时钟树的组件:

• 三个晶体振荡器(XO)

• 三个缓冲器IC

• 两个时钟发生器IC

图3:采用传统时钟树的中心切换方案

多线道SerDes与PHY参考频率

时钟树很复杂的主要原因在于,高速通讯链路基本上是依赖每种网络接口的多线道、高速的串行器/解串器(SerDes)和物理层装置(PHY)。SerDes芯片和PHY是数据中心交换器板卡至关重要的基本组件。依照网络类型(LAN/WAN、运算、存储)、协议(GbE、10 GbE、光纤信道、PCIe)以及传输媒介(光纤线缆、铜线或PCB背板),每个高速的SerDes或PHY装置都需要低抖动参考频率,而且有很多的运转频率并不相同。

由于协议和实体媒介的标准不同,这些参考频率鲜少是整数相关。例如161.1328125MHz的频率跟156.25 MHz的频率就是小数相关(66/64)。这种小数关系使得低抖动SerDes频率很难同步产生,因为必须用到小数分频器。比起只有整数的PLL时钟发生器所使用的整数分频器,传统的时钟发生器所使用的小数分频器产生的抖动要大得多,使设计人员不得不采用比较昂贵与专用的晶体振荡器来生成每一个独特的频率。

CPU、存储器与系统时钟

有些IC对于抖动的要求可能非常严格(像是SerDes和PHY),有些切换器板卡功能的要求则比较宽松(100 MHz的PCIe、75到150 MHz的可变式CPU,以及166.66 MHz的DDR-333存储器时钟)。不过,由于传统解决方案的灵活性和集成度有限,时钟树的设计人员不得不使用多个时钟发生器、晶体振荡器(XO)和缓冲器来完成时钟树。

因此,为了满足数据中心交换器板卡在提高网络接端口密度与带宽上有增无减的需求,时钟树的设计人员所需要的时钟发生器应该要有:

• 多个低相位抖动SerDes和PHY参考时钟完全符合网络(1/10/100G的以太网)、存储(光纤信道、PCIe)和运算(PCIe、Infiniband)的主流标准对于抖动性能所要求的严格规格。一般来说,抖动的规格从1 ps RMS左右到低于300 fs RMS(12 k到20 MHz)不等。

• 频率灵活性,一面同步产生范围广泛的整数和小数相关时钟频率,同时固守网络、运算和存储以及频率抖动的严谨规格。在运转中改变频率而不影响其他输出的能力也大有用处。比方说,这能让以速度来分级的CPU满足不同的产品成本与市场需求。

• 最高度的集成,以大幅缩减PCB的面积、成本和组件数量,并尽量提高系统的端口密度与每位成本。

为综合式数据中心设计时钟树的新做法

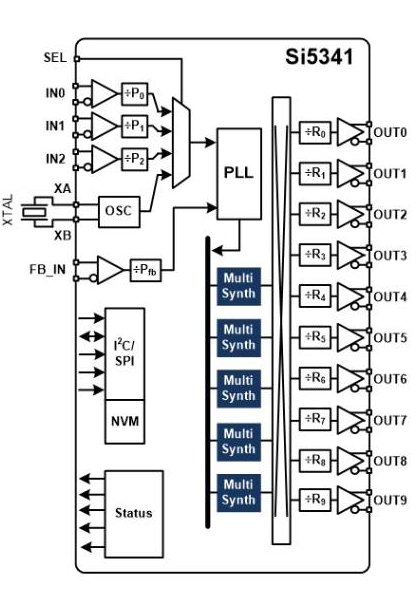

相对于传统的时钟发生器,像SiliconLabs的Si5341/40时钟家族这种新一代的时钟解决方案充分运用了小数与整数频率合成的灵活性,集成度也比较高。这种架构性的做法提供了有效率、省钱、单芯片的解决方案来把所有个别的计时功能整合到单一的IC,又不用牺牲抖动的性能。Si5341时钟之所以能对任何的输出同步产生任何达800 MHz的整数或小数频率,而且一般的抖动都小于150 fs,关键就在于SiliconLabs独家的MultiSynth小数分频技术。

如图4中所示,Si5341时钟是用单一的低功耗压控振荡器来驱动五个独立的MultiSynth小数分频器,并通过非阻塞的交点式交换器连结到有10路频率输出的数组上。在这个架构的第一阶段,MultiSynth高速小数-N分频器会在两个最近的整数分频器数值之间无缝切换,以产生精确的时钟频率,频率合成误差则是0 ppm。为了消除这个过程所产生的相位误差,MultiSynth会计算小数-N分频器所产生的频率以及所要的产出频率之间的相对相位差,并动态调整相位,以符合理想的频率波形。这种新颖的做法使任何产出的频率频率从1 kHz到800 MHz都能产生出来,而且误差为0 ppm。在整数模式中,结果是相位抖动效能优于100 fs RMS,在合成模式中则是不到150 fs,所以小数与整数相关频率都能同步产生。

图4:Si5341功能框图

频率灵活使数据中心交换机刀片的时钟树设计改头换面

利用具频率灵活性、超低抖动、10路输出的Si5341时钟发生器,开发人员就能把数据中心交换机刀片的时钟树从八个个别的组件缩减到只剩下一个高效能时钟。

图5:Si5341时钟发生器内部图

基于云的串流服务将推高需求更高的数据速率。为了适应这些要求,高速网络和数据中心设备必须要具备频率灵活性的时钟发生器IC解决方案来支持更快的数据速率。高效能、具频率弹性的Si5341/40时钟发生器能产生任何频率,并达到绝佳的抖动性能(在整数模式中不到100 fs RMS,在小数合成模式中不到150 fs RMS)。数据中心时钟树的设计人员在为综合式数据中心建造高弹性、高带宽的互联网基础设施设备时,可充分运用这些新的频率产品和SILICON LABS的ClockBuilderPro软件,以便把所需要的计时组件材料列表和复杂度降到最低。

- |

- +1 赞 0

- 收藏

- 评论 0

本网站所有内容禁止转载,否则追究法律责任!

相关推荐

【应用】10路差分输出!DSP时钟电路中少不了这款时钟发生器

SI5341最大能支持10路差分输出,低抖动,完全满足DSP所需的时钟性能需求。

【应用】支持任意频率/输出的时钟发生器,减少通信EMI辐射

为防止高速通信系统EMI辐射过大,工程师通常采用时钟扩频(SSC)技术来减少EMI的产生。Silicon Labs公司的一款基于SSC的时钟发生器Si5338支持任意频率和任意输出,大大减少了、EMI辐射。

【应用】新一代“片上时钟树”产品,提供最佳时钟树方案

Si534x抖动衰减器和时钟发生器,在单芯片时钟IC中集成了所有分立时钟器件功能。

【经验】如何实现SI534X/SI538X时钟发生器SPI在线编程?

Silicon Labs SI534X、SI538X时钟发生器包括基于模拟PLL的SI5340、SI5341和基于DSPLL技术的SI5342、SI5344 、SI5345、SI5342H、SI5344H、SI5346、SI5347、SI5348以及无线专用时钟SI5380、SI5382、SI5386等时钟芯片产品。目前在光通信、数据中心、服务器、小基站、光模块等产品中有广泛的应用

Silicon Labs(芯科科技) Si5351A/B/C-B可编程时钟发生器数据手册

Si5351是一款基于I2C的可编程时钟发生器,适用于替代晶体、晶振、VCXO、PLL和缓冲器。它具有高精度频率合成能力,可生成高达200 MHz的非整数相关频率,并提供多种输出选项和配置功能。

SILICON LABS - I²C可编程任意频率CMOS时钟发生器+VCXO,晶体及时钟芯片,评估板,I²C-PROGRAMMABLE ANY-FREQUENCY CMOS CLOCK GENERATOR + VCXO,EVALUATION BOARDS,SI5351A,SI5351B,SI5351A-B-GTR,SI5351C,SI5351B-B-GM,SI5351A-A-GT,SI5351C-A-GM,SI535X-TMSTK,SI5351C-B-GM,SI5351B-B02073-GM,SI5351X-BXXXXX-XXX,SI5351B-BXXXXX-GM,SI535X-B20QFN-EVB,SI5351C-B-GMR,SI5351A-B-GM,SI5351A-B-GT,SI5351-B,SI5351,SI5351A-BXXXXX-GM,SI5351A-B-GM,SI5351C-B,SI5351A-B,SI5351B-B-GMR,SI5351B-B,SI5351A-B-GT,SI5351A-BXXXXX-GT,SI5351C-BXXXXX-GM,室内照明,AUDIO/VIDEO EQUIPMENT, GAMING,住宅大门,手机相关,音频/视频设备、游戏,高清电视、DVD/蓝光、机顶盒,HDTV, DVD/BLU-RAY, SET-TOP BOX,电脑外设,智能家居,SERVERS, STORAGE,玩具,HANDHELD INSTRUMENTATION,服务器,存储,个人代步工具,便携数码,消费电子部件,通信设备,PRINTERS, SCANNERS, PROJECTORS,网络/通信,电脑,工业电子,打印机、扫描仪、投影仪,个人娱乐,手持仪器,XO REPLACEMENT,可穿戴设备,RESIDENTIAL GATEWAYS,NETWORKING/COMMUNICATION,XO替换

时钟发生器技术方案介绍

时钟发生器是一种关键的电子器件,其主要功能是产生稳定且精确的时钟信号。在数字电路系统中,时钟发生器确保各个组件能够同步运作,从而保证数据的准确处理和传输。无论是在计算机芯片、数字通信设备还是嵌入式系统中,时钟发生器均扮演着不可或缺的角色。

【经验】新型时钟发生器SI5332的多个用户GPIO接口设置用例

SI5332是Silicon Labs推出的一款新型时钟发生器芯片,是一款用于电信传输网、政企网、基站、数据中心、消费电子等多行业通用的时钟芯片。这款时钟发生器芯片是比较成功的,SI5332拥有超低的jitter性能指标(RMS JITTER 230 fs)、可输出路数多(多达12路)、支持任意频点输出、采用模拟环(上电初始化时间快)、可内置多组频率计划等特点,获得了市场及大部分工程师的认可。SI

【应用】可编程任意频率时钟发生器Si5332简化了板级FPGA设计

Silicon Labs推出的Si5332任意频率的时钟发生器提供最高级别的集成,实现在 10/25/100G 数据中心、通信和工业应用程序中的完整时钟树整合。本文介绍了可编程时钟在FPGA设计中的应用

时钟发生器款型多,如何轻松选出理想款?

时钟发生器是电子系统中的核心组件之一,通过内置的锁相环(PLL)和分频器,基于已知的本地参考时钟,生成满足应用需求的精准时钟信号。面对琳琅满目的时钟发生器,如何才能准确、快速地选出一款适合自己产品需求的时钟发生器呢?

【经验】时钟发生器SI5338的LVDS匹配问题的分析测试案例

SI5338是Silicon Labs推出的一款经典的时钟发生器芯片,是一款目前广泛用于通信基站、传输网、政企网、数据中心、消费电子等多行业通用的时钟芯片。日常使用偶尔会碰到较多SI5338的应用问题,有寄存器配置的,也有输出匹配不一致的,对于寄存器问题,一般配合寄存器列表,可以简单较为容易的解决,对于匹配问题,也是SI5338时钟输出的重点关注部分,日前就有工程师碰到了一起LVDS输出匹配问题。

深入探讨时钟发生器的工作原理

在科技的世界中,时钟发生器是一种常见的电子设备,它以精确的方式计时并产生稳定的脉冲信号。本文赛思将深入探讨时钟发生器的工作原理。

时钟发生器Si5351的版本B和版本A有什么变化,推荐使用哪个版本?

时钟发生器Si5351目前主推版本B,版本B和版本A的主要变化有:(1)RevB:频率输出范围是2.5 kHz到200 MHz;RevA:8 kHz 到160 MHz。(2)输出阻抗RevB是50欧姆,RevA是85欧姆。(3)RevB不支持24-QSOP封装。

【经验】如何利用时钟发生器free run模式规避通信系统输入频偏过大

Silicon Labs SI534X时钟发生器使用时往往运行于free run模式,可以规避这种系统上电输入不稳定(频偏过大)的现象。

【经验】时钟发生器Si5332接地PAD引起的频率计划烧录失败问题及解决方式

Si5332支持多个输出端,每个输出端有独立的输出电压,使用ClockBuilder Pro可以快速轻松地配置频率计划,并且有专门的烧录器可通过I²C接口烧录到芯片内的NVM,但是有时候接地PAD引起的频率计划烧录失败,本文将简要分析。

时钟发生器Si5351的I2C工作正常,但是PLLA的时钟倍频不上去不能正常输出148.5M的时钟,请问是什么原因?

Si5351是一款I2C可配置时钟发生器,基于MultiSynth分数分频器的结构,可以以0 ppm误差输出任意高达200MHz的时钟频率。Si5351的时钟配置过程需要按流程进行,配置频率修改寄存器后必须配置初始化寄存器(软复位),该问题原因是修改频率配置寄存器后没有继续配置软复位寄存器。

电子商城

现货市场

品牌:SKYWORKS

品类:HIGH-FREQUENCY, ULTRA-LOW JITTER ATTENUATOR CLOCK WITH DIGITALLY-CONTROLLED OSCILLATOR

价格:¥365.2522

现货:173

服务

提供蓝牙BLE芯片协议、蓝牙模块、蓝牙成品测试认证服务;测试内容分Host主机层,Controller控制器层,Profile应用层测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

提供电机的输出反电势波形测试、驱动芯片输入/输出波形测试服务,帮助您根据具体应用场景来选择适合的电机驱动芯片型号,确保电机驱动芯片能够与其他系统组件协同工作达到最佳效果。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 成都 提交需求>

登录 | 立即注册

提交评论