【选型】支持8-50MHz晶体输入的Au5411A-QMR时钟buffer用于通信管理机,可简化电路节约PCB板空间

电源、时钟、复位时硬件电路三大核心电路,具有举足轻重的地位,对于产品的正常工作非常重要,本文主要介绍奥拉电子时钟Buffer在一款通信管理机中的应用。

本系统需要6组PCIE2.0时钟,故需要选取时钟Buffer进行一驱多应用,这样可以简化电路,节约PCB板空间,提高系统可靠性。

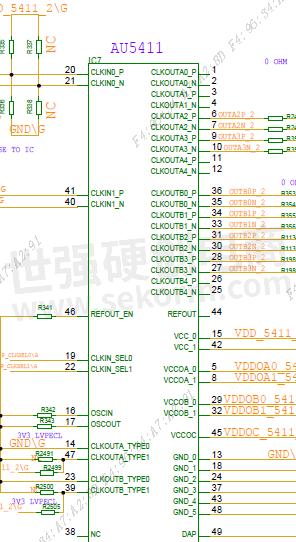

图1 Au5411A-QMR电路原理图

此芯片具有两路输入CLK0、CLK1,支持LVPECL、LVDS、LVCMOS等多种电平输入,同时支持8-50MHz的晶体输入(OSCIN,OSCOUT),支持10路LVPECL、LVDS、HCSL等多种电平输出。

下面主要选取了几家时钟Buffer,针对货期、主要参数、价格、生命周期进行了比对,最终选取了奥拉的Au5411A-QMR,图2为几家时钟Buffer的选型比对表。

图2 时钟Buffer的选型比对表

在目前价格和交货周期良好状态下,Au5411A-QMR时钟Buffer在VCC内核电压和VCCO输出电压方面也较有优势,Au5411A-QMR支持电压种类更多,工程师使用起来更加灵活,可以支持更多的应用。

图3 Au5411A-QMR实物图

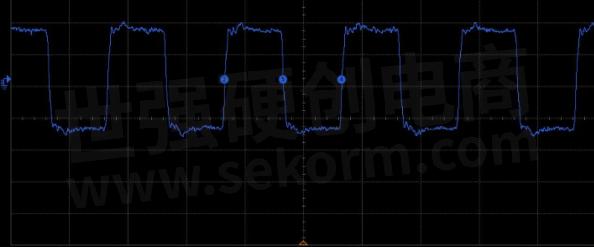

通过验证,Au5411A-QMR在实际验证中均能够满足测试要求,各方面性能都非常不错,PCIE时钟输出波形图如图4所示。

图4 PCIE2.0时钟输出波形

在研发过程中在选取时钟Buffer需要注意:

1. 时钟buffer具有单端和差分输出之分,输入和输出频率、电平、路数都不一样,选型是需要特别注意;

2. 时钟buffer电平匹配非常重要,和应用电路对接时需要特别注意;

3. 时钟buffer抖动参数也特别重要,需要满足应用电路要求;

4. 奥拉的Au5411A-QMR具有价格便宜,交期短,产品一致性好,符合Rohs认证,支持多种供电电压,满足产品设计要求,非常值得选择。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由drwyh提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【选型】奥拉时钟驱动器AU5426A-QMR用于光端机,支持4路差分输出和1路单端输出

某用户在研制光端机时需求时钟buffer,要求低抖动,最好是国产的,推荐奥拉的时钟驱动器AU5426,它是一款支持4路差分输出和1路LVCMOS输出的超低抖动时钟和扇出缓冲器,该缓冲器可以选择来自主时钟、次时钟或晶振的时钟输入。

【选型】国产时钟Buffer AU5425A可P2P兼容LMK00105,参数满足应用需求

为提供低延迟、低抖动的时钟扇出,时钟Buffer广泛应用于在以太网、5G小基站等通信设备上,来提供时钟分配功能。下面是奥拉AU5425A与TI LMK00105参数对比,两者参数基本一致,可互相兼容。

【选型】奥拉超低附加抖动Au5424时钟buffer,附加抖动低至50fs,适用于高速信号传输系统

奥拉Au5424是非PLL的超低抖动时钟buffer,抖动低至50fs,将一路单端LVCOMS信号频率复制实现4路频率输出,1个芯片即可为电路上的多个器件提供时钟源信号。广泛应用于基站、服务器等通信设备上。

奥拉(Aurasemi)时钟和电源管理产品选型指南

目录- 公司简介 Timing BU Introduction VRM LDO & BuckBoost

型号- AU4562,AU5424,AU5425,AU5426,AU5327BC1-QMR,AU5325BC1-QMR,AU5620,AU5508,AU560X,AU5315AC0-QMR,AU5328,AU532X,AU8010AA-QNR,AU5329,AU8014EB-QNR,AU5329B-QMR,AU8310A0-WMR,AU5325BC2-QMR,AU5411A-QMR,AU5327BC2-QMR,AU8014EA-QNR,AU8013EB-QNR,AU4531,AU5X82,AU8941,AUXXXX,AU5410,AU5411,AU571X,AU531X,AU5615,AU5424G,AU5617,AU5317AC0-QMR,AU5424A,AU5410A-QMR,AU8014A,AU8013EA-QNR,AU8012AA-QNR,AU5X8,AU8011CA-QNR,AU4592

AU5411 – 10 路输出、差分信号、超低抖动时钟缓冲器

描述- AU5411是一款高性能的10路输出、差分信号、超低抖动时钟缓冲器,适用于高速数字系统中的时钟分配和电平转换。它具备3:1输入时钟选择,支持多种输出驱动模式和电源电压选项,并提供详细的电气特性和应用信息。

型号- AU5411,AU5411A-QMR,AU5411A-EVB,AU5411A-QMT

AU5424G:1.8 V至3.3 V高性能LVCMOS时钟缓冲器输出,超低抖动缓冲器

描述- AU5424G是一款高性能LVCMOS时钟缓冲器,具有极低的附加相位抖动(50 fs RMS),支持同步无毛刺输出使能功能。该器件可在1.8 V至3.3 V的电压下工作,适用于高速通信设备和服务器等领域。

型号- AU5424BG-DNR,AU5424G,AU5424BG-DMR,AU5424BG-EVB

AU5410–10输出、LVCMOS、超低抖动缓冲器

描述- Au5410是一款低抖动时钟缓冲器,具有10个输出端口,适用于低抖动、高频时钟和数据分配。该器件采用LVCMOS输出,设计用于驱动50欧姆串联或并联终止传输线。它可以从主、辅或晶振源中选择时钟输入,并支持多种输入波形和频率范围。

型号- AU5410A-QMR,AU5410,AU5410A-QMT,AU5410-A-EVB

AU5424A1:高性能1:4 LVCMOS时钟缓冲器

描述- AU5424A1是一款高性能的1:4 LVCMOS时钟缓冲器,具有低相位抖动和低偏移特性。它支持同步无毛刺输出使能功能,可在1.8V至3.3V的电压下工作,适用于汽车级应用。

型号- AU5424A1,AU5424BA1-DAR,AU5424A1-EVB

奥拉半导体产品选型表

供电电压频率(≤250MHz),相位噪声(<50fs),输入/输出,封装类型,输出频率范围(0.5 Hz-2.94912 GHz),输出电流(A),频率,输出精度,静态电流,噪音,压降,电源抑制比

|

产品型号

|

品类

|

供电电压(MHz)

|

相位噪声(fs)

|

输入/输出

|

封装类型

|

|

AU5424BG-DNR

|

时钟驱动器

|

≤200MHz

|

<50fs 附加抖动

|

1:4 LVCMOS 缓冲器

|

8-DFN

|

选型表 - 奥拉 立即选型

奥拉时钟产品(Buffer)亚洲第一,<50fs低抖动可编程时钟

高频数字信号的bit周期短,数据传输在确定边沿进行采集,低抖动可避免时钟理想时刻偏移。奥拉的时钟产品(Buffer)亚洲第一,<50fs低抖动可编程时钟。其高性能单端时钟驱动芯片4~10路单端输出buffer, 驱动能力强,<50fs附加抖动,可减少误码。

Aura Timing产品概述

描述- 本资料概述了Aura半导体公司2015年至2022年的定时产品路线图,包括工程样品和量产产品。产品涵盖抖动衰减器、缓冲器、时钟发生器和网络同步器等,具有低抖动、高精度和多种接口特性。资料详细介绍了各产品的关键参数、功能特点和应用领域,以及与竞争对手产品的兼容性。

型号- AU5424,AU5325,AU5425,AU5426,AU5327,AU5327BC1-QMR,AU53X7,AU5325BC1-QMR,AU5315,AU5508,AU5317,AU5508 SERIES,AU5315AC0-QMR,AU5328,AU5329,AU5329B-QMR,AU5325BC2-QMR,AU5411A-QMR,AU5327BC2-QMR,AU53X5,AU5410,AU5411,AU5615,AU5424G,AU5617,AU5317AC0-QMR,AU5424A,AU53X7 SERIES,AU5410A-QMR,AU53X5 SERIES

AU5426:4路差分、1路LVCMOS输出、超低抖动、高性能缓冲器

描述- AU5426是一款高性能缓冲器,具备4个差分输出和1个LVCMOS输出,适用于低抖动、高频时钟和数据分配。该产品具有极低的抖动性能(50 fs RMS),支持PCIe Gen1至Gen5,并可在3.3 V/2.5 V核心电源电压下工作。

型号- AU5426A-QMR,AU5426,AU5426A-EVB

电子商城

登录 | 立即注册

提交评论