【经验】如何设置抖动衰减器Si5344以跟踪频偏变化的输入信号?

抖动衰减器Si5344是SILICON LABS推出的基于第四代DSPLL专利技术的高性能4输入4输出的时钟芯片,目前已经广泛用于各种数据通信产品中,包括OTN线卡、IP_RAN、PTN、承载网等设备中,不仅可以作为去抖时钟芯片也可以作为普通的时钟发生器,功能非常强大,其输出电平格式支持LVPECL、LVDS、LVCMOS、HCSL、CML等多种电平,支持零延迟,能够方便通过GUI软件界面选择配置并导出频率计划相关的寄存器或者C文件,设计方便简洁。Si5344工作在去抖模式时,需要对输入时钟信号的跟踪锁定,这时内部的DSPLL承担起频率合成和消抖的功能。

是否对于任何输入的时钟信号都可以锁定?实际上对于在其额定频率范围内的时钟信号,在满足电气特性的条件前提下,锁定一般都没有问题,但是实际在工程中应用时,会因为特殊的应用而碰到各种输入时钟信号需要Si5344对其锁定跟踪。对于这种特殊时钟输入信号,需要提供Clockuilder Pro软件来进行调整,以免锁相环失锁。

日前有用户反馈输入的时钟信号是一个周期性的频偏变化信号出现失锁,这个输入时钟的输入频偏每隔几毫秒在±几个ppm到零频偏之间周期性变化。Si5344的输入信号频偏容忍度可以达到几十甚至上百 ppm,一般在这个频偏范围内输入时钟变化,Si 344的DSPLL都能正常跟踪,但是这个是在输入信号相对变化缓慢或者与设定的输入值固定频偏的情况下可以正常跟踪,对于这种相对于设定的输入信号周期性的变化频偏输入信号,DSPLL在跟踪时可能会出现失锁,这很正常,因为Clockuilder Pro软件配置的频率计划是根据固定频点输入来配置的,对于突然的频偏变化,DSPLL会根据频偏大小重新跟踪锁定。如果再次跟踪锁定没有完成时,输入频偏再次跳变,那么跟踪锁定可能永远无法完成,这时会导致失锁LOL。

对于这种情况,那么该如何通过Clockuilder Pro配置进行避免失锁呢?通常需要对下述三个选项进行详细配置。

1) 首先是环路带宽设置。对于这种情况,环路带宽不能设置太窄,环路带宽与锁定时间是成反比的,因此在满足抖动需求的情况下应该根据需要适当加大环路带宽。

2) 其次是OOF设置。OOF设置一般不能超过输入变化的频偏值,避免因为OOF告警导致失锁。

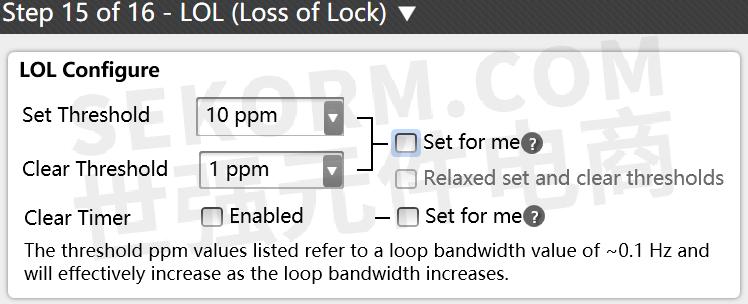

3) 再就是LOL设置。这个步骤设置也是最重要的(如下图1),这里不能简单选择“Set for me”选项,这个是默认选项,是针对固定频点软件Clockuilder Pro做的最优化默认设置,但是对于动态的输入频率(频偏变化),当配置无效时,这里需要手动调整。其次重点设置“Clear Threshold”,这个选项是重新锁定时的解除失锁判决门限。对于输入只有几个ppm输入变化的情况,可以将这个“Clear Threshold”设置不超过输入频偏的门限,进一步避免失锁出现。

图1 LOL设置

注意,上述三个配置选项可能需要重复调整并Debug验证。

- |

- +1 赞 0

- 收藏

- 评论 1

本文由火芯人提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【经验】抖动衰减器Si5345如何匹配选择8K单端输入时钟信号?

Silicon Labs的Si5345的输入时钟最低频率刚好是8kHz信号,通常对于这个最低频率的处理,需要特别注意。很多应用时会直接采用直流耦合的方式进行匹配,但是对于Si5345来说,这个8k不能简单直接使用DC耦合。通常8kHz时钟信号在通信吕一般由两种,一种是正常的占空比40~60%之间的时钟信号,还有一种是占空比远远小于1%的窄脉冲时钟信号,这两种时钟信号的处理实际应用是完全不同的。

如何实现SI5342、SI5344和SI5345抖动衰减器锁相环动态调整?

Silicon Labs的超高性能抖动衰减器SI5342/SI5344/SI5345已经在通信客户中获得大量的应用。Silicon Labs SI5342/SI5344/SI5345时钟发生器内置Silicon Labs第四代专利锁相环DSPLL,自带I2C、SPI可编程接口,能够实现用户在线编程改变输出频率,实现在线调试和频率更新。本文讲述了实现抖动衰减器锁相环动态调整的方法步骤。

【经验】秒懂噪声源时钟树——添加抖动衰减器动机及对时钟树抖动估计的影响探讨

在本单元秒懂时钟系列——噪声源时钟树第1部分案例,Silicon Labs将超越原型或“标准”时钟树。本文将对添加抖动衰减器的动机及其对时钟树抖动估计的影响进行讨论。

【产品】四路独立DSPLL超低抖动衰减器,简化设计复杂度

针对Si5347-B版本实际应用过程中碰到的Bug和客户提出的应用需求,Silicon Labs最新推出了一款可用于在8kHz~750MHz输入时钟抖动衰减时钟发生器Si5347-D,其实用的可编程延时调节、精准的缓变率调节及可配置的自由振荡模式等功能大大简化了系统设计的复杂度。

Silicon Labs(芯科科技) Si5345, Si5344, Si5342系列抖动衰减器/时钟倍频器 参考手册

型号- SI5345A-B-GM,SI5344C-B-GM,SI5345D-B03700-GM,SI5345D-B04500-GM,SI5345B-B04564-GM,SI5344B-B04184-GM,SI5345D-D-GM,SI5345C-A-GM,SI5345B-B-GM,SI5344D-B-GMR,SI5345B-B04881-GM,SI5345D-B04831-GM,SI5344D-B-GM,SI5342D-B05470-GM,SI5345A,SI5345A-B-GMR,SI5345B,SI5345C,SI5345B-B05955-GM,SI5345D,SI5342A-B-GM,SI5345B-B05785-GM,SI5345D-B05731-GM,SI5342D-D-GM,SI5345A-A-GM,SI5345B-B05747-GM,SI5345D-B04501-GM,SI5348B-B05856-GM,SI5342B,SI5342C,SI5342D,SI5342B-B-GM,SI5345D-B04409-GM,SI5348B-B05083-GM,SI5344A-B-GM,SI5345B-B04823-GM,SI5345B-B05971-GM,SI5342C-D-GM,SI5345B-B00021-GM,SI5345B-B06003-GM,SI5348B-B05423-GM,SI5344B-D-GM,SI5342A,SI5345C-D-GM,SI5345B-B-GMR,SI5345D-B04493-GM,SI5345D-B04502-GM,SI5345D-B-GM,SI5345D-B05784-GM,SI5342C-A-GMR,SI5345B-D-GM,SI5345A-D-GM,SI5342A-D-GM,SI5345B-B04421-GM,SI534X,SI5348B-B05017-GM,SI5345A-B04313-GM,SI5345B-B04408-GM,SI5342D-B-GM,SI5345D-B04494-GM,SI5345D-B04528-GM,SI5345C-B-GM,SI5345B-B05825-GM,SI5344D,SI5342B-D-GM,SI5345D-B04834-GM,SI5345B-B04563-GM,SI5342D-B04694-GM,SI5344D-D-GM,SI5345A-B04313-GMR,SI5345A-B04957-GM,SI5344A-D-GM,SI5345D-B04830-GM,SI5345D-B05729-GM,SI5344B-A-GMR,SI5345D-B04410-GM,SI5345A-A-GMR,SI5345B-B03718-GM,SI5342D-B03814-GM,SI5344A,SI5345B-B03234-GM,SI5344B,SI5344C,SI5345B-B05786-GM

Si5369 ANY-FREQUENCY PRECISION CLOCK MULTIPLIER/JITTER ATTENUATOR

型号- SI5369A-C-GQ,SI5369,SI5369D-C-GQ,SI5369C-C-GQ,SI5369B-C-GQ

【应用】互联网基础设施(II)应用时钟设计人员选择Si534x抖动衰减器的三大原因

Silicon Labs的Si534x输出高性能抖动衰减器结合了第四代DSPLL和MultiSynth技术,帮助需要最高抖动性能的应用实现了任意频率时钟发生和抖动衰减。对于时钟树设计人员来说,使互联网基础设施(II)应用更简单、更快和更可靠是具有一定挑战性的。

一文快速告诉你任意频率时钟抖动衰减器Si539x与Si534x的性能对比

Silicon Labs结合第四代DSPLL™和MultiSynth™技术推出了Si539x和Si534x两款任意频率时钟生成抖动衰减器,抖动极低,适用于要求严格的互联网基础设施,可降低各种定时应用的成本和复杂性。本文将重点介绍超高性能Si539x系列较之Si534x系列有了哪些提升。

【技术】Silicon Labs低功耗抖动衰减器的第四代DSPLL技术,可简化时钟设计

Silicon Labs发明了DSPLL®技术,这是一种结合了数字信号处理(DSP)和PLL技术的混合方法,可简化高速互联网基础设施应用所需的时钟倍频和抖动衰减电路。现在已进入第四代,这种先进的专利时序技术现在是用单个集成电路替换多个离散锁相环路PLL元件的最佳解决方案,该集成电路集成了DSP电路和超低抖动时钟或电压控制振荡器。

Si5368 ANY-FREQUENCY PRECISION CLOCK MULTIPLIER/JITTER ATTENUATOR

型号- SI5368C-C-GQ,SI5368,SI5368B-C-GQ,SI5368A-C-GQ

【经验】高性能抖动衰减器时钟芯片Si5326的频率配置问题解析及替代方案推荐

Si5326是Silicon Labs推出的基于第三代DSPLL专利技术的高性能抖动衰减器时钟芯片,最近有工程师在做设计时要求Si5326输入为25MHz时钟,2路输出分别是25.8MHz和27.5MHz的3.3V时钟信号,使用DSPLLsim配置时,发现无论该2路时钟位置如何调换,无论如何调整分频比,输出频点都不能同时实现整个两个频点的输出。本文就将解答这一问题并给出替代方案。

在Silicon Labs抖动衰减器SI5347A-D的DEMO板输入端输入占空比为0.04%的8 kHz极窄脉冲,DEMO板上报有LOS和OOF告警,不能稳定锁定,请问这可能是什么原因?

SI5347A-D支持频率低于1 MHz且占空比少于50%的时钟输入,并能锁定输出。如果不能锁定,可以分析以下原因:;1). SI5347A-D的ClockBuilder Pro软件GUI界面中没有选择pulse mode。;2). DEMO板的默认输入电路以高频差分信号为参考进行设计,在输入端增加了多个电容用于隔离直流,但是对于窄脉冲输入信号,应该按照数据手册要求换掉电容,并增加电阻分压电路。

Si5327 ANY-FREQUENCY PRECISION CLOCK MULTIPLIER/JITTER ATTENUATOR

型号- SI5327-EVB,SI5327D-C-GM,SI5327B-C-GM,SI5327C-C-GM,SI5327

电子商城

现货市场

品牌:SKYWORKS

品类:HIGH-FREQUENCY, ULTRA-LOW JITTER ATTENUATOR CLOCK WITH DIGITALLY-CONTROLLED OSCILLATOR

价格:¥365.2522

现货:173

服务

可来图定制均温板VC尺寸50*50mm~600*600 mm,厚度1mm~10mm,最薄0.3mm。当量导热系数可达10000W/M·K,散热量可达10KW, 功率密度可达50W/cm²。项目单次采购额需满足1万元以上,或年需求5万元以上。

提交需求>

可定制电机的连续转矩范围1Nm至2000Nm,峰值转矩3Nm至5500Nm,电机延长线长度、变换编码器类型。

最小起订量: 1 提交需求>

登录 | 立即注册

提交评论