【经验】如何设计车载音响娱乐系统中DDR3内存的布局布线方案?

型号为AS4C128M16D3LB-12BCN的ALLIANCE DDR3具有800Mhz的时钟速率,信号传输速率非常快、时序要求非常严格,因此它的布局布线好坏关系到了产品的性能,甚至关系到产品能否正常启动和运行。本文笔者将就一个采用了2片AS4C128M16D3LB-12BCN的车载音响娱乐系统项目,分享如何设计AS4C128M16D3LB-12BCN DDR3内存布局布线方案的实践经验,内容包括布局、拓扑选择、布线等。

布局

DDR3与处理器之间距离尽量短,2个DDR的情况下请均放置在同一面以保证去耦电容的合理放置,本项目采用的是2片AS4C128M16D3LB-12BCN,因此2片AS4C128M16D3LB-12BCN放在了同一层,这里是放在了Layer8(第8层)。

DDR3布线拓扑选择

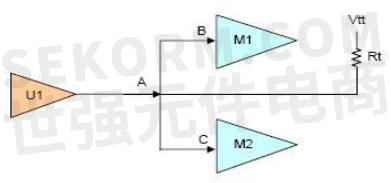

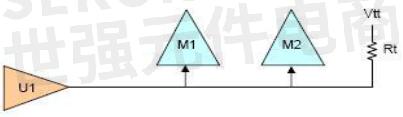

DDR3布线拓扑包括T型(树形)、菊花链、Fly-By,详见图1、图2、图3,图中U1为内存控制器,M1/M2为DDR3芯片,T型主要适用于产品采用2片内存的情况,Fly-By适用于4片或以上DDR3数量的情况,因本项目采用的是2片AS4C128M16D3LB-12BCN,因此采用T型拓扑。

图1 T型(树形)拓扑

图2 菊花链拓扑

图3 Fly-By拓扑

根据上述布局和拓扑分析,本车载音响娱乐系统项目中DDR3 AS4C128M16D3LB-12BCN的布局和拓扑如图4所示:

图4 AS4C128M16D3LB-12BCN的布局和拓扑结构图

布线

AS4C128M16D3LB-12BCN的布线顺序如下:

1. 数据线、时钟线

2. 地址线、控制线、命令线

3. 电源

这种布线方式能使时钟线更容易与其它信号组匹配且兼顾EMI性能。

数据线、时钟线

1. 数据线组包括DQ(数据线)、DQS+/-(数据线时钟基准线)、DQM(数据掩码),每8根DQ、一对DQS和一根DQM组成一个字节,比如DQ【0:7】、DQS0+、DQS0-、DQM0这11根线为第1组数据组,其它走线以此类推,每一字节小组走线大部分须在同一层,执行同样数目的换层过孔、在同样的位置打过孔(因为每层走线的速度不一样,保持每层一样的走线长度有利于保证时序)、同组线等长处理;

2. 因时钟线和数据线信号波形边沿陡峭、变化极快因而辐射量大,因此兼容时序和EMI考虑,把时钟线和各组数据线都放在内层一起走线;

3. 为避免各线之间相互串扰影响信号质量同时兼顾走线密度空间限制,同组数据线内线和线之间的距离应大于2倍自身线宽,各组之间间距大于等于3倍自身线宽,时钟线跟其它线之间的间距应大于3倍自身线宽;

4. 所有走线换参考的地方就近补链接路径(打地孔);

5. 时钟的端接电阻靠DDR3放置;

6. 数据线和时钟线的参考层需是地层。

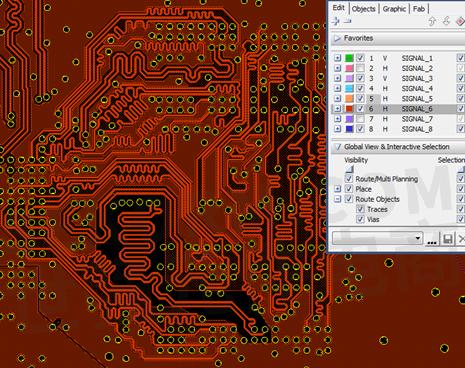

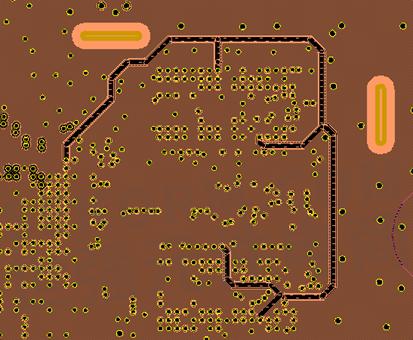

依据上述原则,本项目的数据线、时钟线布线在Layer3(参考层为地层Layer2)和Layer6层(参考层为地层Layer7),详见图5、图6.

图5 AS4C128M16D3LB-12BCN数据线组合时钟线布线图(Layer3)

图6 AS4C128M16D3LB-12BCN数据线组合时钟线布线图(Layer6)

地址线、控制线、命令线

1. 为兼顾PCB板成本,它们大部分在表层布线;

2. 它们跟时钟线等长、走T型拓扑;

3. 每根线阻抗设为50欧姆,线跟线之间距离2倍自身线宽以上以免串扰;

4. 它们跟其它非内存线的距离大于3倍自身线宽。

VDD

VDD是数据、地址、时钟、控制等的供电瞬态电压,特点是电流大、变化快,可见它必须布置成大平面,保证电源平面阻抗比较低(从而不会引起大的电源波动),此案中VDD放在Layer4,优点是一方面它可以很好的充当Layer3内存走线的参考平面,另一方面其相邻层Layer5是Ground层,可以保持电源层的稳定去耦。

图7 AS4C128M16D3LB-12BCN V VDD布线图

VREF

VREF电流需求较小(小于3mA),它是为控制器和DDR3芯片的差分接收器提供VDD/2(VDD为内存数据地址等端口的供电电压)的直流偏置,VREF的误差或噪声可能会在总线上引起时序的错误、不期望的抖动和误动作等,因而其较敏感、 layout要求比较严格,它的纹波必须控制在3%以下,在PCB上布成拉线形式,线尽量短,宽度20mils以上,须远离数字信号,最好其上下左右均有Ground包围,本案中VREF的布线如图8所示,它放在Layer5,周围都是Ground,且其距离Layer6的走线层较远(Layer5和Layer6之间的填充介质较厚),不易受走线的噪声干扰。

图8 AS4C128M16D3LB-12BCN V VREF布线图

- |

- +1 赞 0

- 收藏

- 评论 2

本文由清风提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【技术大神】DDR3,最了解你的人是我!

ALLIANCE公司的DDR3颗粒AS4C256M16D3-12BCN作为商业级DDR3颗粒,工作温度范围可达到0-95摄氏度,最高可支持800MHz时钟速率,适用于LTE小基站等应用领域。

【成功案例】基于Alliance DDR3的T型拓扑、Fly-by 拓扑结构设计方法,成功用于车载音响系统项目

本文从车载音响系统设计项目中介绍,当产品中采用多片DDR3(ALLIANCE AS4C256M16D3B-12BCN为例)时就会涉及到内存传输拓扑结构问题,及如何设计相应的拓扑结构方案才能保证产品低成本、高信号质量且具有良好的时序余量。

【经验】Fly-by拓扑下DDR3的终端匹配电阻设计方案,减少反射、提高信号质量

当汽车电子产品中采用4片或4片以上的AS4C64M16D3-12BIN时,为解决时序和信号完整性问题,DDR3内存的时钟、地址、控制命令线需要采用Fly-by拓扑结构,但也同时需要精心设计相应的终端匹配方案,以减小反射、保证信号质量。解决办法就是在反射最严重的分支上加终端匹配电阻,而最远分支是反射最严重的地方,因此在最远分支末端加上终端匹配电阻吸收反射来提高信号完整性是既经济又折中的方案。

ALLIANCE 存储器选型表

提供存储器、存储芯片、SRAM、SDRAM、DDR1、DDR2、DDR3、DDR4选型,VCC(V):0.6-5,MSL LEVEL:0-5,CLOCK(MHz):133-1866,可支持商业级/工业级/汽车级。

|

产品型号

|

品类

|

Product Family

|

DENSITY

|

ORGANISATION

|

VCC(V)

|

TEMPERATURE RANGE(°C)

|

PACKAGE

|

MSL LEVEL

|

|

AS7C164A-15JCN

|

存储器

|

FAST-Asynch

|

64K Fast

|

8K x 8

|

5V

|

Commercial (0 ~ 70°C)

|

28pin SOJ(300mil)

|

3

|

选型表 - ALLIANCE 立即选型

AS4C1G8D4A-62BCN / AS4C1G8D4A-62BIN ALLIANCE MEMORY MDS REPORT

型号- AS4C1G8D4A-62BIN,AS4C1G8D4A-62BCN

国产的DDR3或DDR4有没有8Gb或者16Gb的,请给个厂家和具体型号?

目前世强代理的国产品牌ATP,有DDR3内存条,但不是存储芯片,存储芯片,ALLIANCE这边有,DDR3,1.5V的只有4G的,如AS4C256M16D3B-12BCN;DDR3L,1.35V的有8G的如:AS4C512M16D3L-12BxN,AS4C1G8MD3L-12BCN。

【产品】96 ball FBGA封装的512M DDR3——AS4C32M16D3L

Alliance的512M DDR3——AS4C32M16D3L ,采用96 ball FBGA封装,该芯片采用双倍数据速率架构,可实现高速运行。Alliance的这款512MB DDR3可实现高达1600 MB/sec/pin的高速双数据传输速率,可满足常规应用。

AS4C512M16D4A-62BCN / AS4C512M16D4A-62BIN ALLIANCE MEMORY MDS REPORT

型号- AS4C512M16D4A-62BIN,AS4C512M16D4A-62BCN

AS4C256M16D3LC 256M x 16 bit DDR3L Synchronous DRAM (SDRAM)

型号- AS4C256M16D3LC-10BAN,AS4C256M16D3LC-12BANXX,AS4C256M16D3LC,AS4C256M16D3LC-10BANXX,AS4C256M16D3LC-12BAN

Alliance是否有MT41K256M16TW-107P的代替型号pin-to-pin,ddr3l

Alliance的DDR3 AS4C256M16D3L-12BxN 是pin-to-pin的。

Alliance Memory Expanded Lineup of DDR3 and DDR3L SDRAMs With 512Mb x8 and x16 Devices in 78-Ball and 96-Ball FBGA Packages

Alliance Memory announced that it has expanded the industry’s widest offering of high-speed CMOS DDR3 and low-voltage DDR3L SDRAMs with new 512Mb x8 and x16 devices in the 78-ball and 96-ball FBGA packages, respectively.

【产品】8Gbit双倍数据速率DDR3L同步DRAM(SDRAM)AS4C1G8D3LA,78-ball FPGA封装

Alliance Memory推出了一款结构为128M words x 8 bits x 8 banks、双倍数据速率(DDR3L)同步DRAM(SDRAM)AS4C1G8D3LA。采用双倍数据速率架构,每个时钟周期可传输两次数据,8位预流水线结构可实现高速数据传输。

AS4C256M8D3LC 256M x 8 bit DDR3L Synchronous DRAM (SDRAM)

型号- AS4C256M8D3LC,AS4C256M8D3LC-12BIN,AS4C256M8D3LC-12BC/INXX,AS4C256M8D3LC-12BCN

Alliance Memory Introduced Die Version for 2Gb and 4Gb DDR3 and DDR3L SDRAMs Providing New Memory Chip Source in Face of Market Shortages

To address the memory market’s shortage of high-speed CMOS DDR3 and low-voltage DDR3L SDRAMs, Alliance Memory announced a new die revision (B die) for its 2Gb and 4Gb devices in the 96-ball FBGA package.

电子商城

现货市场

登录 | 立即注册

提交评论