【经验】奥拉低抖动时钟buffer Au5411同差分时钟格式输出的实现方式

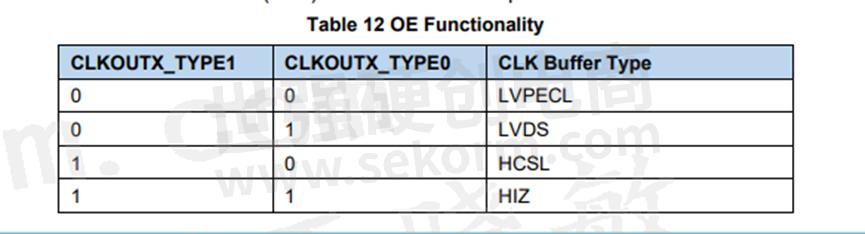

奥拉低抖动时钟buffer Au5411可支持10路差分时钟输出,包括LVPECL, LVDS, HCSL or HIZ 等格式、超低附加抖动55fs RMS,可广泛应用于基站、服务器等场景中。下面将介绍不同差分格式输出的实现方式。

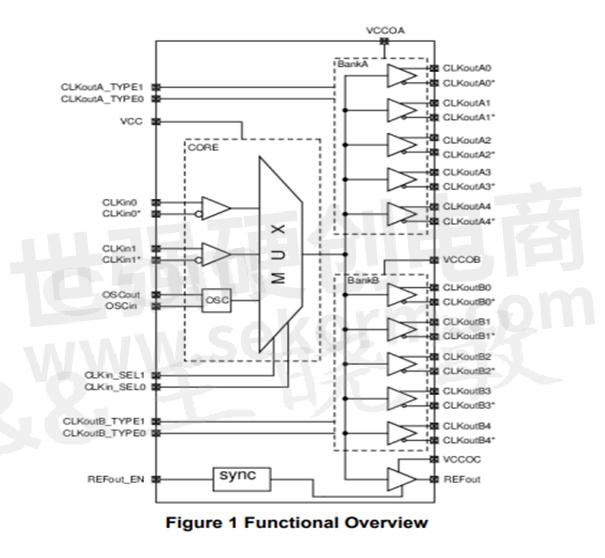

时钟buffer可对输入时钟进行复制,输出多路的时钟,供后端器件提供频率源,Au5411有两个bank,可通过CLKOUT_TYPE,将如输入时钟格式变换、满足后端器件对不同格式电平的需求。

Au5411可支持频率复制、格式转换,适用于需多频率时钟源场景中,使用于基站、服务器等场景中。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由王晓敏提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【经验】如何选择奥拉时钟buffer Au5426的输入源以降低开发难度?

奥拉Au5426是一款可支持4路差分输出和1路单端输出的超低抖动时钟buffer,附加抖动为50fs,可支持1路XO输入及两路CLKin输入,应该如何选择输入源才能更好的体现芯片的性能,减少开发难度?本文给您答案。

服务器散热风扇的噪音大解决方案

服务器散热风扇的噪音大,是一个常见的问题。服务器散热风扇在保障服务器正常运行和散热的同时,也会产生一定的噪音。如果噪音过大,可以参考以下点进行排查:风扇设计问题、风扇积尘、风扇老化或损坏、温度过高、机柜固定问题。

【经验】关于奥拉Au5508时钟抖动衰减器判断时钟输出相位锁定的方式

在基站应用中,通常来自GPS模块的1pps信号作为时钟源,再经过时钟发生器实现时钟分频输出,并且相位同步,本文将介绍Au5508如何判断输出相位锁定的方式。以上1pps输入,输出1HZ需要跟输入相位保持同步。

【技术】解析时钟Buffer芯片及关键参数

时钟芯片是高性能通讯系统中必不可少的核心芯片,其性能及可靠性直接影响着通讯系统的主要性能和系统稳定性。本文中电科星拓将为大家详细讲解下时钟Buffer的分类和关键参数等。

研讨会2024时钟及晶振新技术研讨会

12月19日在线直播,带来超高精度恒温晶振、超低功耗时钟发生器、车规认证RTC、低抖动高频差分晶振、低功耗实时时钟模块等最前沿的新技术新产品

PurusMicro(华时嘉库)超低抖动DSP时钟选型指南

描述- 华时嘉库的核心团队在时钟行业拥有超过20年的管理经验,团队成员具备丰富的模拟、射频和复杂数模混合设计能力。团队致力于持续创新,并与客户紧密合作,以确保解决方案能够满足不断演变的市场需求。

型号- PM5386,PM5440,PM51012,PM53358,PM5344,PM2111H,PM5101,PM50841,PM2111,PM5345,PM50204,PMD2000,PM19024,PM53350,PM19004,PM53012,PM19020,PM53354,PM5361,PM53352,PM19008,PM28130,PM51002,PM3352,PM5112,PM53328,PM50851,PM28901,PM51008,PM3312,PM53008,PM19013,PM5391,PM2512B,PM13156,PM19016,PM3352B,PM14924,PM3352A

奥拉(Aurasemi)时钟和电源管理产品选型指南

目录- 公司简介 Timing BU Introduction VRM LDO & BuckBoost

型号- AU4562,AU5424,AU5425,AU5426,AU5327BC1-QMR,AU5325BC1-QMR,AU5620,AU5508,AU560X,AU5315AC0-QMR,AU5328,AU532X,AU8010AA-QNR,AU5329,AU8014EB-QNR,AU5329B-QMR,AU8310A0-WMR,AU5325BC2-QMR,AU5411A-QMR,AU5327BC2-QMR,AU8014EA-QNR,AU8013EB-QNR,AU4531,AU5X82,AU8941,AUXXXX,AU5410,AU5411,AU571X,AU531X,AU5615,AU5424G,AU5617,AU5317AC0-QMR,AU5424A,AU5410A-QMR,AU8014A,AU8013EA-QNR,AU8012AA-QNR,AU5X8,AU8011CA-QNR,AU4592

【选型】奥拉时钟驱动器AU5426A-QMR用于光端机,支持4路差分输出和1路单端输出

某用户在研制光端机时需求时钟buffer,要求低抖动,最好是国产的,推荐奥拉的时钟驱动器AU5426,它是一款支持4路差分输出和1路LVCMOS输出的超低抖动时钟和扇出缓冲器,该缓冲器可以选择来自主时钟、次时钟或晶振的时钟输入。

【选型】支持8-50MHz晶体输入的Au5411A-QMR时钟buffer用于通信管理机,可简化电路节约PCB板空间

电源、时钟、复位时硬件电路三大核心电路,具有举足轻重的地位,对于产品的正常工作非常重要,本文主要介绍奥拉电子时钟buffer Au5411A-QMR在一款通信管理机中的应用。

【产品】3:1输入时钟选择的时钟驱动器AU5411,可支持10路2.1GHz的低抖动时钟输出

奥拉半导体是一家跨国无晶圆厂半导体公司,专注于高端模拟和混合信号集成电路的解决方案。其推出的时钟驱动器AU5411支持10路2.1GHz的低抖动时钟输出,主要用于低抖动、高频时钟/数据分配和电平转换用途,该缓冲器可以选择从主时钟、次时钟或者晶振输入。

AU5424G: 1.8 V TO 3.3 V HIGH PERFORMANCE LVCMOS CLOCK BUFFER OUTPUT, ULTRA LOW JITTER BUFFER

型号- AU5424BG-DNR,AU5424G,AU5424BG-DMR,AU5424BG-EVB

AU5411 – 10 OUTPUT, DIFFERENTIAL, ULTRA LOW JITTER BUFFER

型号- AU5411,AU5411A-QMR,AU5411A-EVB,AU5411A-QMT

电子商城

服务

深圳市启威测实验室,面向所有企业提供信号完整性测试服务,主要包括USB、HDMI 、DP、MIPI、PCIe 、SD/EMMC、DDR接口信号测试。测试手段有波形测试、眼图测试、抖动测试等。

提交需求>

登录 | 立即注册

提交评论