How ATP Protects Your Data and SSDs with HW/FW Power-Loss Protection

Solid state drives (SSDs) are particularly vulnerable to unstable power conditions and unexpected power interruptions. Unlike HDDs, SSDs do not have mechanical parts, so every component is electronic. The internal data management of an SSD involves many operations happening in the background, and every power loss or failure, no matter how short, can mean undue interruption of those operations, which could affect drive performance.

Data is typically written on the SSD in this order:

1. The Host sends data to the SSD.

2. The SSD Storage Controller acknowledges that data has been received.

3. If the SSD does not have a DRAM cache, the Storage Controller moves the data to the NAND flash memory, which is non-volatile memory, so the data is safely stored even when power is terminated. If the SSD has a DRAM cache, the data is moved there first. This is volatile memory, so if power is terminated, the data is lost.

4. The Storage Controller decides when to "Flush" the data from the DRAM cache to the NAND flash memory.

In a normal power shutdown, all data from the host is successfully transmitted to the NAND flash memory. Even if power is cut off, data remains there.

When power is terminated before data is moved or flushed into the SSD, the data may be corrupted or lost.

Four Levels of Power-Loss Protection

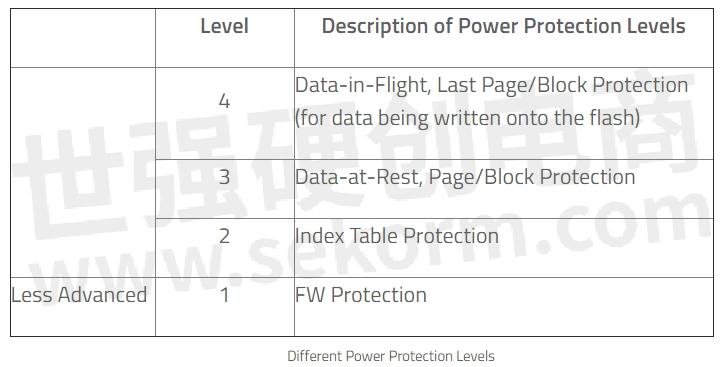

Power-Loss Protection (PLP) mechanisms built into modern solid-state drives (SSDs) can be categorized into four levels:

Damaged Firmware Protection (Level 1). Multiple copies of the firmware (FW) are generated at different times to ensure a backup copy exists in the master firmware that gets corrupted. The master FW is always stored on the strongest flash pages and access is limited to reduce the possibility of reading disturb, and to ensure both FW and data integrity.

Linking Table Damage Protection (Level 2). A NAND flash device creates a linking table to keep track of the physical flash pages with respect to the logical block addresses from the host. The linking table must be maintained and updated constantly so that the host can always access the most updated data via the two mapping addresses recorded on the flash device and the host.

The linking table is cached first and rewritten to the flash from time to time so that the frequent index updating operation does not slow down the ongoing writing performance. When power disruption occurs while some mapping information is still in the flash cache, the mapping index is damaged, along with the data in the flash mapped by the respective linking table. The worst-case scenario is the destruction of the index table, resulting in the loss of all data in the storage device.

Multiple copies of the linking table are backed up for future restore situations when the linking table is distorted or lost during a sudden power loss, thus eliminating the risk of losing all data in a flash device as a result of losing the linking table.

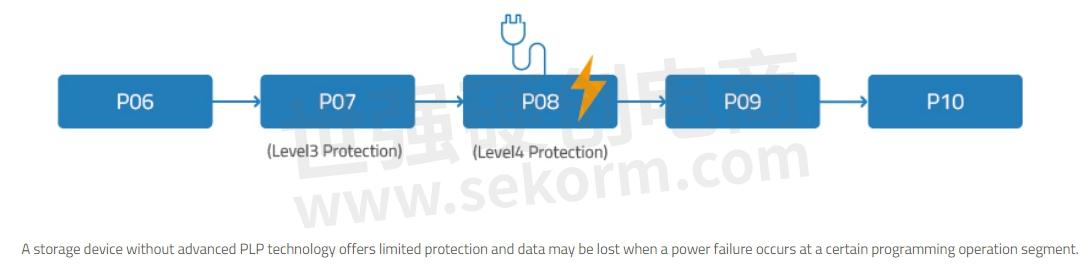

Page/Block Protection (Level 3). Data written on flash chips is divided into segments of millisecond-long operations. If power loss occurs and the writing process is interrupted at one segment point, for example, the 8th millisecond, data error may occur when the host tries to access the part of the data that was lost during the power loss interruption. Level 3 protection ensures completion of the write command prior to power failure, preventing any data loss.

Last Write Page/Block Protection (Level 4). For SSDs with Level 4 protection, data in transit is secured by providing enough power to complete the last program operation before the power loss, guaranteeing that data is safely written onto the flash chip. In the illustration above, the last millisecond-long program operation is completed and data in the 8th segment is safely stored.

The following table summarizes the various levels of power protection to prevent data loss:

ATP Sudden Power-Off Recovery (SPOR): Pure FW Power-Loss Protection

ATP Sudden Power-Off Recovery technology provides firmware-based PLP to minimize the effects of sudden power off.

■ISP Code Backup. As soon as the device is powered On, the temporary in-system programming (ISP) code is generated in a spare block to reduce read access of the main ISP and to reduce the chances of reading disturbed.

■Link Table Mapping Address Backup. After power is on, the FW will trace the link table from the latest mapping address. If the link table is found to be invalid, the FW will search the previous mapping address until the valid one is found. The mapping address is stored on a strong page only to ensure its integrity.

ATP's Superior HW + FW Power-Loss Protection Technology

It is critical to have a power-loss protection (PLP) mechanism, especially in high-performance computing environments where devices are running 24/7, the deployment is extensive, and data, as well as device integrity, could spell the difference between operational failure and success. Protecting stored data is just as crucial as protecting data in transit.

ATP provides state-of-the-art defense against data loss, integrating hardware design and firmware algorithms to deliver the best power-loss protection available today.

ATP harnesses the advantages of tantalum polymer capacitors, featuring low series resistance and minimal sensitivity to temperature and humidity. ATP SSDs with HW+FW PLP technology are assured of high reliability and endurance even in harsh environments. They also enable the HW+FW PLP mechanism to be implemented in small-size SSDs.

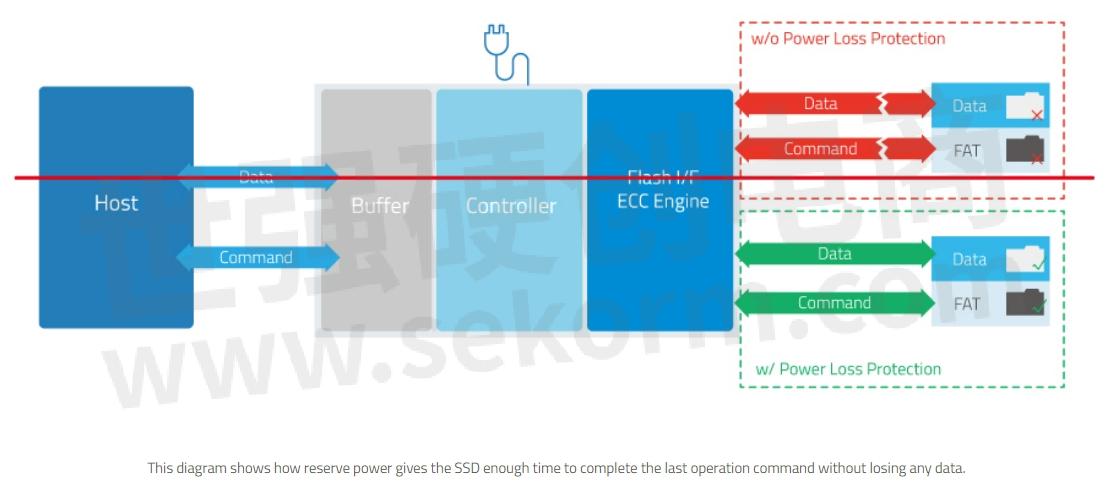

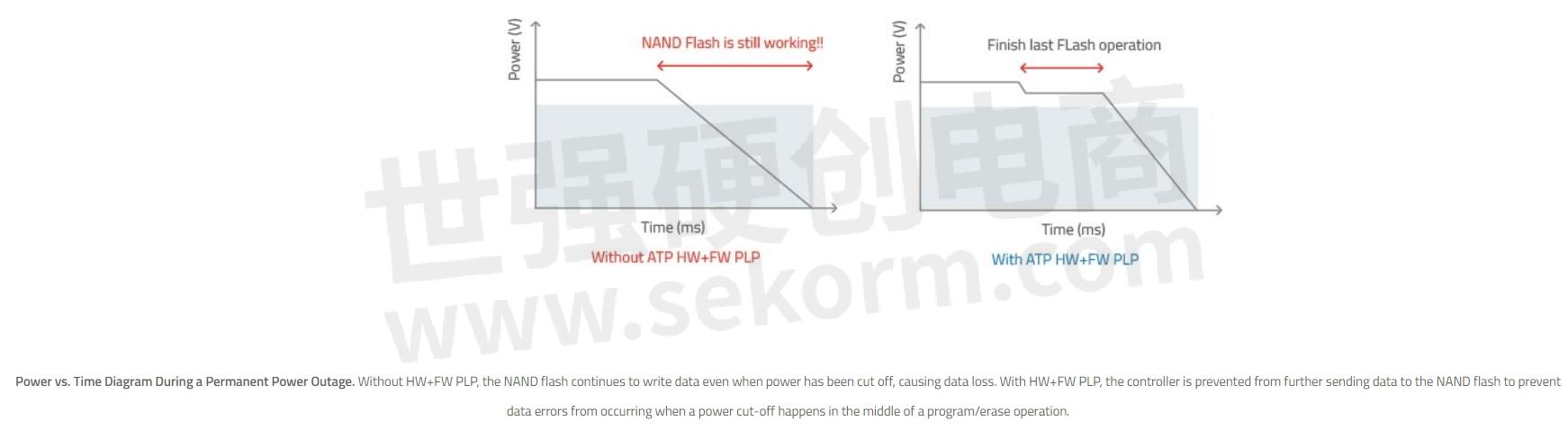

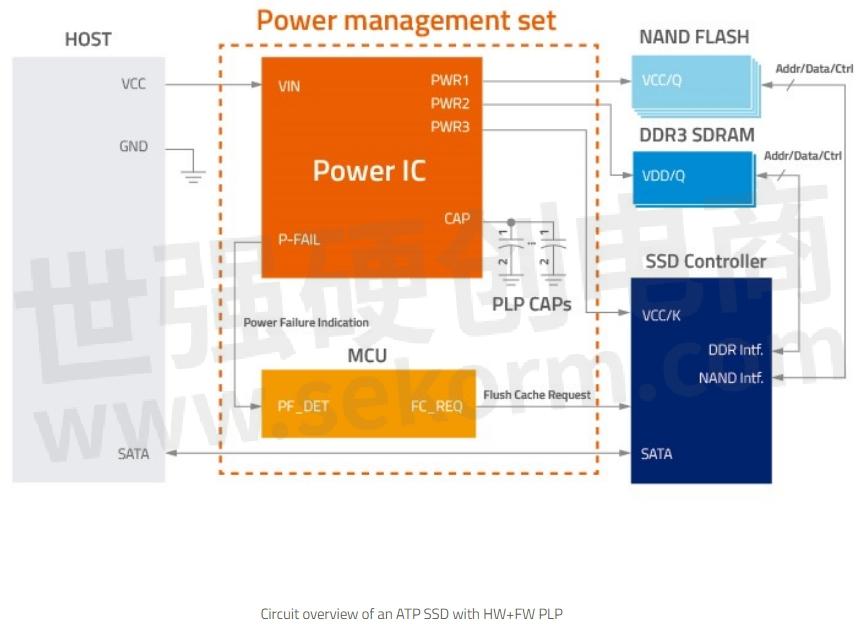

Upon sensing a power loss event, a power loss detection circuit integrated in the SSD immediately activates the power protection mechanism. The SSD then uses up reserve power from capacitors on the drive to complete the last Read, Write or Block Erase operation, while simultaneously stopping the controller from sending data to the flash chip to make sure that no data is lost in transit.

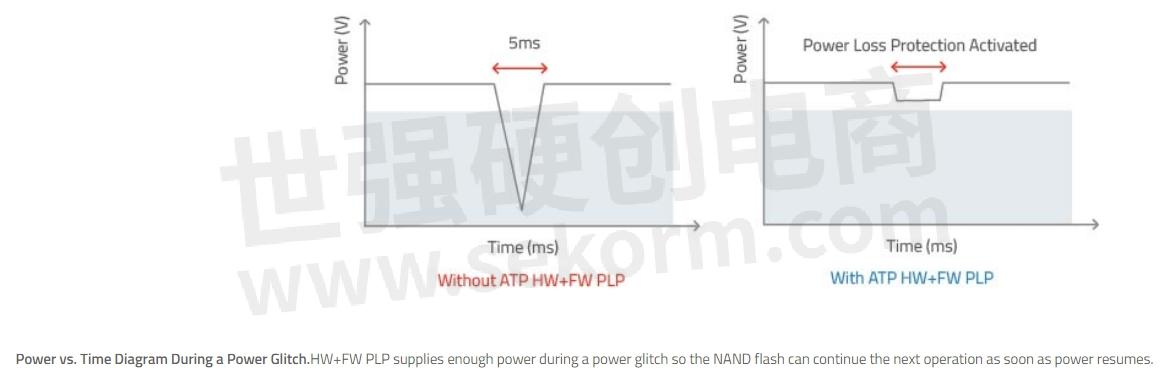

The following diagrams show how ATP's HW+FW PLP prolongs the functionality of the NAND flash in two scenarios, allowing the SSD to complete the last command or data given by the controller.

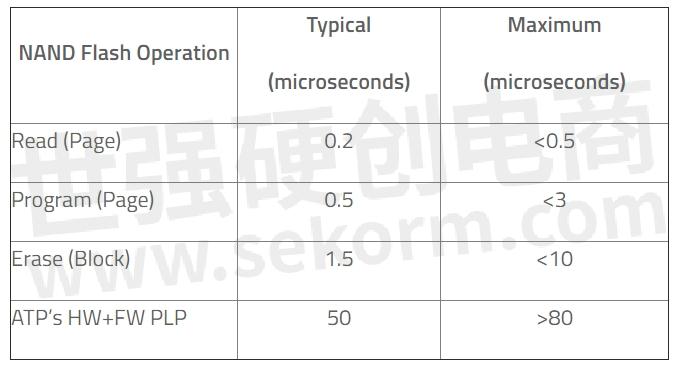

The following table shows the typical and maximum amount of time in microseconds (ms) for ATP's HW+FW PLP to complete various commands during a power loss event.

Microcontroller-Based PLP

Select SSDs use a microcontroller unit (MCU) that provides unparalleled defense for ATP Serial ATA (SATA) and NVMe SSDs to deliver the best PLP protection in the industry. Integrated into ATP HW+FW PLP, the completely new design of the PLP array utilizes a new power management IC (PMIC) and new firmware‑programmable MCU that allow the PLP array to perform intelligently in various temperatures, power glitches and power states.

MCU-based PLP provides over input voltage protection, power-up inrush current suppression, input power noise de-glitch, fast power on-off control, PLP capacitors over voltage protection, and customization options.

ATP Power Cycling Tester

ATP's own-built power cycling tester validates the design of the PLP mechanism under sudden power-off conditions. At the beginning of each cycle, the power tester writes a segment of data pattern onto the SSD test device. Power is then cut off at the exact configured millisecond while data is being programmed into the NAND flash blocks. By creating a sudden power failure at the "write" command stage, the test proves the effectiveness of the PLP mechanism, showing a "Pass" over thousands of power cycles without any data errors.

During the Power Cycling Test, a window of time for a device without ATP HW+FW PLP is evident during the specific time frame in milliseconds when data loss is most likely to occur with a power glitch. This finding is critical for product development teams to fine-tune the programming of future NAND flash products with their host systems.

The following figures show that a product without the ATP HW+FW PLP will have corrupted data and a "Fail" result due to data miscompare in the post-test check conducted after each power cycle. The product with ATP HW+FW PLP shows a "Pass" result without any data loss.

Conclusion

ATP offers both firmware and hardware solutions aimed at protecting valuable data on an SSD. ATP HW+FW PLP offers advanced power-loss protection to ensure data integrity even during a power failure scenario and to preserve data in mission-critical applications. The PLP mechanism features a standalone design, solid-state capacitors, and long life span.

For SSDs with ATP's MCU-based PLP, the power-loss protection exceeds the performance and reliability offered by other basic backup solutions. Moreover, ATP's Power Cycling Tester, which removes power at the exact millisecond during the programing of the NAND flash product, further validates and improves ATP product lines' overall reliability.

- |

- +1 赞 0

- 收藏

- 评论 0

本文由西瓜头头大转载自ATP ELECTRONICS,原文标题为:How ATP Protects Your Data and SSDs with HW/FW Power-Loss Protection,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

ATP对所有SSD进行数千小时RDT测试,确保产品严格遵守最高质量标准

可靠性验证试验(RDT)是对ATP固态驱动器(SSD)进行的一项长期严格测试,旨在证明每个SSD符合最严格的质量要求。ATP在较长时间内对其 SSD执行完整的实际驱动器级别测试,以验证额定MTBF值,而不是依赖可靠性预测系统。

ATP‘s Power Loss Protection Just Got Smarter with MCU-based SSD Design

ATP customers want constant assurance that power loss events will not cause massive downtime or lost data that could affect business operations and lead to higher operating costs. The MCU intelligently monitors sudden power failure conditions from a glitch to a surge or a complete outage...

ATP SSD寿命验证测试:确保从0%到100%甚至超过生命周期的可靠性、耐久性和保留率

SSD的预期寿命取决于多个因素,ATP会进行EOL(end-of-life,寿命验证 )测试,保证SSD在给定时间内的有效使用。目的是确保SSD在生命周期(甚至更长时间)内能继续可靠地工作并保持数据完整性。

PCIe®Gen 3 NVMe M.2 2280/2242/2230 SSD专业存储和内存解决方案的全球领导者

ATP推出PCIe Gen 3 NVMe M.2 SSD,具备数据保护、加密和散热解决方案。产品支持多种容量和温度范围,提供高性能和可靠性,适用于嵌入式和工业应用。

ATP - PCIE®GEN 3 NVME M.2 2242固态硬盘,PCIE®GEN 3 NVME M.2 2280固态硬盘,PCIE® GEN 3 NVME M.2 2230 SSD,SSD,M.2 2280 NVME模块,NVME SSDS,PCIE® GEN 3 NVME M.2 2242 SSD,M.2 2280 NVME SOLID STATE MODULES,固态硬盘,PCIE® GEN 3 NVME M.2 2280 SSD,M.2 2280 NVME MODULES,PCIE®GEN 3 NVME M.2 2230固态硬盘,M.2 2280 NVME固态模块,NVME固态硬盘,FT960GP38AG8BPC,N750PI,FT480GP38ANDBFC,FT120GP38AG8BPC,FT480GP38AG8BPC,FT480GP34ANDBFC,FT960GP38AG8BPI,FT240GP38AG8BPC,FT120GP38ANDBFC,N700PC,FT240GP38AG8BPI,FT120GP38AG8BPI,N600SC,N650SI,N600VI,FT960GP34ANDBFC,N700PI,FT240GP38ANDBFC,N600SI,FT120GP34ANDBFC,N650SC,FT240GP34ANDBFC,N600VC,FT480GP38AG8BPI,工业应用,INDUSTRIAL APPLICATIONS

笔记本需要更换大容量硬盘,求推荐性价比更的SSD固态硬盘。

您好,推荐ATP(华腾国际)的SSD固态硬盘,M.2 NVMe接口最高容量可达1TB,M.2 2280接口最高容量1TB,SATA接口最高容量1TB,具体可参考【选型】ATP(华腾国际)内存及存储产品选型指南

ATP工业企业SSD系列产品宣传单

ATP Industrial Enterprise SSD系列结合了工业级和企业级存储解决方案的优点,适用于边缘计算环境。该系列SSD采用NVMe PCIe Gen4x4接口,提供M.2、U.2和E1.S三种形态,适用于数据中心向边缘计算转移的趋势。产品具备高耐用性、数据保留能力、一致性能、高质量服务和高可靠性,同时支持宽温度范围和硬件电源丢失保护。ATP还提供固件定制服务,以满足不同企业客户的需求。

ATP - PCIE®GEN4 NVME E1.S固态硬盘,固态硬盘,PCIE®GEN4 NVME U.2固态硬盘,INDUSTRIAL SOLID-STATE DRIVES,PCIE ® GEN4 NVME M.2 SSD,工业固态硬盘,SSDS,PCIE®GEN4 NVME M.2固态硬盘,PCIE® GEN4 NVME U.2 SSD,INDUSTRIAL ENTERPRISE SSD,PCIE ® GEN4 NVME E1.S SSD,工业企业SSD,FT400GP48APHBSI-ERS2,FT480GP48APHBSI-ERS3,N651SIE SERIES,FT800GP48APHBSI-ERS2,FT240GP48APHBSI-ERS3,FT800GES4APHBSI-ERS2,FT1T60ES4APHBSI-ERS2,FT240GP48APHBSI-ERS1,FT120GP48APHBSI-ERS3,FT6T40U24APHBSI-ERS2,FT3T20ES4APHBSI-ERS2,FT3T84ES4APHBSI-ERS1,FT7T86ES4APHBSI-ERS1,FT1T60P48APHBSI-ERS2,FT3T20U24APHBSI-ERS2,FT480GP48APHBSI-ERS1,FT1T92P48APHBSI-ERS1,FT960GES4APHBSI-ERS1,FT960GES4APHBSI-ERS3,FT1T60U24APHBSI-ERS2,FT960GU24APHBSI-ERS1,N651SIE,FT960GU24APHBSI-ERS3,FT200GP48APHBSI-ERS2,FT7T86U24APHBSI-ERS1,FT3T84ES4APHBSI-ERS3,FT3T84U24APHBSI-ERS3,FT3T84U24APHBSI-ERS1,FT960GP48APHBSI-ERS3,FT800GU24APHBSI-ERS2,FT1T92U24APHBSI-ERS3,FT480GU24APHBSI-ERS3,FT6T40ES4APHBSI-ERS2,FT1T92U24APHBSI-ERS1,FT480GES4APHBSI-ERS3,FT1T92ES4APHBSI-ERS3,FT960GP48APHBSI-ERS1,FT1T92ES4APHBSI-ERS1

ATP推出业界最高擦写寿命的工业级固态硬盘(SSD),具有出色的耐久性和在极端温度下工作的能力

ATP推出N751Pi系列PCIe Gen4 NVMe M.2 2280 SSD,该SSD在配置了pSLC NAND的工业级固态硬盘(SSD)中具有出色的耐久性和在极端温度下工作的能力,是恶劣环境、恶劣条件和高负荷工作负载下关键任务和写入密集型应用的理想选择。

The Doctor is in: ATP PLP Diag Offers Proactive Capacitor Health Checks to Avert PLP Failures

As more industries and enterprises rely on SSDs for reliable data storage under all circumstances, especially during unpredictable power loss events, ATP Electronics strengthens its SSDs‘ MCU-based HW PLP design with PLP Diag. By proactively monitoring the health of its polymer tantalum capacitors and responding to potential failures that expose the in-flight data to risks, PLP Diag offers fail-safe protection to ensure uncompromised data integrity and device reliability.

ATP推出工业宽温企业级SSD系列产品N651Sie,包含U.2,M.2,E1.S三种接口类型

ATP推出工业宽温企业级SSD系列产品N651Sie,结合了工业级固态硬盘和企业解决方案的优点,专为在不受控制的恶劣环境中处理企业级工作负载而设计。

【经验】过度配置如何提高基于NAND的ATP SSD的耐用性和性能介绍

过度配置(overprovisioning, OP)为固态硬盘(SSD)的垃圾收集过程提供了额外的空间,有助于提高性能,并增加其耐久性,从而有助于延长驱动器寿命。本文ATP ELECTRONICS深入介绍OP及其大小如何影响写入(TBW),以及SSD的随机写入性能。

PCIe®Gen 3 NVMe M.2 2280/2242/2230固态硬盘

ATP推出的PCIe Gen 3 NVMe M.2 2280/2242/2230 SSD,基于NVMe协议和PCIe Gen3 x4接口,提供高速、可靠和持久的性能,满足嵌入式和工业应用日益增长的数据存储需求。这些模块采用3D TLC NAND闪存,容量从40GB到960GB不等,适用于不同的数据存储需求。

ATP - M.2 2280 NVME SOLID STATE MODULES,M.2 2280 NVME固态模块,第三代NVME M.2 2280/2242/2230固态硬盘,NVME固态硬盘,GEN 3 NVME M.2 2280 / 2242 / 2230 SSD,NVME SSDS,FT960GP38AG8BPC,N750PI,FT480GP38ANDBFC,FT120GP38AG8BPC,FT480GP38AG8BPC,FT480GP34ANDBFC,FT960GP38AG8BPI,FT240GP38AG8BPC,FT120GP38ANDBFC,N700PC,FT240GP38AG8BPI,FT120GP38AG8BPI,N600SC,N650SI,N600VI,FT960GP34ANDBFC,N700PI,FT240GP38ANDBFC,N600SI,FT120GP34ANDBFC,N650SC,FT240GP34ANDBFC,N600VC,FT480GP38AG8BPI

【产品】ATP的SSD固态存储盘,具有静态数据安全功能,可快速安全地删除所有数据

ATP的SSD固态存储盘,具有静态数据安全功能,可快速安全地删除所有数据,可应要求提供各种客户和应用程序特定功能,以防止未经授权访问SSD,系统或网络,定义读/写访问限制(包括WORM)或验证要访问的内容。

【经验】什么是SSD的M.2标准?M.2 SSD和mSATA SSD之间又具体有哪些差异?

近年来发布的固态驱动器(SSD)变得更快,并且能够处理大量数据。但是,它们的全部功能受到与其连接的接口的阻碍或限制。Mini-SATA(mSATA)接口虽然专为提供最小的SSD尺寸而设计,但受到SATA 6 Gb / s的限制。M.2标准是内部安装的计算机附加卡的规范,旨在解决mSATA的局限性,并为小型卡(包括不同大小和容量的SSD)提供更多选择。

ATP Industrial Enterprise SSD Series: The Best of Both Worlds, Engineered for Uncontrolled Environments at the Edge

ATP offers the best of both of industrial and enterprise worlds: THE NEW INDUSTRIAL ENTERPRISE Series, which leverage NVMe PCIe Gen4x 4 and are available as M.2, U.2, and E1.S. They combine the best of enterprise and industrial features, making them excellent as boot drives, data storage drives, or mixed-use drives.

ATP NVMe BGA pSLC SSD安全保护及加密功能特点

硬件写保护* 写保护功能将ATP NVMe BGA SSD置于“只读”模式,以防止数据写入设备,并保护重要数据不被意外删除、移动或修改。通过在控制器印电路板(PCB)上的通用输入/输出(GPIO)信号引脚的特定引脚上放置跳线,在存储设备上启用写保护。硬件快速擦除*对于特定应用,主机可以使用GPIO连接器触发“擦除数据”行动。

电子商城

现货市场

服务

可定制ATP TE Cooler的冷却功率:40~200W;运行电压:12/24/48V(DC);控温精度:≤±0.1℃; 尺寸:冷面:20*20~500*300;热面:60*60~540*400 (长*宽;单位mm)。

最小起订量: 1 提交需求>

登录 | 立即注册

提交评论