【经验】电科星拓时钟Buffer芯片TBUF1510在客户服务器上的应用案例详解

上期我们详细介绍了时钟Buffer芯片以及关键的参数(【技术】解析时钟Buffer芯片及关键参数),本次分享TBUF1510在大客户的应用经验,帮助大家深入理解时钟Buffer的应用。首先我们先回顾TBUF1510关键规格和优势参数。

TBUF1510规格参数

TBUF1510—10路输出超低附加抖动差分时钟缓冲器

1、产品特性

· 灵活支持单端、差分和晶体输入

· 10路差分输出,最高1.5GHz,支持LVPECL、LVDS、HCSL模式

· 附加抖动<30fs(@100MHz HCSL模式)

· LVCMOS高达200MHz参考输出

· 从输入到输出通道的低延迟(typ<0.8ns)

· 工作电压:2.5V/3.3V

· 温度范围:-40℃~85℃

· QFN-48封装(7mmx7mm)

2、关键优势

· 附加抖动 :超低

· 传输延时 :低

· 输出偏移 :低

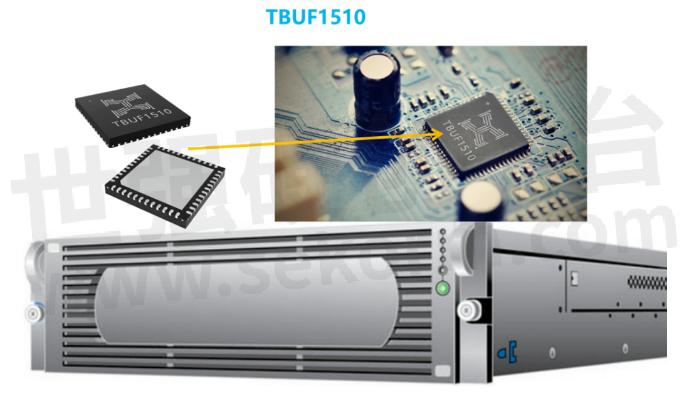

了解完TBUF1510的相关规格和优势,我们进入今天的主题,下图展示了TBUF1510在客户服务器上的应用。

图1 TBUF1510应用场景与应用框图

PCH自身产生三个100MHz的基频时钟,经过三颗TBUF1510就会扇出三十个时钟信号,分别提供给CPU、RISER SLOT、SNIC、BMC、M.2接口卡和外设接口等稳定的时钟,以保证他们可以正常稳定长期地工作。为了更好的理解图1中的应用框图,下面先通过图2的主板3D效果图让大家有一个简单的认识,然后我们再通过6个部分来详细讲解主板的大体架构、重要组成部件和TBUF1510的应用。

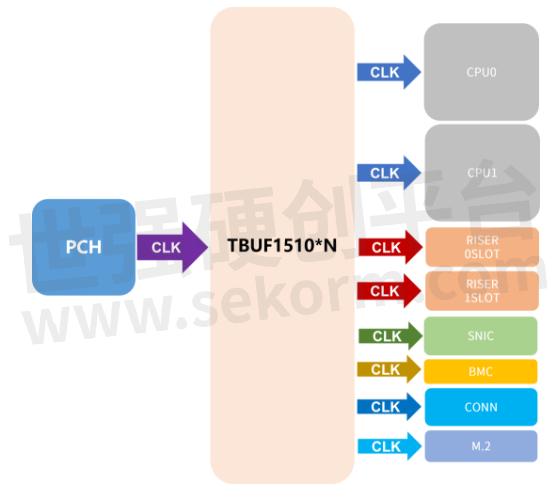

图2 主板3D示意图

01、PCH(平台控制集成器)

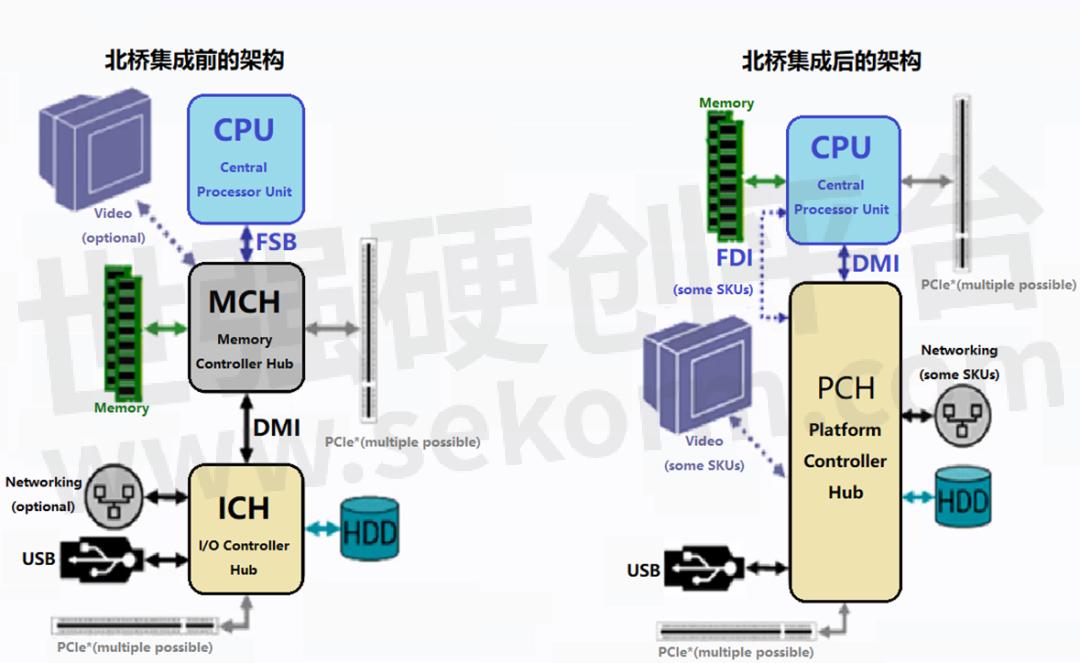

对于图1中PCH这个概念我们在此来做个详细介绍,它是Platform Controller Hub(平台控制集成器)的缩写,它还有一个大名鼎鼎的中文名字:“南桥”。一提南桥,相信很多小伙伴都会恍然大悟,原来南桥就是PCH。

具体南桥在主板上到底有什么用呢?

要解答这个问题,那就不得不提PCH的前身ICH了。ICH和PCH一样,是一个英文名称I/O Controller Hub的缩写。一看到I/O,相信小伙伴们顿时明白了,这不就是Input/Output的缩写嘛!!!

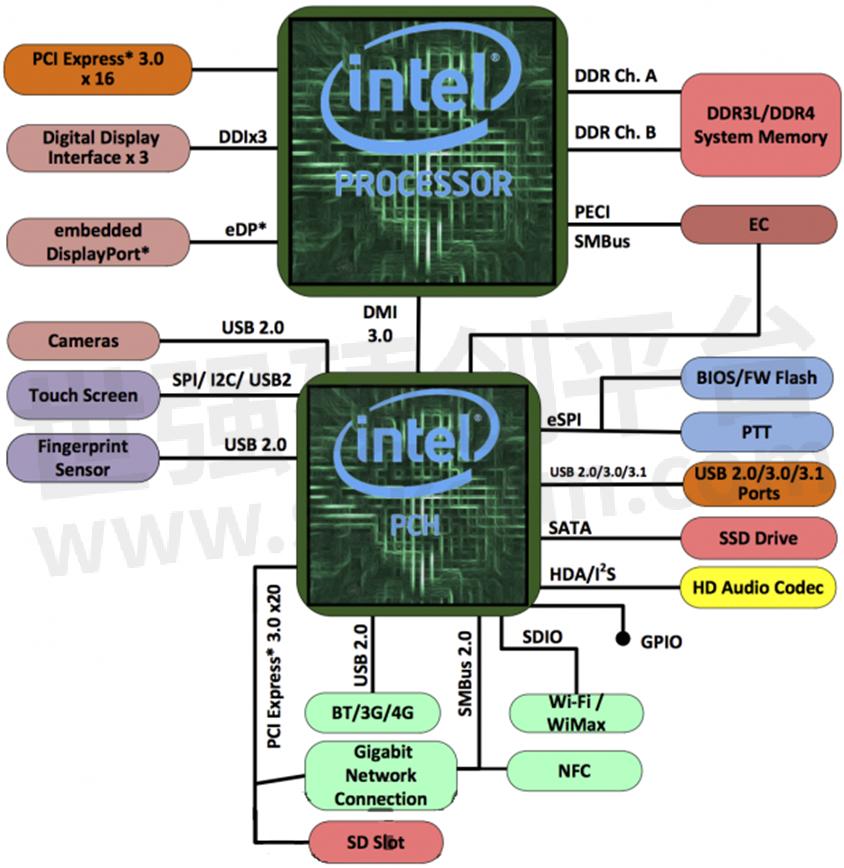

到此,顾名思义,大家应该都大体知道ICH的作用了。输入输出控制中心,职责就是负责I/O总线之间的通信,例如PCI总线、IDE设备、USB、LAN、ATA、SATA、音频控制器、键盘控制器、实时时钟控制、高级电源管理等。

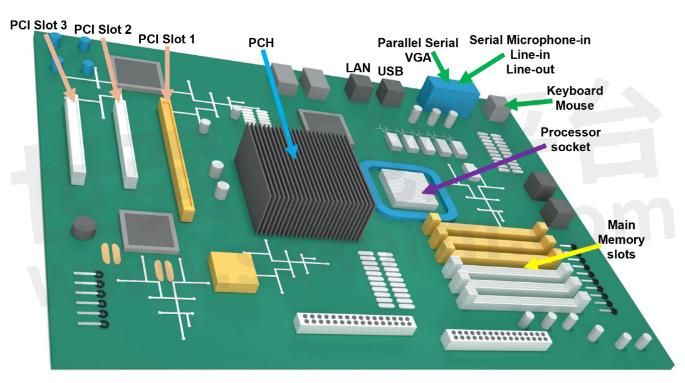

PCH作为统管大部分IO设备的最后一个江湖大佬,而ICH到PCH的转变却十分的小,时至今日,除了DMI随着PCIe3.0升级到DMI3.0,增加了更多的功能外,其它变化相对较小。为了给大家更为直观的认知,请看下面图示:

PCH的概念就介绍到这里,下面我们一起来看下PCH是怎么控制实时时钟输出的。

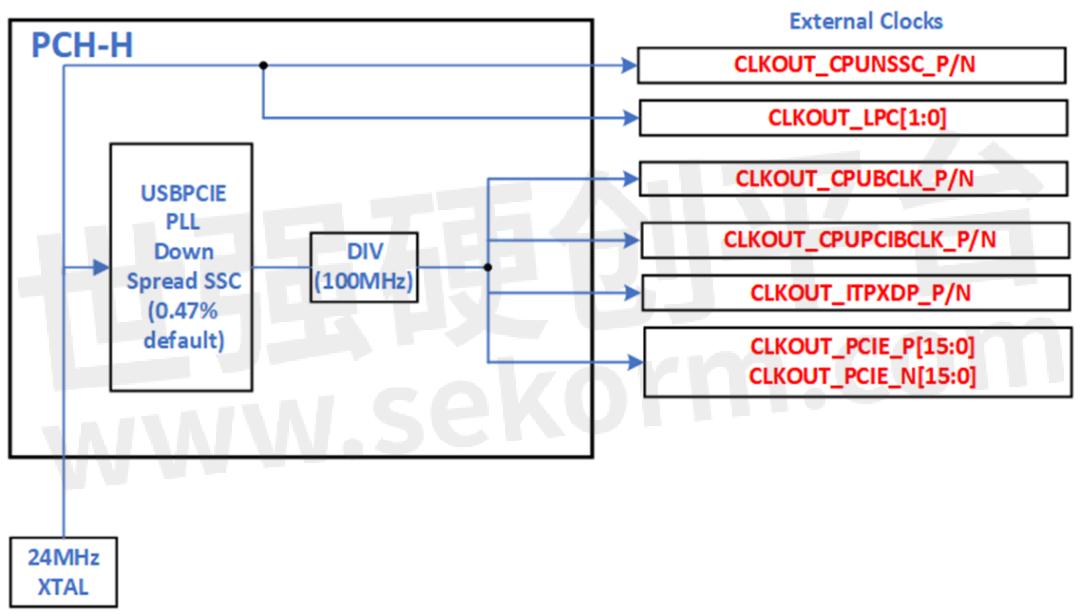

02、实时时钟的输出原理

主板上一般会有一个基准的24MHz频率无源晶振XTAL,它接入南桥PCH的嵌入式时钟控制器ICC(Integrated Clock Control),经过其中的PLL和差分器,输出100MHz的时钟信号CLKOUT_CPUBCLK_PIN。这个CLKOUT_CPUBCLK_PIN就是大名鼎鼎的BCLK。

图3 PCH内部时钟产生的原理图

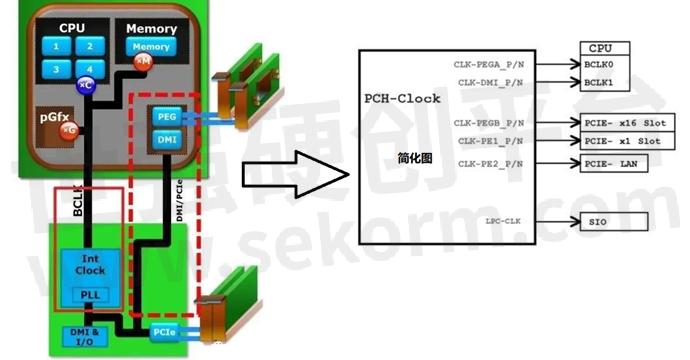

BCLK也叫做基频(Base Clock,BCLK),它像天山上流下来的第一股泉水,从南桥流出,汇入CPU,从此不断分叉,滋养了其中大多数IP,如内核、核显,也包括今天的主角CPU Cores。大家通过下图4关于PCH提供时钟的概念图相信就会有一个直观的理解了。

图4 PCH提供时钟的概念图

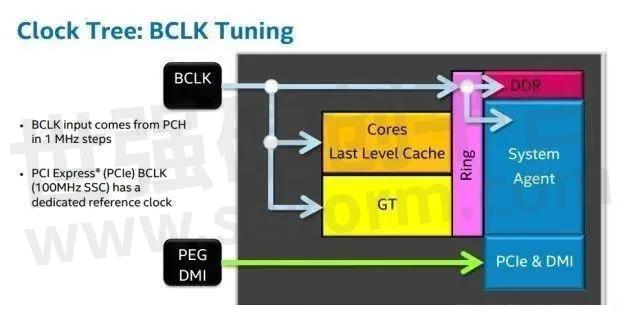

它是基准频率,其他的频率都是在它的基础上变换出来的,以下是基于基频变化的时钟树简图。

图5 基于基频变化的时钟树简图

CPU中的各个器件并不是工作在100MHz上,各个IP有自己的倍频(Multiplier)为自己服务。例如CPU内核的频率就是这样计算的:

CPU主频 = 基频BCLK×倍频

举个例子,标称3.5GHz的CPU,它的基频是100MHz,内核的倍频是35,算下来就是:100×35=3.5GHz

倍频器(Multiplier)

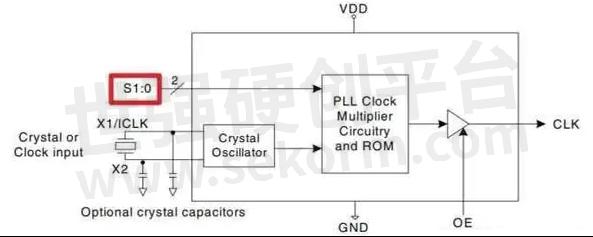

举个PLL Clock Multiplier的例子,它的原理很简单,就是通过S0,S1两个pin脚来控制输出clock对输入clock的倍数,如下图红框部分:

关于实时时钟输出原理就介绍到这里,下面我们再来看下主板上的另外一部分DMI接口。

03、DMI接口

DMI是Direct Media Interface(直接媒体接口)。由Intel公司开发用于连接主板南北桥的总线,取代了以前的Hub-Link总线。DMI采用点对点的连接方式,时钟频率为100MHz,由于它是基于PCIe总线,同样采用8bit/10bit(有效位宽8bit)编码因此具有PCIe总线的优势。

在4系列芯片组没有取消前端总线FSB时,DMI是Intel公司开发用于北桥(G)MCH(Graphics&Memory controller hub)和南桥ICH10/ICH7之间的芯片连接总线。DMI实现了上行与下行双向数据传输率,单通道单向传输速率达到2.5GT/s,采用8bit/10bit编码,共计4条通道。这个高速接口集成了高级优先服务,允许并发通讯和真正的同步传输能力。它的基本功能对于软件是完全透明的,因此早期的软件也可以正常操作。

从5系列芯片组开始的新构架设计中,前端总线被取消,北桥芯片的功能被整合进CPU中。显卡采用了PCIeX16的通道直连CPU,当有多卡使用需求时,可按实际应用分为X8+X8(双卡)或X8+X4+X4(三卡)(具体分配方式要参考主板设计)。因为在PCIe2.0的应用中,DMI接口升级到了DMI2.0,单通道单向传输速率达到5GT/s。同时DMI2.0也不再用于南北桥芯片的连接,而是用于CPU和芯片组(原南桥芯片组)的连接。

图6 PCH与CPU的连接通信图

04、BMC的介绍

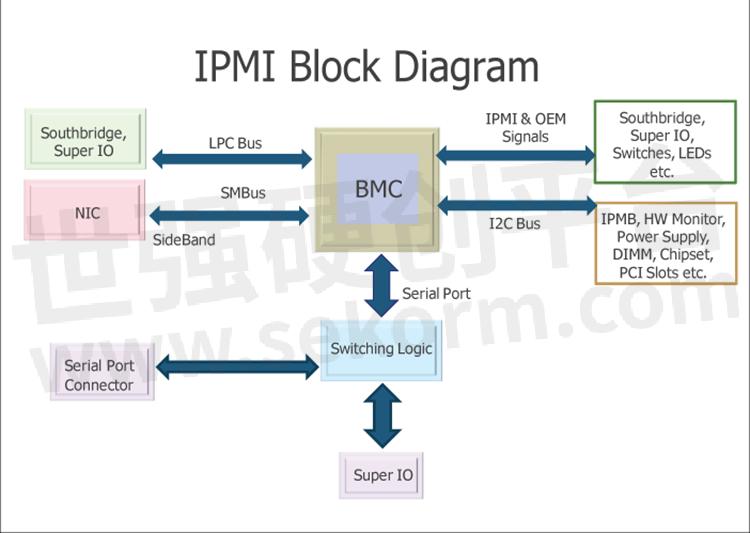

在介绍BMC之前需要了解一个概念,即平台管理(platform management)。平台管理表示的是一系列的监视和控制功能,操作的对象是系统硬件。比如通过监视系统的温度,电压,风扇、电源等等,并做相应的调节工作,以保证系统处于健康的状态。

当然如果系统真的不正常了,也可以通过复位的方式来重新启动系统。同时平台管理还负责记录各种硬件的信息和日志记录,用于提示用户和后续问题的定位。下图是平台管理涉及到的功能概述:

以上的这些功能可以集成到一个控制器上来实现,这个控制器被称为基板管理控制器(Baseboard Manager Controller,简称BMC)。需要说明BMC是一个独立的系统,它不依赖于系统上的其它硬件(比如CPU、内存等),也不依赖于BIOS、OS等(但是BMC可以与BIOS和OS交互,这样可以起到更好的平台管理作用,OS下有系统管理软件可以与BMC协同工作以达到更好的管理效果)。

图7 BMC的工作原理图

05、应用图中几个模块简介

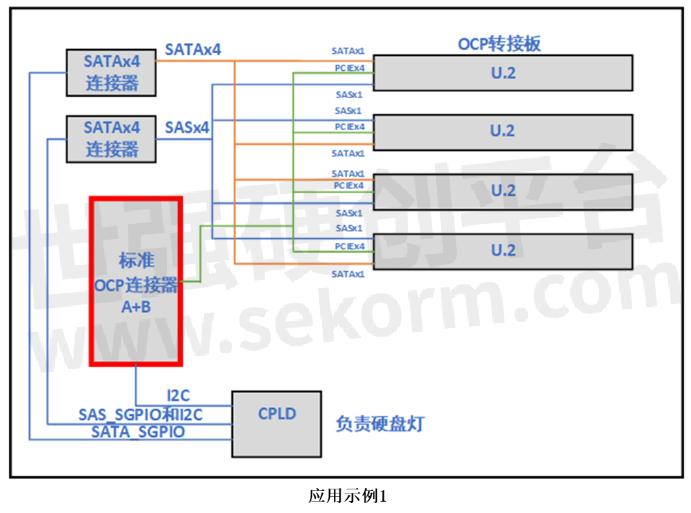

对于服务器网卡(Server Network Interface Card,简称SNIC)、M.2接口所对应设备来说,他们是通过一对或者多对REFCLKP/N差分时钟来保证信号稳定性的。也就是说,PCH将所需要的时钟传给TBUF1510,而TBUF1510接收到所需要的时钟信号,会扇出多路时钟,分别提供服务器网卡、M.2接口所对应设备。TBUF1510这种扩展能力也极大解决了PCH时钟信号数量不够用的窘迫之态。以下为相关的图示供大家参考。

SNIC

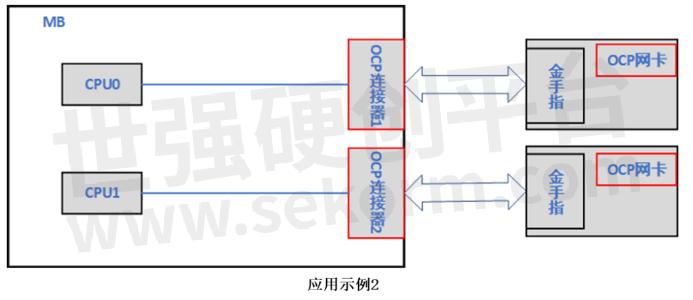

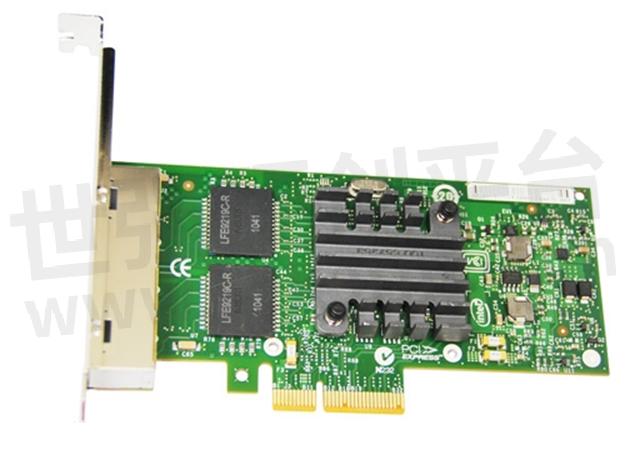

在服务器领域中,OCP和I350统称为服务器网卡,下面我们带大家简单看下OCP和I350网卡。

图8 OCP网卡应用原理图

图9 I350网卡图

M.2

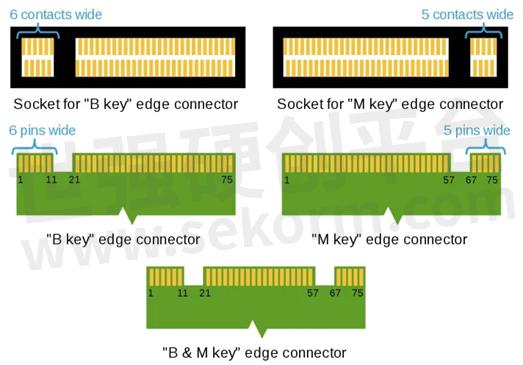

按照接口类型分,可以把M.2接口分为Socket 2和Socket 3;

Socket 2也可以叫做B key,支持SATA,PCIe×2;

Socket 3也可以叫做M key,支持SATA,PCIe×4;

06、TBUF1510的应用

通过前面五个部分的介绍,实时时钟是如何由PCH控制的原理,以及后面所支持的设备和接口,相信大家已经有了初步了解。

那现在问题来了,PCH自身所产生的时钟是有限的,主板上各色各样的芯片、外设接口以及扩展接口,例如图1中的CPU、RISER SLOT、BMC、CONN、M.2、SNIC等,都需要时钟才可以正常工作。

时钟就如同人的心脏一样是节拍器,只有它稳定地工作,整个系统才可以高效有序的运转。此时,TBUF1510的优势就体现出来了,一个时钟输入可以扇出十个时钟输出。再加上TBUF1510的三大关键优势和众多大客户对产品的认可,相信不久的将来一定可以打出一片属于自己的天地。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由犀牛先生转载自电科星拓公众号,原文标题为:TBUF1510应用案例详解,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

PCIe Retimer TX和RX电气测试

随着PCIe速率越来越高,信号衰减和抖动问题开始突出,为了确保长距离、复杂环境或高数据速率下,PCIe链路仍能保持稳定可靠的通信,出现了PCIe Retimer。本文论述了高速的PCIe Retimer如何进行高效的电气测试。

PCIe Retimer参与链路训练行为总览

我们将聚焦PCIe Retimer的通信介质角色,和您一起详细了解PCIe Retimer是如何通过参与链路训练行为实现链路状态管理,以提高数据传输稳定性、一致性。

【技术】解析时钟Buffer芯片及关键参数

时钟芯片是高性能通讯系统中必不可少的核心芯片,其性能及可靠性直接影响着通讯系统的主要性能和系统稳定性。本文中电科星拓将为大家详细讲解下时钟Buffer的分类和关键参数等。

成都电科星拓科技有限公司(Silicon Innovation)成立于2019年12月,总部位于成都,在深圳、北京、上海、杭州设有研发中心,是一家业界领先的互联芯片解决方案提供商。

成都电科星拓科技有限公司产品介绍

型号- XSAT系列,PEFS1215,TGEN6308,INTL9548,INTL9306,TGEN6309,INTL9544,INTL9545,XUSB系列,INTL9546,INTL系列,OCDR2822,TBUF系列,OCDR281X,STMP112,STMP431,STMP432,TBUF1308,PSTD0601,PSTD1612,TGEN6310,XSAT2102A,TBUF0210,INTL9617,XSAT2204,XSAT2202,XUSB,OCDR2814,OCDR2811,PSTD1606,RCD,OCDR280X,TBUF0208,STMP系列,TGEN系列,XUSB2102,TBUF0320,INTL3306,TGEN6302,XUSB2104,TGEN6304,MSPD系列,MSPD,TBUF0204,STMP75,OCDR,XSAT,INTL9641,OCDR2801,PEFS0505,PMIC5001,PMIC5002,PMIC5003,OCDR2804,TBUF,INTL3416,PSTD1630,XSAT2104A,RCD系列,XSAT2104,STMP,INTL9554,INTL9555,INTL9511,RCD5001,MSPD5118,TGEN6310B,PEFS1205,TBUF0308,STMP464,OCDR系列,TBUF0306,STMP5111,TGEN6320,INTL3524,TBUF1510,PSTD1620,PEFS1250,RCD5002,TGEN,RCD5003,TBUF0304,INTL3528,INTL

电科星拓芯片选型表

电科星拓提供以下技术参数的芯片选型表,包含:时钟Buffer芯片、时钟发生器芯片、I2C接口芯片、数字温度传感器芯片、PCIe Bridge(转SATA)芯片、DDR5 RCD芯片、DDR5 SPD Hub芯片、CDR芯片、电源管理芯片

|

产品型号

|

品类

|

系列

|

规格

|

状态

|

封装

|

|

TBUF0320

|

时钟Buffer芯片

|

TBUF系列

|

20路DB2000QL CLK Buffer (LPHCSL)

|

MP

|

LGA80

|

选型表 - 电科星拓 立即选型

TBUF1510 High Performance Ultra Low Jitter Differential Fanout Buffer Datasheet

型号- TBUF1510,TBUF1510QFIGR

世强硬创获电科星拓授权,提供企业级时钟与数字隔离芯片等产品代理

致力于提供技术领先和高性价比的企业级时钟、接口、电源管理类等芯片。通过技术创新和产业协作,突破瓶颈技术和核心专利,实现互联芯片解决方案服务千行百业客户。

【IC】电科星拓推出业界首款满足PCIe Gen5的全新时钟Buffer芯片-TBUF1510,时钟频率高达1.5GHz

电科星拓推出业界首款满足PCIe Gen5的全新时钟Buffer芯片--TBUF1510,支持高达1.5Ghz时钟频率,多路输出,超低延迟和抖动,可灵活配置支持PCIe5.0、5G无线、56G以太网等各种应用,广泛应用于服务器、存储、5G通信、PC等多种产品。

【技术】电科星拓带您认识时钟发生器和缓冲器

本文中电科星拓尝试给大家梳理时钟的起源和发展史,并带大家认识时钟发生器和缓冲器,以及电科星拓的时钟产品介绍,希望能解除大家心中疑惑。

TBUF0304 High Performance Ultra Low Jitter Differential Fanout Buffer Datasheet

型号- TBUF0304QFIGR,TBUF0304

电子商城

服务

可支持TI AM335x/AM5718 和NXP iMX6/iMX8芯片定制核心板和计算单板;支持NXP iMX6核心模组X / F / H系列、TI AM335x核心模组X / N / H系列,与兼容的底板组合定制单板计算机。

最小起订量: 1pcs 提交需求>

世强深圳实验室提供Robei EDA软件免费使用服务,与VCS、NC-Verilog、Modelsim等EDA工具无缝衔接,将IC设计高度抽象化,并精简到三个基本元素:模块、引脚、连接线,自动生成代码。点击预约,支持到场/视频直播使用,资深专家全程指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论