若贝微电子推出基于RISC—V的沉芯异构芯片和自主研发的IDE工具,具有节能的特点

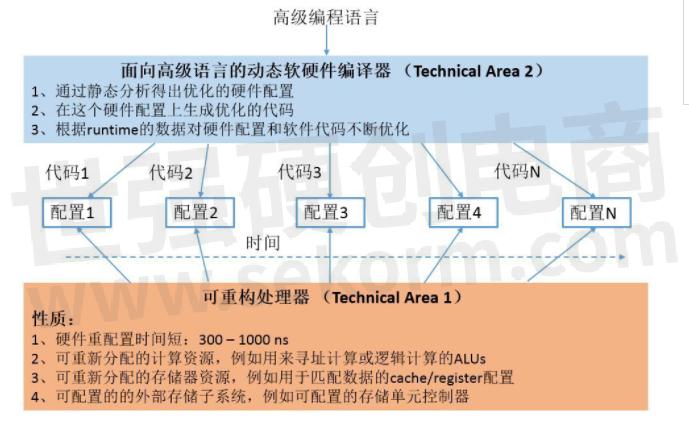

自从集成电路设计行业进入片上系统(SOC)时代,芯片集成的功能模块(IP)越来越多,芯片面积越来越大,功耗越来越高,必须依赖先进的工艺才能把功耗和芯片面积控制下来。每个功能模块在芯片上都占用了一定的面积,为了控制功耗,不用的时候断掉电源用的时候才上电。比如一开始在使用A模块,但是程序要运行B模块,就需要把A模块关掉,给B模块上电,重置一下寄存器,然后再使用B模块。关断与切换的过程大概耗时100纳秒到1微秒的时间,而且关断与切换的方式需要同时把A和B模块预先集成到硅晶圆上,会增加硅晶圆面积,也增加了功耗。

美国把芯片制造大厂台积电搬到了美国国内,那给咱们剩下的就是一些低端工艺,低端工艺肯定在功耗和面积上面和5nm,3nm工艺相比差距很远。所以我们在低端工艺上生成芯片,在设计芯片的时候就要跳出传统模式,采用节能省功耗,时空改变的方式去满足高端芯片的需求。什么是时空变化,怎样在有限的面积上设计更多的芯片,可以看看沉芯的演变。

时空转换

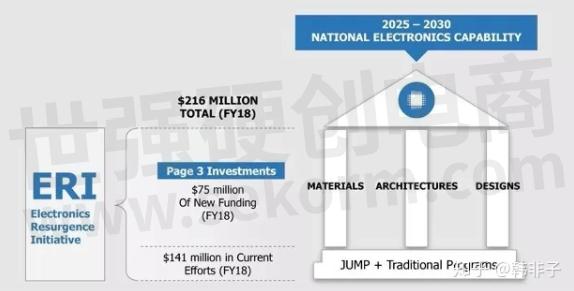

沉芯优势,基于RISC—V,将串行 MCU或者CPU与并行处理的自适应动态可重构架构相结合,实现串并行自由切换,这种架构美国国防科工局和google都在研究,(虽然公司官网被黑多次,但是核心信息还是掌握在自己手里,这种芯片架构已经获得美国和加拿大国际专利)

沉芯具备控制流的串行计算和数据流的并行计算,并且可以在串并行计算之间自由切换,一颗芯片可以替代CPU+DSP CPU+FPGA或CPU+DSP+FPGA的多芯片系统。

沉芯异构芯片包括三款RAC101,RAC102,RAC03,其中:编号为RAC102XXX,该芯片支持RISC-V开放指令集的RV32IM,三级流水,支持10MHZ~200MHZ主频, 72个32位元的动态可重构计算单元、12个32位乘法器及单精度浮点计算单元(IEEE-754标准)、通用接口为SPI、QSPI、UART、PWM、I2C、SDRAM(RAC101和RAC102不含)、按组可配置GPIO等。

自主研发的IDE工具——Robei IDE Tool

应用场景与领域:

应用领域为:嵌入式、数字信号处理、机器人、智能家电、智能家居、物联网、智能玩具、电机控制等。

典型应用场景:

1. 家电的末端智能(洗衣机、冰箱、空调、集成灶、洗碗机等等)

2. 小型机器人

3. AI 应用

4. 无人船和无人艇

5. 智慧海洋浮漂

6. 可穿戴设备

7. 指纹锁

8. 电动工具控制器

9. 智能玩具

10. 小家电(电饭煲、榨汁机、烧水壶、饮水机等等)

- |

- +1 赞 0

- 收藏

- 评论 0

本文由Jessica_li转载自Robei公众号,原文标题为:基于RISC-V异构芯片-沉芯线上产品介绍,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

2024全国大学生集成电路创新创业大赛——Robei职业技能杯

随着中国集成电路产业的快速发展,集成电路技能型人才的缺乏已经成为困扰行业的一个难题。为适应行业对集成电路技能型人才的需求,2024全国大学生集成电路创新创业大赛开设职业技能赛项,青岛若贝电子有限公司加入并开启第一届集创赛Robei职业技能杯,以下是大赛相关内容。

若贝微电子EDA软件集成可视化和模块化分层设计理念,采用透明、开放模型IP资源,助力加快设计速度

Robei EDA工具,是一款全新的集成电路前端设计、仿真工具,最新可视化的分层设计理念、透明的模型库,以及非常友好的用户界面。Robei软件将芯片设计高度抽象化,并精简到三个基本元素:模块、引脚、连接线。

什么是我国芯片行业“卡脖子”的根本原因?

国外对于芯片设计上游EDA与IP的垄断,使得我国芯片技术成为了掣肘,唯有加大自主研发和政策扶持,完善EDA软件和IP才能对芯片设计行业有进一步的促进作用。Robei EDA软件是由若贝公司自主研发的一款全新的集成电路设计工具。采用框图和代码相融合的设计模式,自动生成端口定义的Verilog代码以及约束文件。

异构芯片成未来趋势,解析已成功量产的国产自研异构芯片

若贝微电子量产的一颗中等型号沉芯异构芯片编号为RAC102XXX,该芯片支持RISC-V开放指令集的RV32IM,三级流水,支持10MHZ~200MHZ主频, 72个32位元的动态可重构计算单元、12个32位乘法器及单精度浮点计算单元(IEEE-754标准)、通用接口为SPI、QSPI、UART、PWM、I2C、SDRAM(RAC101和RAC102不含)、按组可配置GPIO等。

【产品】主频10-200MHz,可替代CPU+DSP、CPU+FPGA或 CPU+DSP+FPGA系统的自适应芯片|视频

若贝微电子CEO吴国盛介绍了自主设计开发的自适应芯片产品,包含RAC101、RAC102、RAC103三个系列,重点介绍了自适应芯片的技术背景和特点,其自适应结构可自由切换、核心数可按需定制、实现高算力但是功耗不增加。

【产品】若贝新推快速动态可重构的串并行一体化自适应芯片,三级流水,支持RISC-V指令集

通过对现有架构的优劣分析,若贝微电子基于自适应芯片多年研究的基础,提出全新的快速动态可重构的自适应芯片架构。基于该架构并结合超高速动态可重构的计算阵列,打造出串并行一体化的自适应芯片。

RAC101系列沉芯异构芯片

描述- 本文档介绍了Robei沉芯异构芯片V 1.5,这是一种基于RISC-V指令集的CPU加上并行计算的动态可重构阵列(CGRA)组成的异构系统芯片。该芯片具有串行计算和控制流的能力,同时支持并行计算和数据流处理,适用于多种嵌入式应用。

型号- RAC103,RAC102IQ064X,RAC103C,RAC101C,RAC102C,RAC101IQ064N,RAC103I,RAC101I,RAC102I,RAC102 系列,RAC101,RAC102,RAC102IQ064N,RAC101 系列

RAC101/RAC102/RAC103 沉芯异构芯片

描述- 本文档介绍了Robei沉芯异构芯片V 1.5,这是一种基于RISC-V指令集的CPU加上并行计算的动态可重构阵列(CGRA)组成的异构系统芯片。该芯片具有串行计算和控制流的能力,同时支持并行计算和数据流处理,适用于多种嵌入式应用。

型号- RAC103,RAC102IQ0641X,RAC101IQ064N,RAC101,RAC102,RAC102IQ064N

【产品】国产自研采用自适应架构的沉芯异构芯片RAC102XXX,支持10MHZ~200MHZ主频

若贝微电子量产的一款中等型号沉芯异构芯片RAC102XXX,该芯片支持RISC-V开放指令集的RV32IM,三级流水,支持10MHZ~200MHZ主频, 72个32位元的动态可重构计算单元、12个32位乘法器及单精度浮点计算单元。

Robei EDA软件开放免费试用,可与VCS、NC-Verilog、Modelsim等EDA工具无缝衔接

EDA软件是芯片研发设计环节必不可少的工具。3月19日,国产EDA公司若贝微电子在平台上线了Robei EDA软件免费试用服务,面向所有企业用户提供此服务。Robei EDA软件是一个全新的面向对象的可视化芯片设计软件,支持基于Verilog语言的集成电路前端设计与验证。该软件具备可视化架构设计、核心算法编程、自动代码生成、语法检查、编译仿真与波形查看等功能。另外,Robei EDA软件以易用和易

【经验】窗口看门狗实验步骤及代码示例

看门狗负责定期的查看芯片内部的情况,一旦发生错误就向芯片发出重启信号。看门狗在程序的中断中拥有最高的优先级,防止程序跑飞及防止程序在线运行的时候出现死循环。而窗口看门狗通常被用来监测应用程序背离原有的运行序列导致的故障。本文介绍窗口看门狗实验步骤及代码示例。

Robei EDA集成电路实验平台采用IP白盒子,搭载核心开发板和实验箱,助力提高设计和动手能力

为增强学生设计实战能力,若贝微电子Robei EDA集成电路实验平台:只需要学生在C语言的基础上,快速了解和学习IP设计中的硬件描述语言Verilog语言。该平台同时培养学生的软件和硬件能力,并增强和拓展学生就业技能和操作实战能力。为提高中国的核心高科技技术人才,若贝公司结合自己企业特色,增强产学合作,培养更优秀的设计人才。

【经验】浅析Robei IDE工具的使用步骤

Robei IDE工具是若贝公司研发用于沉芯系列芯片的项目开发与编程。本文详细解析了Robei IDE工具的使用步骤。

电子商城

服务

Ignion可支持多协议、宽频段的物联网天线方案设计,协议:Wi-Fi、Bluetooth、UWB、Lora、Zigbee、2G、3G、4G、5G、CBRS、GNSS、GSM、LTE-M、NB-IoT等,频段范围:400MHz~10600MHz。

最小起订量: 2500 提交需求>

提供语音芯片、MP3芯片、录音芯片、音频蓝牙芯片等IC定制,语音时长:40秒~3小时(外挂flash),可以外挂TF卡或U盘扩容。

最小起订量: 1pcs 提交需求>

登录 | 立即注册

提交评论