【产品】采用高性能28nm工艺的FPGA器件Seal SA5Z-30系列,总容量高达1242Kbits

西安智多晶微电子有限公司的Seal(海豹)5000 SA5Z-30系列FPGA器件(下称“本系列FPGA”),建立在一个优化的低功耗,高性能28nm工艺基础之上。通过最低的成本,融合新架构,多个崭新与优化功能的嵌入式模块来实现高速FPGA,使系统设计师在降低成本的同时又能够满足不断增长的高性能应用要求。对无线和有线通信、工业控制,图像处理,人工智慧,数据处理中心及云信息等行业中的低功耗,高性能的大小型应用,本系列FPGA无疑是最理想的选择。

1.1特性

丰富的逻辑资源:

⚫32,666逻辑单元的器件

⚫多达243个用户I / O

高性能可编程逻辑单元

⚫采用6输入查找表(6-LUTs)

⚫双5-LUTs选项

⚫最多128位分布式存储器

⚫最多64位分布式移位寄存器

低功耗器件

⚫先进28nm铜CMOS工艺

⚫核电压1.0V,Vccaux为3.3V

⚫待机模式和其他省电选项

嵌入式和分布式存储

⚫Fmax = 500 MHz

⚫嵌入块存储容量为18K/9Kbits, 总容量高达1242Kbits

⚫高达653Kbit的分布式存储

高性能,灵活的I / O单元

⚫LVDS接口高达1.0Gbps

⚫可编程IO缓冲区支持多种接口:

⚫LVCMOS3.3 / 2.5 / 1.8 / 1.5

⚫LVTTL

⚫PCI,TMDS, MINI-LVDS

⚫BLVDS,MLVDS,RSDS,LVPECL

⚫SSTL/DIFF-SSTL 25/18/15

⚫HSTL/DIFF-HSTL 18/15

⚫施密特触发器输入迟滞

⚫I/O支持热插拔

⚫可编程上拉、下拉或总线保持模式

⚫I/O块(Bank) 1、2和3的输入输出支持3.3/2.5/1.8/1.5/1.2V电压,I/O块4的输入输出只能支持1.8V/1.5V电压

源同步I / O接口

⚫支持7:1 Video接口,可高达1.0Gbps

⚫通用DDRX1/X2/X4/X5/X8 最高1.0Gbps

⚫单端/差分DQS支持的DDR1/2/3内存

增强的乘法器块

⚫Fmax = 500 MHz

⚫内置多个9x9/18x18/25x18具备预加法的串行乘法器, 算数逻辑单元(ALU),两层叠加实现DSP处理密集型应用

灵活的片内时钟

⚫24个全局时钟与4个边沿时钟於每个I/O模块(Bank)

⚫4个延时锁相环(DLL)用于高速I/O接口

⚫2个内置通用PLL, 提供倍频、分频、相位转移、展频等系统时钟

⚫精度为+/-6%的片上振荡器

配置模式

⚫JTAG, 从模式(PS/SCPU),主模式(AS)

⚫配置完成后支持SED/SEC单/多比特流检测及单比特纠正

⚫配置过程支持多个比特流加载,可在第一个程序文件加载失败后,自动跳到Golden区域加载第二个程序文件

⚫局部重配置(Partial Re-configuration)

⚫支持3:1压缩及1:3解压缩

⚫兼容IEEE1149.1:如符合边界扫描(BSCAN)

⚫符合IEEE 1532的系统内编程

安全

⚫支持AES-256比特流加密及解密

合封DDR2 SDRAM存储

⚫128/256/512Mbits DDR2 SDRAM,工作频率Fmax=400MHz

上电顺序

⚫先核电压(Vcc)后,再上1.8电位

嵌入式硬核

⚫Fmax=250MHz MCU

⚫Fmax=533MHz DDR2存储控制器

⚫2路12 bits@125 ~ 200 kbpsADC

⚫片上SPI, I2C,定时器/计数器

低成本封装

⚫低成本焊线封装芯片

⚫先进的无铅封装

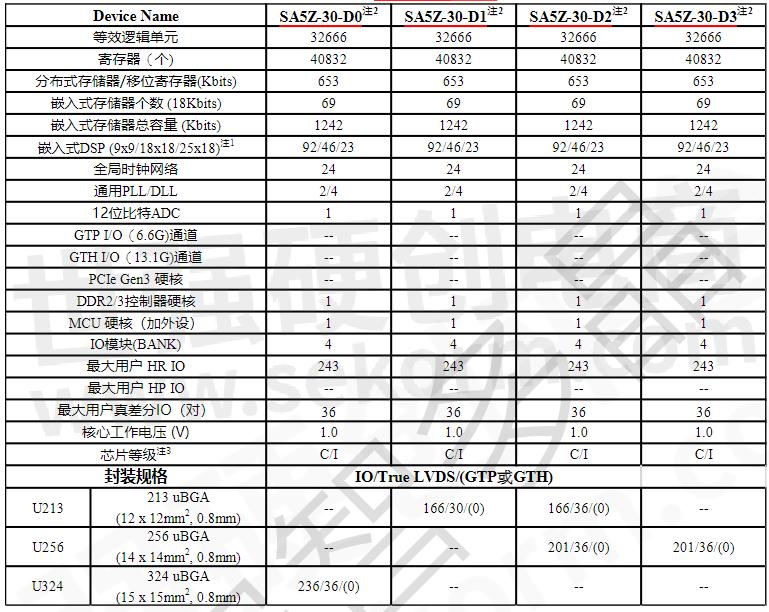

1.2器件资源

表1-1Seal(海豹)SA5Z-30系列器件资源

【注】

1.一片DSP包含4个9x9或2个18x18具备预加法的串行乘法器和1个54位累加器或两片组合为一个25x18串行乘法器

2.D0/D1/D2/D3 代表0/128/256/512Mbits DDR2 SDRAM

3.等级: C: 商业级,结温温度0℃-85℃; I: 工业级,结温温度-40℃-100℃

4.SA5Z-30-ES只有18对LVDS TX

1.3器件结构概述

本系列FPGA的核心构架由六输入查找表(LUTs)、逻辑单元存储器模块,加法器,乘法器构成和分布式存储器/移位寄存器。嵌入式存储器模块具有18或36Kbit的SRAM存储器。嵌入式存储器模块配置成单端口、伪双端口、真双端口RAM以及FIFO缓冲器或者ROM。嵌入式乘法器模块可以在单一模块中实现一个18×18或两个9×9乘法器,利用两模块可实现25x18乘法器。本系列FPGA器件的I/O功能是由许多低成本应用中的多样化I/O标准所驱动的,大幅度提高了I/O的性能要求,可以轻松、灵活地容纳您的主模块设计,并支持可编程总线保持、可编程上或下拉电阻、可编程延迟、可编程驱动能力、可编程斜率控制、热插拔。

本系列FPGA的器件有多个PLL和DLL,以及全局和边沿时钟网络以提供可靠、有效且低偏斜和高速度的时钟管理与综合。您可以在HqFpga软件中对PLL进行重配置时钟频率或者相位。另提供DDRSDRAM存储器接口解决方案,由一个PHY接口和一个存储再加上软或硬核控制器组成。在Dx-系列的器件,所有IO Bank4的I/O都连接合封128Mbits DDR2 SDRAM存储芯片的管脚,与DDR2控制器硬核配合提供更有效、高性能的存储应用。

智多晶提供不同PHY接口IP如Video7:1,与顾客定制的控制器或智多晶提供的控制器一起使用,得以提升与优化更全面的设计。本系列FPGA提供多个硬核IPs如MCU、ADC和DDR2控制器等等,配合不同的设计应用。外部主机通过JTAG访问端口,被动串行(PS)、被动并行(SCPU)端口或主动串行(AS)端口进行配置本系列FPGA,或利用额外的硬件来完成远程现场升级。

1.4合封DDR2 SDRAM

1.4.1SA5Z-30-D1

SA5Z-30-D1采用最新的3D合封技术与一片8Mx16 bit的DDR2 SDRAM (M14D128168A)合封而成。其DDR2 SDRAM特性如下:❖合封DDR2 SDRAM电源

◼I/O块(Bank) 4的Vccio(x) 提供合封DDR2 SDRAM读/写电源,其电压必须为1.8V+/-0.1V

◼内置128Mb DDR2 SDRAM存储空间,16数据总线位宽,最高400MHz工作频率,最大读写带宽800MB/s

❖结构

◼支持JEDEC 标准

◼SSTL18 接口

◼可分为4块(Bank),每块区域大小为2Mx16 bits

◼支持突发读/写(Burst Read/Write),突发长度可为4和8

◼CAS延迟时间(CAS Latency) 可为3, 4, 5, 6和7

◼数据选取脉冲(DQS) 双沿触数据(DQ) 转换

◼数据选取脉与读取数据边缘对齐,与写入数据中心对齐

◼支持数据屏蔽(Data Mask, DM)

◼片内可调差分阻抗(OCT)与终端电阻(ODT)

◼除了数据和数据屏蔽外,所有输入都在系统时钟的上升沿进行采集

◼自动和自刷新

❖读/编程/擦除

◼最小时钟周期:2.5ns

◼最小时钟高脉冲宽:1.2ns

◼最小时钟低脉冲宽:1.2ns

◼最小输入数据(DQ) 与数据屏蔽(DQM) 设定时间(相对数据选取脉冲DQS) :200ps

◼最小输入数据(DQ)与数据屏蔽(DQM) 保持时间(相对数据选取脉冲DQS):200ps

◼地址与控制总线设定时间:125ps

◼地址与控制总线保持时间:200ps

◼工作电流@突发长度=4:250mA

◼块(Bank) 工作电流@突发长度=4:260mA

◼待机电流:90mA

◼刷新电流:6mA@自刷新,105mA@突发刷新

1.4.2SA5Z-30-D2

SA5Z-30-D2 采用最新的3D合封技术与一片32Mx16 bit的DDR2 SDRAM (M14D5121632A)合封而成。其DDR2 SDRAM特性如下:

❖合封DDR2 SDRAM电源

◼I/O块(Bank) 4的Vccio(x) 提供合封DDR2 SDRAM读/写电源,其电压必须为1.8V+/-0.1V

◼内置512Mb DDR2 SDRAM存储空间,16数据总线位宽,最高400MHz工作频率,最大读写带宽800MB/s

❖结构

◼支持JEDEC 标准

◼SSTL18 接口

◼可分为4块(Bank),每块区域大小为8Mx16 bits

◼支持突发读/写(Burst Read/Write),突发长度可为4和8

◼CAS延迟时间(CAS Latency) 可为3, 4, 5, 6, 7, 8和9

◼数据选取脉冲(DQS) 双沿触数据(DQ) 转换

◼数据选取脉与读取数据边缘对齐,与写入数据中心对齐

◼支持数据屏蔽(Data Mask, DM)

◼片内可调差分阻抗(OCT)与终端电阻(ODT)

◼除了数据和数据屏蔽外,所有输入都在系统时钟的上升沿进行采集

◼自动和自刷新

❖读/编程/擦除

◼最小时钟周期:2.5ns

◼最小时钟高脉冲宽:1.2ns

◼最小时钟低脉冲宽:1.2ns

◼最小输入数据(DQ) 与数据屏蔽(DQM) 设定时间(相对数据选取脉冲DQS) :200ps

◼最小输入数据(DQ)与数据屏蔽(DQM) 保持时间(相对数据选取脉冲DQS):200ps

◼地址与控制总线设定时间:125ps

◼地址与控制总线保持时间:200ps

◼工作电流:230mA

◼块(Bank) 工作电流@突发长度=4:180mA

◼待机电流:60mA

◼刷新电流:8mA@自刷新,120mA@突发刷新

1.5封装特性

◼无铅,小型,多IO封装

◼12mm x 12mm uBGA213,多达166个单端口IO

◼14mm x 14mm uBGA213,多达201个单端口IO

◼15mm x 15mm uBGA324, 多达236个单端口IO

◼优化的引脚排布,使得只需要两层PCB

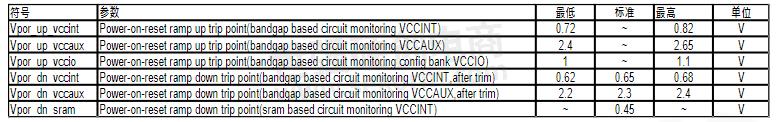

SA5Z-30交直流特性

POR触发点

表3-1Seal(海豹)POR触发点规格

【注】

1.Config块的VCCIO没有上电复位的下降触发点

2.Vccint, Vccio, Vccaux一定维持建议的工作点来保证正常工作

3.电源上升时间为0.2 –50ms

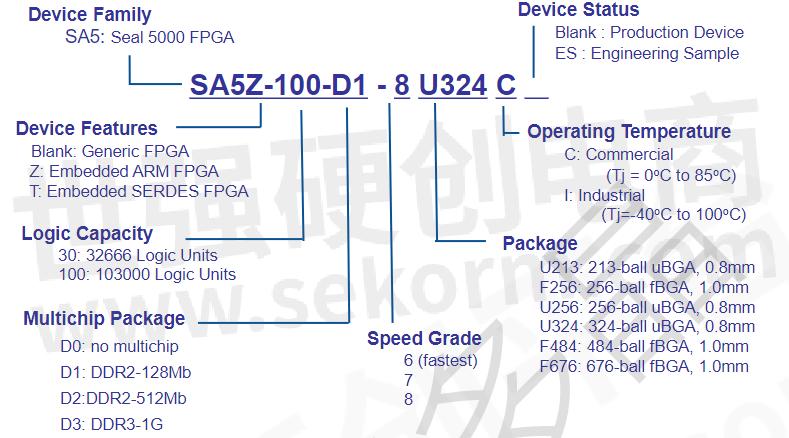

器件编号说明

图2-1器件编号说明

- |

- +1 赞 0

- 收藏

- 评论 0

本文由Lonely转载自智多晶,原文标题为:Seal(海豹)SA5Z-30 FPGA产品手册,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【IC】智多晶推出基于FPGA的高精度PWM控制方案,提升到了1ns的脉宽和相位精度且资源消耗极低

近日智多晶应用团队的一项Precise_PWM demo,使用智多晶FPGA将PWM控制精度从FPGA应用常见的10ns~5ns的水平提升到了1ns的脉宽和相位精度,精准可控,且资源消耗极低。

【产品】内置24992逻辑单元的低功耗FPGA器件SL2-25E/V,嵌入块存储容量9Kbits

西安智多晶微电子有限公司的Sealion(海狮)SL2-25E/V FPGA器件,建立在一个优化的低功耗工艺基础之上,并提供最低的功耗,通过最低的成本实现较高的功能性;适用于对无线、有线、广播、工业用户以及通信等行业中的低成本的小型应用。

【产品】具有12,032逻辑单元的SL2-12E FPGA器件,核电压1.2V或3.3V

西安智多晶的Sealion(海狮)SL2-12E/V FPGA器件,建立在一个优化的低功耗工艺基础之上,并提供最低的功耗,通过最低的成本实现较高的功能性。FPGA器件旨在用于大批量、成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的应用要求。

【选型】西安智多晶(XIST)FPGA/CPLD可编程逻辑器件选型指南

目录- Seagull1000/Sealion2000/Sealion合封系列

型号- SL2D-25E,SEALION2000,SL2E-5E,SEAGULL1064C,SEAGULL1000,SG1128V,SEAGULL1256C,SEAGULL1064V,SG1064V,SEAL 5000,SG1256V,SEAGULL1256V,SL2-12E,SL2S-25E,SEAGULL 1000,SG1128C,SG1064C,SL2-25E,SL2S-12E,SL2-7E,SL2-5E,SEAGULL1128C,SL2E-7V,SEALION 2000,SG1256C,SEAGULL1128V

SA5Z-30 FPGA 器件概述

描述- 西安智多晶微电子有限公司的SA5Z-30系列FPGA器件采用28nm工艺,具备丰富的逻辑资源、高性能可编程逻辑单元、低功耗特性、嵌入式和分布式存储、高性能灵活的I/O单元以及合封DDR2/3 SDRAM存储。适用于无线通信、工业控制、图像处理、人工智能、数据处理中心及云信息等行业。

型号- SA5Z-30-D3-U256,SA5Z-30,SA5Z-30-D0-U324,SA5Z-30-D1-U213,SA5Z-30-D2-U256,SA5Z-30 系列,SA5Z-30-D2,SA5Z-30-D0-8U324C,SA5Z-30-D3,SA5Z-30-D0,SA5Z-30-D1

西安智多晶发布软件无线电评估板,基于28nm FPGA芯片SA5Z-30并搭载ECR8661 RF收发器助力研发

为了让无线通信客户更方便评估智多晶FPGA芯片以及国产RF Transceiver,西安智多晶联合智锐星科技为客户打造了一个专业的软件无线电(SDR)评估板,可用于客户前期的项目预研。评估板的核心器件是28nm FPGA芯片SA5Z-30。

【产品】基于智多晶SL2-25E FPGA芯片的软件无线电(SDR)评估板,适用于项目开发初期验证、教学及培训

为了更好让无线通信客户评估智多晶FPGA芯片,西安智多晶为客户打造了一个专业的软件无线电(SDR)评估板,可用于客户前期的项目预研,其核心器件是西安智多晶的SL2-25E FPGA芯片,F256封装。这个评估板卡非常适合小带宽、低成本的通信项目,专网或公网的应用。

SA5Z-30 FPGA 数据手册

描述- 本资料为西安智多晶微电子有限公司的SA5Z-30 FPGA数据手册,详细介绍了SA5Z-30 FPGA的特性和应用。该器件属于Seal(海豹)5000系列,基于28 nm工艺,提供丰富的逻辑资源、高性能可编程逻辑单元、灵活的片内时钟、嵌入式和分布式存储、高性能I/O单元等特性,适用于无线通信、工业控制、图像处理、人工智能等领域。

型号- SA5Z-30-D1-U213,SA5Z-30-D2-U256,SA5Z-30-D2,SA5T-325,SA5Z-30-D3,SA5Z-30-D0,SA5Z-30-D1,SA5T-100,SA5T-366,SA5Z-50,SA5Z-30,SA5Z-30-D0-U324,SA5Z-30-D0-8U324C

Seal(海豹)SA5Z-30 FPGA 产品手册

描述- 西安智多晶微电子有限公司发布的SA5Z-30 FPGA产品手册详细介绍了该系列FPGA的特性、资源、结构和封装。该系列基于28nm工艺,具备丰富的逻辑资源和高性能可编程逻辑单元,适用于无线通信、工业控制、图像处理等领域。

型号- 海豹5000系列,SA5Z-30-D2,SA5Z-30-ES,SA5Z-30-D0-UBGA324,SA5Z-30-D0,SA5Z-30-D1,SA5Z-30-D1-UBGA213,SA5Z-30-D2-8U213C5,SA5Z-30,SA5Z-30-D1-8U213C4,SA5Z-30-D2-8U213C6,SA5Z-30-D2-UBGA213,SEAL 5000系列,SA5Z-100-D1-8U324C,SA5Z-30-D0-8U324C6,SA5Z-30 系列,SA5Z-30-D1-8U213C,SA5Z-30-D2-8U213C

Sealion(海狮)2000 系列 FPGA数据手册

描述- 西安智多晶微电子有限公司的Sealion 2000系列FPGA是一款基于55nm工艺的低功耗FPGA,适用于低成本、低功耗应用。该系列FPGA具备丰富的逻辑资源和存储器模块,支持多种I/O标准和配置模式,并提供内置Flash和SDRAM等功能。

型号- SL2D-25E,2000S,SL2E-5E,SEALION 2000S,SL2E-5E-8M121I,2000E,SL2-12E-8F256C,SEALION 25K,SL2-18,SEALION 5K,2000E 系列,SL2S-25 V,SEALION 2000E 系列,SL2-12,SL2S-12E,2000,SL2E-7V-8U400I,SL2S-25 E,SL2-25 V,2000 系列,SL2E-7 E,SL2E-7V,SL2E-5 E,SEALION 2000,SL2S-12E-8E176C,SL2S-12 V,SL2E-5E-8N84I,SL2E-7 V,SL2-25 E,SL2D-25 V,SL2E,SL2S-25,SL2S-12 E,SL2D,SL2S-12E-8F256C,SEALION 2000 系列,SL2-12 V,SL2-5,SL2S-25E-8U213C,SL2D-25 E,SL2-7,SEALION 7K,SL2E-7E,SL2S-25E,SL2S,SL2-25E-8U324C,SL2-12 E,SL2S-12,SEALION 12K,SL2,SEALION 2000D,SEALION 2000E,SL2-25

SA5Z-30 FPGA(车规级)数据手册

描述- 本资料为西安智多晶微电子有限公司的SA5Z-30 FPGA(车规级)数据手册,详细介绍了该款FPGA的特性和资源。SA5Z-30 FPGA基于28 nm工艺,具有丰富的逻辑资源、高性能可编程逻辑单元、灵活的片内时钟、低功耗设计等特点,适用于无线通信、工业控制、图像处理、人工智能等领域。

型号- SA5Z-30,SA5Z-30-D0-8U324C,SA5Z-30-D0

智多晶FPGA选型表

FPGA选型参数:28nm hpc+工艺,自 LUT6 架构,嵌入MCU,30K~325K LUT4,内置100/200/400个25X18/18X18/9X9专用乘法器,硬核 Memory DDR controller,PCIe-Gen2/3,1Mbps/s 采样,12bit ADC,支持 DDR4-1866Mbps,LVDS 1.25Gbps,Serdes 3.1Gbps~12.5Gbps,3D 合封 DDR2、DDR3 、DDR4

|

产品型号

|

品类

|

封装

|

LUTS

|

Flip-Flops

|

Slices

|

CLB

|

Flash(Kbits)

|

Max Distributed Ram (Kbits)

|

Embedded memory

(Kbits)

|

Number of Block SRAM(9 Kbits/block)

|

Embedded

18x18multipliers

|

General purpose PLLs+DLLs

|

Global Clock Networks

|

User I/O Banks

|

Max user I/O(注1)

|

|

SL2E-5E-8W81I

|

FPGA

|

81-ball WLCSP,0.4mm

|

5040

|

5040

|

2520 (LUT:FF=1:1)

|

630

|

512

|

40

|

108

|

12

|

16

|

2+2

|

16

|

6

|

199

|

选型表 - 智多晶 立即选型

Sealion(海狮)SL2E-7E/V FPGA产品手册

描述- Sealion(海狮)SL2E-7E/V FPGA是由西安智多晶微电子有限公司开发的一款低功耗、高性能的可编程逻辑器件。该器件采用55nm工艺制造,具备丰富的逻辑资源和I/O单元,适用于各种低成本、低功耗的应用。

型号- SL2E-7V-UBGA400,SEALION 2000 系列,SL2E-7V,SEALION 2000,SL2E-7V-E144,SL2,SL2E-7E,SEALION SL2E-7E,SEALION SL2E-7V,SL2S-12E-8F256C,SL2E-7V-U256

Device UID_IP 用户指南

描述- 本指南介绍了西安智多晶微电子有限公司的Device UID\_IP,一种用于FPGA器件的唯一标识符生成和读取的IP核。指南详细说明了UID的特性、系统框图、接口描述、使用说明以及IP生成过程。UID作为器件的DNA,具有不可修改的特性,用于安全性和唯一性验证。指南提供了接口时序图和使用说明,以及如何在HqFpga工程中生成和使用该IP核。

型号- SL2S-22E,SL2E-5E,SA5T-100,SA5T-200,SA5T-366,SEALION 2000 系列,SA5Z-50,SL2E-2V,SEAL 5000,SL2E-4V,SEAL 5000 系列,SL2E-7V,SEALION 2000,SA5T-50,SL2-22E

电子商城

服务

可定制卫星定位天线协议:GPS、北斗、伽利略 (Galileo) 、格洛纳斯(GLONASS)卫星定位;增益:5~25dBi;驻波比:≤1.5;接口连接器:IPEX:1~5代IPE、SMA接口/公头等。

最小起订量: 1000 提交需求>

可定制B-Flon极细同轴线导体规格:AWG36~48,特性阻抗:50±5Ω,工作温度:-40~90℃,静电容量:105-120PF/m,减衰量:10MHZ:0.5-2.6db/m;100MHZ:1.6-4.2db/m,阻燃UL:VW-1规格。

最小起订量: 50000m 提交需求>

登录 | 立即注册

提交评论