【经验】发挥氮化镓器件设计的最高性能的关键技术:栅极驱动器、PCB布局与设计、散热和EMI

GaN晶体管,特别是氮化镓场效应晶体管(eGaN FET),它的行为与老化的功率MOSFET非常相似,因此,功率系统工程师可以利用他们的设计经验,充分发挥氮化镓器件的最高性能。本文中将会与首次使用GaN的设计师分享在设计时通常会遇到的问题。

一、栅极驱动器

氮化镓晶体管的行为与功率MOSFET器件的行为相似,但它的开关速度和功率密度高很多。本节将重点介绍如何驱动氮化镓晶体管,从以实现最高的性能。对于eGaN器件,栅极驱动器的考虑因素包括:

对于低侧驱动器和特别是高侧驱动器,都需要调节栅极驱动器电源电压,从而避免晶体管的栅极出现过压的情况。驱动器件时,要导通电阻没有明显增加的理想范围是5 V至5.5 V,绝对最大值为6V。

同样,栅极驱动器的设计应尽量减小VDD电源电容与功率器件(漏极和源极器件)之间的栅极功率环路电感。这将栅极驱动器的上升时间减至最少,并使得驱动器的di / dt可以最大化。

最后,在设计栅极驱动器时,设计师应假设驱动器接地与控制器接地的差异可以很大,而且输入逻辑引脚必须不受噪声引致的逻辑状态所影响。

我们需要关注栅极驱动器的要求,但实际上不用担心,因为近年来,适用于增强型氮化镓晶体管的栅极驱动器集成电路的生态系统一直以来以指数级进化。多家供应商的驱动器,包括德州仪器、uPI半导体、Silicon Labs、pSemi等,都可以满足氮化镓晶体管所需的驱动器的各种要求,而且许多驱动器更特别针对基于氮化镓器件的各种关键应用。例如说,EPC公司和Renesas公司的耐辐射并与氮化镓器件兼容的栅极驱动器,可支持宇航和高可靠性应用。此外,将驱动器和功率器件集成,包括模块和单片器件。这些器件进一步简化了设计和组装,并且可以提升性能。

二、最优的布局技术

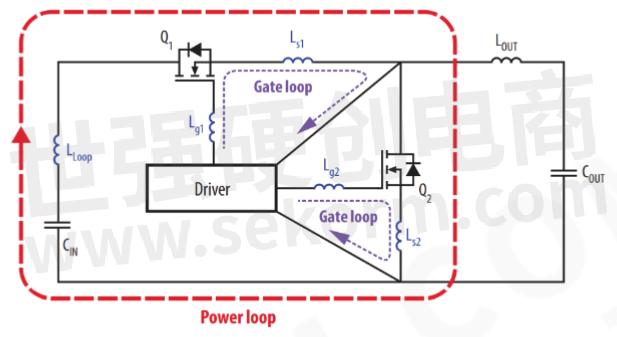

由于氮化镓器件的开关速度快,因此增加寄生电感、影响性能。以下是具体的布局技术和如何把这些寄生电感减至最小的方法。要把所有元件的电感同样地减至最小是不可能的,所以按重要性、顺序解决各种电感:共源电感、高频功率环路电感和栅极驱动环路电感。最后将展示一个最佳布局的示例,从而实现eGaN FET的最佳性能。

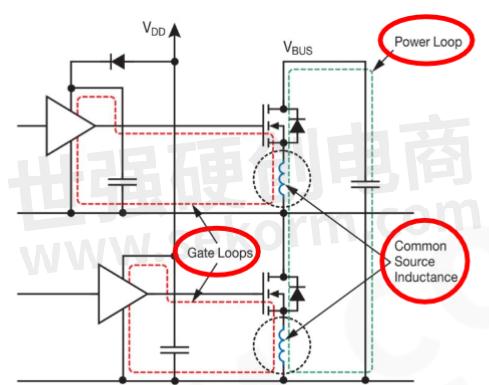

当使用半桥配置,让我们看看电感的来源。在半桥配置,需要考虑三种主要环路电感:

1)两个功率开关器件并配以高频总线电容的高频功率环路;

2)栅极驱动器、功率器件和高频栅极驱动电容的栅极驱动环路电感;

3)共源电感被定义为在栅极环路和功率环路常见的环路电感。

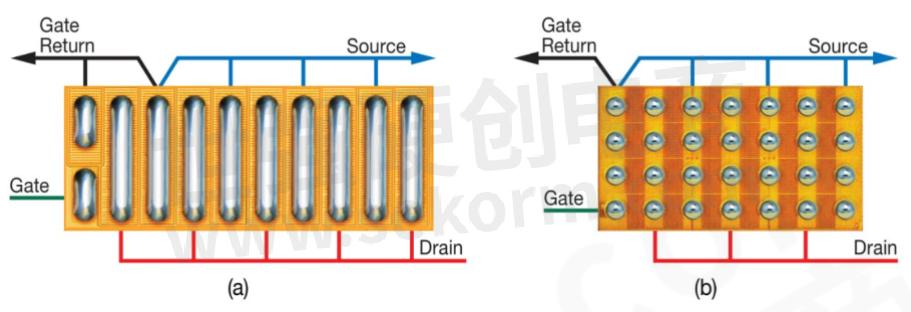

增强型氮化镓晶体管采用晶圆级芯片级封装,其端子采用焊盘栅格阵列(LGA),如这里的左图(a)所示;或球形栅阵列格式(BGA),如右图(b)所示。然后,如这里所示,通过使电流沿正交方向流动,将栅极和电源环路的布局分开。将漏极和源极端子交织在器件的一面,会产生许多带有相反电流的小环路,这些环路会通过磁场自抵消而降低总体电感。

eGaN FET的最大允许栅极电压为6V,比建议的5V驱动电压高一伏。这一伏需要相对准确的栅极驱动电源,以及限制eGaN FET与栅极驱动器之间的电感,因为该电感会导致栅极的电压过冲。栅极环路中的电感会直接限制器件的开关速度,需要留意把该电感最小化,从而实现最高的效率。

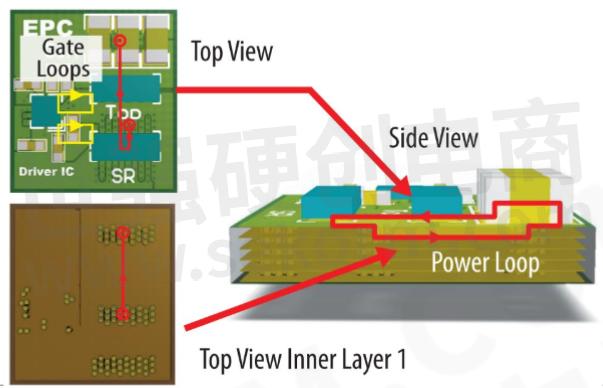

通过利用PCB的内层形成优化回路,从而实现最小的电源环路和栅极环路电感。去耦电容放置在最接近高侧晶体管的漏极位置。利用PCB通孔在第一内层将电容接地端子与低侧电源连接,这层特意使用纤薄的电介质,从而保持较低的电感。这里显示了这种最佳布局技术的示例。现在,让我们看看在实例中,可以实现的效率。

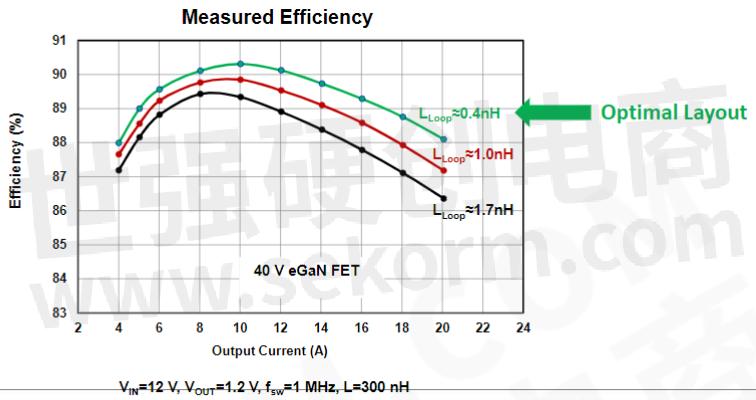

布局电感越低、效率越高。采用最佳的布局,源环路电感可以从1.7 nH降至0.4 nH,而且在1 MHz降压转换器可以提升峰值效率达一个百分点,或功耗降低了约10%。最佳的布局不仅可以改善eGaN FET的电路性能,还可以减少漏极电压过冲,从而降低EMI。

三、PCB设计

本节分享设计PCB时要考虑的各项因素。宜普电源转换公司(EPC)的晶圆级芯片级封装使得功率转换可以实现前所未有的性能。大部分这些元件使用最小间距(小至400 μm),这意味着正确的PCB脚位设计,对氮化镓器件的组装至关重要。本节中根据数据表内提供的信息,为EPC元件的正确脚位提供设计指南。会讨论影响eGaN FET和IC的PCB设计的各个关键部分:首先是金属铜垫设计,接下来是丝印板设计,最后是通孔。

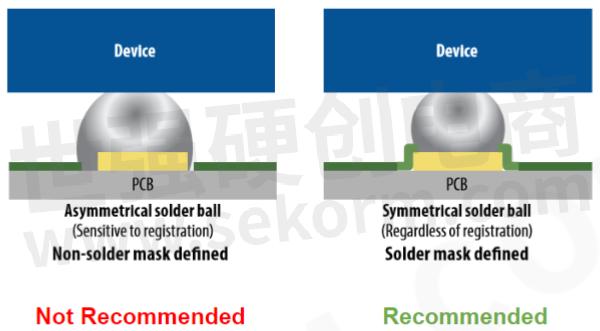

从数据表内提供的信息,可以找到每个EPC元件的完整、由阻焊层定义的焊盘图案,该图案定义了阻焊层的设计。注意没有定义的是金属铜垫。正确的、由阻焊层定义的焊盘设计要求金属铜垫的尺寸在x和y方向都较大,包括制造对准公差。该公差解释阻焊层和金属铜层之间的任何未对准的情况。可以从右图看到,由阻焊层定义的焊盘如何通过确保焊接后,焊球可以对称,从而降低机械应力。相反,使用非阻焊层定义的脚位,可导致不对称的焊球,这是因为金属铜层和阻焊层之间,不可能100%对准,如左图所示。

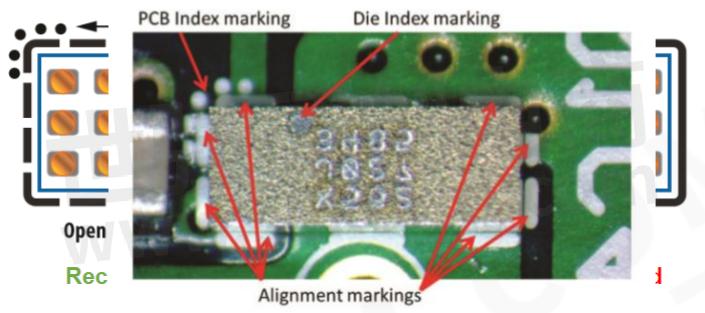

EPC器件的丝印板设计有两个目的:1)指出放置芯片的位置和方向;2)指出引脚1的方向。

为了确保正确放置芯片,应遵循电路板组装商所建议的丝印层至金属铜层对位公差。EPC推荐的丝印板设计应包括:4个角对齐标记,勾划出元件形状;用短划线绘制的线;专有引脚用的标识符。不推荐右图所示的丝网坝的原因,是因为围绕器件的实线矩形,可防止助焊剂在回流过程中从芯片流出,这可能会形成助焊剂坝,使得焊剂停留在器件的底部。这会增加形成枝晶的可能性。这里的照片显示了正确的丝网板设计的示例。

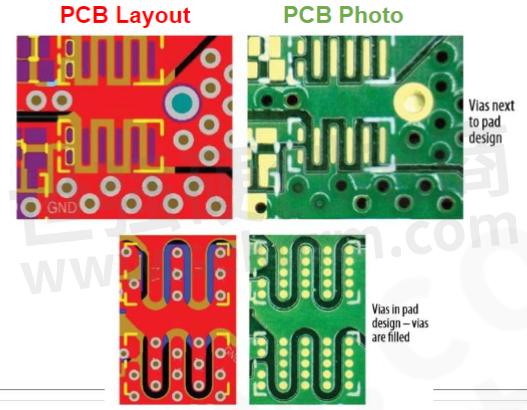

由于eGaN器件的尺寸小和它对电气性能的要求,通孔成为PCB设计的一个重要部分。某些设计可能限制通孔的最小尺寸,这意味着无法在器件焊盘下方放置通孔,而是必须将通孔放置在器件的旁边,例如这里所示的设计。应该全部复盖(由阻焊层覆盖)靠近芯片的通孔,从而防止焊料在回流过程中,流到通孔,并且防止由于芯片附近暴露的铜所引起的电压间隙问题。在某些情况下,可能需要在器件的焊盘下方放置一个过孔。如果需要这样做,则必须填充并覆盖通孔,从而防止在回流期间,将优化焊球高度所需的焊料,流入孔中。这里的照片显示了器件下方的通孔设计。我们从右图可以清楚地看到,场效应晶体管的焊盘已被镀覆,不会看到通孔。

四、散热技术

本节主题是热管理,这是我们经常遇到的问题,因为EPC器件非常微型!在本节中,将分享采用芯片级封装的氮化镓器件的热模型,然后讨论采用散热器,接下来将展示适用于整个基于氮化镓器件的功率转换系统的简单散热管理解决方案,最后分析和展示散热器对性能的影响。

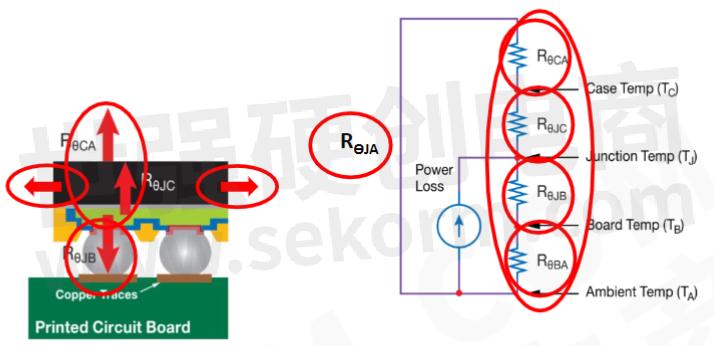

对于采用芯片级封装的器件,器件是上下倒装和它的背面(“外壳”)变为顶部。这里的横截面图显示了采用芯片级封装的氮化镓晶体管的两种散热通路:

1)第一种散热通路是热量向下穿过球栅或栅格阵列焊盘、焊点并进入PCB。然后,热量可以直接从PCB散至周围环境的空气中,或从PCB另一侧的散热器的散热通孔散出。

2)第二种散热通路是通过芯片的顶部或侧面散热。热量可以通过芯片的顶部及侧面,以辐射或对流方式散热。

现在,看看这里的横截面的热模型。结至外壳热阻(RθJC)被定义为从芯片表面到封装外壳的电阻,这里是芯片级GaN晶体管衬底顶部的表面。结至电路板热阻(RθJB)是指从晶体管的表面到PCB上的铜走线、穿过焊球或焊条的热阻。与这两种电阻一起的,有电路板至环境电阻,以及外壳至环境电阻,它们与RθJB和RθJC相比,是大电阻。当两种散热通路并行时,其总热阻就是结至环境电阻(RӨJA)。

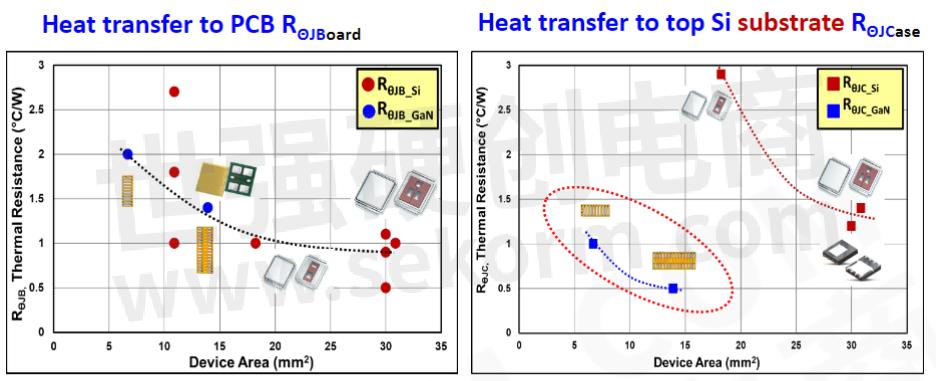

图中显示了硅MOSFET和采用芯片级封装的氮化镓晶体管示例的热阻。水平轴显示器件的面积,而垂直轴显示热阻。如图所示,圆圈所示的结至电路板热阻,与器件的尺寸呈反比。但是,由于采用了芯片级封装,氮化镓晶体管的结至外壳热阻(在右图的正方形所示)低很多,这表明与硅MOSFET器件相比,采用芯片级封装、其散热器连接至顶部的氮化镓晶体管,可实现低得多的结至环境热阻,如红色正方型所示。

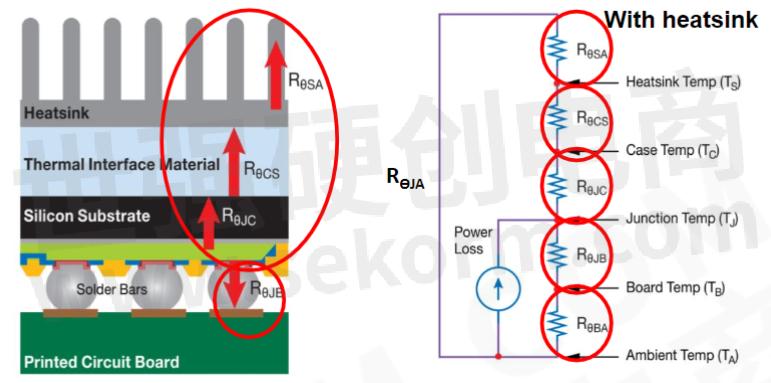

与大多数转换器设计一样,采用散热器可提高氮化镓晶体管的散热性能,从而降低结与周围环境空气之间的热阻。这里的横截面图显示采用芯片级封装的氮化镓晶体管,仍然可以从焊条或焊球将大量热量散到所连接的金属铜区域和PCB的相邻层。散热器和热界面材料可以直接与晶体管外壳的顶部连接,如这里所示,从而提供了更直接的散热通路、避免增加PCB通孔的热阻。

现在看看等同横截面的热模型。当采用散热器后,仍然具有结至外壳热阻(RθJC)和结至电路板热阻(RθJB),以及电路板至环境热阻。有了散热器后,增加了外壳至散热器电阻(RθCS)和散热器至环境电阻(RθSA)。良好的散热器设计,其散热器至环境电阻值(RθSA)是非常小的。

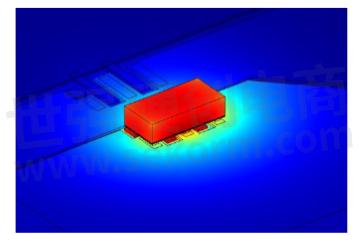

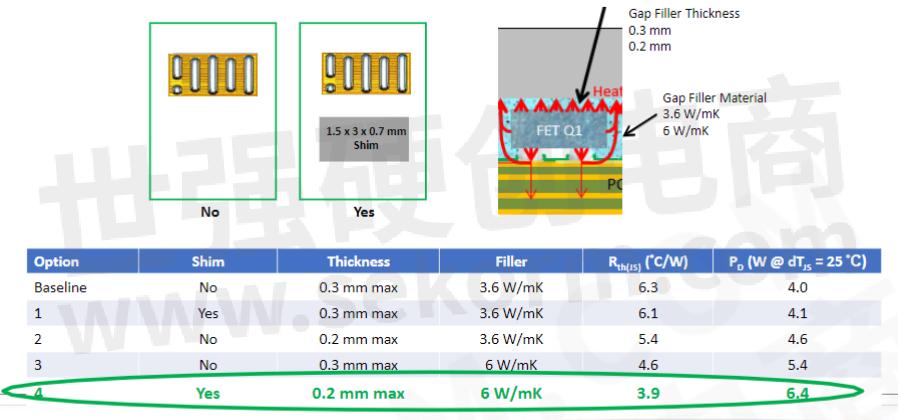

现在看一个实例。这里显示组装在采用散热器的PCB上的单个场效应晶体管。

这个是基线示例,采用一个4平方毫米的芯片、添加填充物、在最差的情况下采用距离散热器最短的间距(0.3 毫米),功耗为6瓦特时,所得结果是每瓦6.3°C。从热图像可以看到,最高温度是137.8°C,散热器预设为100°C,或在6瓦特时,温度上升了37.8°C。

接下来是构建散热系统的几种方法。在绿色框中,展示了带垫片和不带垫片的器件的外观。垫片由金属铜制成。尺寸为1.5 x 3 x 0.7毫米,或与器件的尺寸相约。安装垫片在器件的旁边。右边的横截面显示装贴器件的外观。器件的上方有一个灰色的散热器,而将间隙填充物从0.2毫米改为0.3毫米,并且将使用3.6 W / mK和更好的6W/mk来改变间隙填充物。这个列表显示每个变量对系统的影响。首先是对于基线系统,在没有垫片、最厚的厚度、使用最差的填充物的情况下,系统的热阻为6.3°C / W。如果需要限制器件的最高上升温度仅为25°C,那么它可以耗散4W的热量。在最佳的情况下,即是列表中的第四种系统,添加了垫片、厚度改为0.2 毫米、使用改良版的6W / mK间隙填充物后,该系统的热阻为3.9 °C / W,代表用户可以在这个小巧的器件中,在结温升了刚刚25°C之前,已经耗散6.4 W的热量。

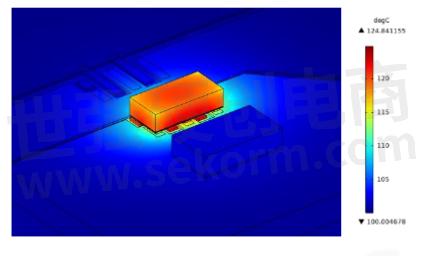

这是热图像。添加了1.5 毫米x 3毫米x 0.7毫米尺寸的垫片、使用6 W / mK的间隙填充物、器件顶部至散热器的间距为0.2毫米。您以看到,最高上升温度为125°C,而散热器保持在100°C。

五、EMI

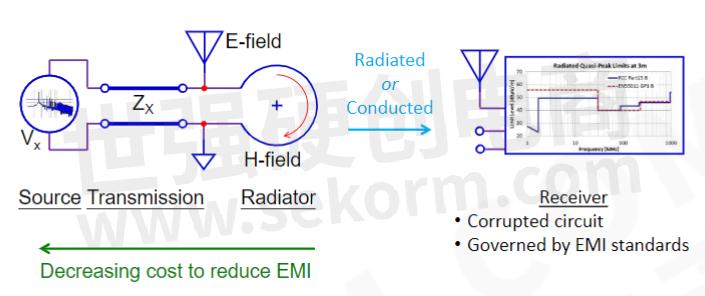

由于eGaN器件的开关速度超快速,那么EMI会怎么样?本节将概述EMI系统,然后讨论可选的特定设计所产生的EMI和传播的影响,例如布局、上升/下降时间和反向恢复。EMI系统包括几个组件:

1)首先是以各种形式产生的能量,例如晶体管的开关事件。-能量需要传输路径,例如PCB上的导体。

2)这些传输路径可以形成电容的极板,在电容中电压可以像电场一样辐射,或可以在回路中使电流像磁场一样辐射。环路也可以辐射电场,或相反地,电容极板可以辐射磁场。

3)无论传输方式和路径是什么,都必须接收EMI能量。在直接传输的情况下,它被称为传导EMI,而对于电/磁场,它被称为辐射。

4)EMI系统中的最后一个组件是接收器,接收器被定义为损坏了的电路,导致不良行为。接收器电路可以是包含源电路或第三方电路的相同电路,例如无线电接收器。对于第三方接收器电路,防止EMI引起的不良行为受EMI标准规范。

5)采取符合规范标准、防止电路损坏、降低EMI的措施,无可避免地会增加系统成本,而在越接近产生EMI的地方采取降低EMI的措施,系统成本就可以越低。

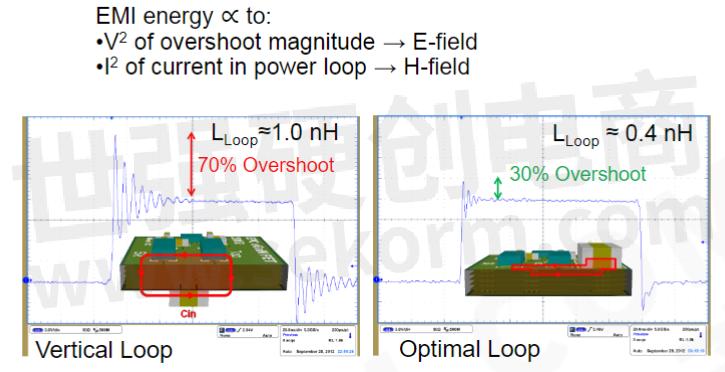

在这里EPC将布局视为一种没有成本、可降低EMI的方法。设计转换器时,布局具有固有的寄生电感。在这个同步降压转换器示例中,显示了在上升沿硬开关切换之后,环路电感对开关节点的电压过冲的影响。左图的环路电感为1 nH,导致出现振铃的70%峰值电压过冲。右图展示400 pH环路电感、30%峰值电压过冲并产生振铃。产生的EMI与电压过冲幅度的平方值成正比,并且从导体传播电场,形成接地电容。环路电感还将在振铃期间传导电流、产生相应的EMI,该EMI与电流幅度的平方值成正比,该电流通常随功率环路电路发出的H场传播。将功率环路电感减小一半,可将EMI降低四分之一。

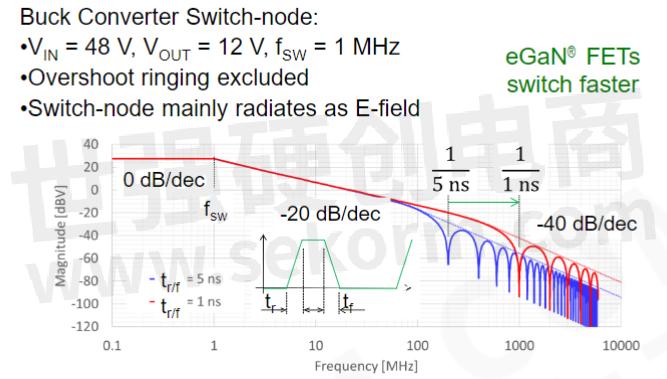

eGaN FET的开关速度比MOSFET器件快,而许多人问及这如何影响EMI。请注意,如果该器件的开关速度比另一种器件快,EMI能量就根本没有变化,只是光谱含量变了。看看这个例子,它是工作在1 MHz频率、分别在5 ns和1 ns的两种开关瞬态条件下的48V/12 V降压转换器。这图显示了这两种瞬态情况的开关节点电压的频谱,其中上升沿时间被设置为与下降沿时间相同,并且不包括电压过冲和振铃。从图中可以看到,在90 MHz时,频谱含量已经衰减了42 dB。在5 ns瞬态情况下,需要留意的频率是200 MHz或1/5 ns;而在1 ns瞬态情况下,需要留意的频率是1 GHz或1/1 ns。在这些频率之上,频谱幅度的降低速率为40 dB/dec,这意味着从开始就需要非常低的滤波要求,因此解决之前讨论的电压过冲振铃更为重要。开关节点形成接地电容的极板,这是第二极板,使得这种EMI电场辐射占优势。

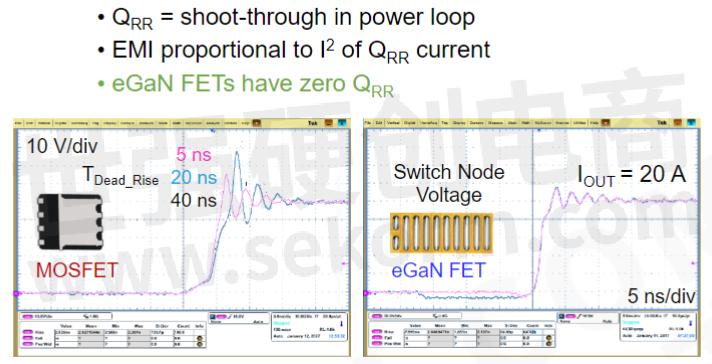

这里以硬开关降压转换器为例,讲解常被忽略的反向恢复对EMI的影响。反向恢复表现为电源环路中的直通电流,而如前所示,电源环路中的电流会导致电压过冲和振铃。反向恢复会增加电源环路中的能量,从而为EMI噪声源添加能量,该能量与反向恢复电流的平方值成比例。该反向恢复电流可以比降压转换器的电感电流高出数倍。左边的波形显示了基于MOSFET器件的降压转换器的电压过冲和振铃,其死区时间分别为5 ns、20 ns和40 ns,而在相同工作条件下,右边展示出等效氮化镓场效应晶体管的波形图。从右边的波形图可以看到,死区时间的变化对氮化镓场效应晶体管没有影响,因为氮化镓晶体管没有反向恢复。

总而言之,氮化镓场效应晶体管(eGaNFET)和IC与EMI兼容。通过采用简单的布局技术可以显着降低EMI,从而在不需增加成本的情况下,降低EMI。较高的开关高压摆率会导致频谱含量发生变化,但不会增加EMI能量。在较高的频率下,由于降低EMI的技术更高效,从而确保以较低的成本降低EMI。最后,eGaNFET和IC具有零反向恢复,因此在硬开关转换器中,可产生较少的EMI能量。

六、总结

本文中分享了一些关键的设计技术,从而发挥基于氮化镓器件的设计的最高性能。讨论了要注意栅极驱动器的要求,详细介绍了被证实为最佳的布局技术,可减少过冲和提高效率,重点介绍了关键的PCB设计技术,是可靠、高良率的PCB设计,让用户易于组装采用具有低电感、小占板面积、芯片级封装的氮化镓(eGaN)晶体管,接下来展示了一种简单且不昂贵的散热系统,让用户发挥微型氮化镓(eGaN)器件的最高性能,最后证明了通过采用简单的布局技术并利用eGaN器件固有的性能优势,尽管eGaN器件的开关速度更快速,它的EMI比MOSFET器件更低。

- |

- +1 赞 0

- 收藏

- 评论 2

本文由无名指转载自EPC,原文标题为:EPC转载,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【经验】eGaN FET EPC2016C开发板EPC9126的调试技巧分享

EPC9126是EPC公司推出的针对eGaN FET EPC2016C的demo板,在调试过程中经常会碰到各种问题,本文就调试步骤做一下总结。1、确认5V电源是否正确。2、确认信号发生器PWM信号是否正确,符合要求的应该是5V幅值,占空比为50%的输入信号。3、J8端信号确认,主要是确认开发板U3/U5芯片没有损坏。

【经验】EPC eGaN FET和eGaN IC PCB封装设计指南

一个良好的PCB封装设计对于GaN器件的一致性和可靠性是很重要的。本文是根据数据手册为EPC器件设计正确封装的指导原则——以EPC2016C和EPC2045为例,分别从LGA和BGA封装来完成介绍。

How to Design a 12V-to-60V Boost Converter with Low Temperature Rise Using eGaN FETs

This Talk EPC will examine the design of a 12V to 60V, 50W DC/DC power module with low temperature rise using eGaN FETs in the simple and low-cost synchronous boost topology.

BRC Solar Selects EPC 100V eGaN FETs for Next Generation Solar Optimizer

Designing EPC‘s EPC2218 100V FETs into BRC Solar GmbH‘s next generation M500/14 power optimizer has enabled a higher current density due to the low power dissipation and the small size of the GaN FET making the critical load circuit more compact.

【应用】eGaN FET EPC2051助力激光雷达发射端高功率纳秒级别脉冲设计

在激光雷达的发射链路中,为实现雷达高分辨率的设计,需产生高功率、纳秒级别的激光脉冲。要达到这样的设计要求,普通MOS不能满足要求,需要采用GaN 搭配高功率Laser器件进行实现。EPC2051是EPC公司生产的氮化镓场效应晶体管(eGaN FET),已经成功的应用在激光雷达上。

EAS egallium氮化物放大器2.1评估套件Class-D高性能egallium氮化物FET放大器平台

描述- 该资料介绍了EAS eGaNAMP 2.1评估套件,这是一款高性能的eGaN FET放大器平台。该平台包括eGaNAMP2016放大器模块、D2Audio DAE-3HT/DAE-6控制器/数字信号处理器,支持立体声、2.0和2.1通道音频配置。平台提供高保真音频参考,支持多种音频输入源接口,包括立体声模拟音频输入、光S/PDIF数字音频输入和AES-EBU数字音频输入。此外,该平台具有完全可编程的DSP前端,支持USB接口进行编程,并兼容D2Audio DAE-3、DAE-3HT和DAE-6 IC。

eGaN FETs Are Low EMI Solutions!

GaN FETs can switch significantly faster than Si MOSFETs causing many system designers to ask − how does higher switching speeds impact EMI? In this blog, EPC discusses simple mitigation techniques for consideration when designing switching converter systems using eGaN® FETs and will show why GaN FETs generate less EMI than MOSFETs, despite their fast-switching speeds.

【产品】EPC新型200V eGaN FET的性能相比传统Si MOSFET提高了一倍

EPC推出新型200V eGaN FETs(氮化镓增强型功率晶体管),相比于传统的硅功率MOSFET的性能提高了一倍。新第五代设备的尺寸仅为上一代产品的一半,栅电极和源电极之间的距离有所减小,金属层的厚度增加等诸多改进使第五代FET的性能提高了一倍。

【应用】eGaN FET EPC2007C成功助力16线、32线等多线激光雷达发射端纳秒级别脉冲设计

在激光雷达的发射链路中,为实现雷达高分辨率的设计,需产生高功率、纳秒级别的激光脉冲。要达到这样的设计要求,需要采用GaN搭配高功率Laser器件来实现。EPC2007C为EPC的氮化镓场效应晶体管(eGaN FET),已经成功的应用在16线、32线等激光雷达设计上。

电子商城

登录 | 立即注册

提交评论