【经验】高性能抖动衰减时钟倍频器Si5347、Si5346在DCO应用上的增益和输出频率的计算

Si5347、Si5346是SILICON LABS的一款集成了DSPLL的高性能抖动衰减时钟倍频器,每个DSPLL都可以在任何器件的输出上提供低抖动时钟信号,以及提供100fs以下典型抖动性能的任意频率转换。同时,还可通过串行接口对非易失性存储器进行在线编程,因此可始终以已知配置启动。通过改变单独的反馈M分频器,可在Si5347、Si5346上实现DCO数控振荡器的功能,实现方式有下面两种方法。

1.通过串口直接写入M分频器(DSPLL反馈)寄存器的M_NUM_PLLz。

2.使用频率递增(FINC)和频率递减(FDEC)引脚或寄存器位更改M_NUM_PLLz,由内部FSTEPW参数定义的小步长M分频器的长度。

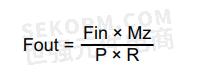

而输出频率的计算如图1的定义,其中z是PLL索引A,B,C或D。

图1

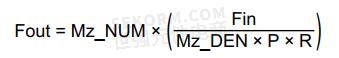

将Mz替换为Mz_NUM / Mz_DEN可得图2的表达式,其中P是所选输入的P分频器值,R是通过写入Mz_NUM控制的输出时钟的输出R分频器值,Fin是进入PLLz的时钟输入频率(以Hz为单位),Fout表示连接到DSPLLz的所有输出时钟的频率。

图2

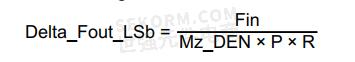

当M_DEN保持不变时,M_NUM将会被更改,且输出频率变化将是线性的。但如果改变Mz_DEN,输出频率变化将不是线性的。所以,将M_NUM移到等号左侧,得到图3的斜率表达式,Delta_Fout_LSb是以Hz/ Mz_NUM作为最低有效位(LSB)的分辨率。该斜率是LSbit变化的DCO增益。

图3

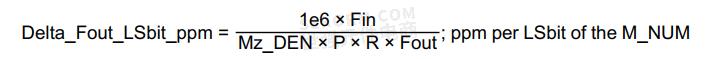

DCO增益也可以表示为M_NUM/LSB ppm,如图4所示,其中Fout和Fin以相同的单位表示。

图4

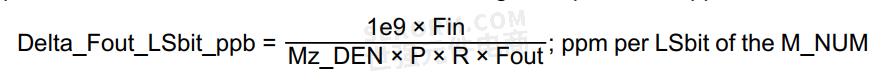

同样,以M_NUM/LSB ppb表示的DCO增益为,如图5所示。

图5

到这里,我们就得到了图3,图4,图5这三个关于DCO增益的重要公式。假如需要配置PLLA的输出频率,只需要配置Fin Fout的频率,所选输入的P分频器值和输出时钟的输出R分频器值,以及MA_DEN 的数值即可得到Delta_MA_Num。将这个数值乘以原始的MA_NUM即可得到最新的Delta_MA_Num,再将原始的MA_NUM减掉最新的Delta_MA_Num即可得到要写入到Si5347、Si5346的 Ma_NUM,并且在每次写入 Ma_NUM后,都要写入一次0x0420 = 1,这样M分频器才算是有效写入,进而产生DCO增益。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由小龙人翻译自Silicon Labs,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【经验】高性能抖动衰减器时钟芯片Si5326的频率配置问题解析及替代方案推荐

Si5326是Silicon Labs推出的基于第三代DSPLL专利技术的高性能抖动衰减器时钟芯片,最近有工程师在做设计时要求Si5326输入为25MHz时钟,2路输出分别是25.8MHz和27.5MHz的3.3V时钟信号,使用DSPLLsim配置时,发现无论该2路时钟位置如何调换,无论如何调整分频比,输出频点都不能同时实现整个两个频点的输出。本文就将解答这一问题并给出替代方案。

如何实现SI5342、SI5344和SI5345抖动衰减器锁相环动态调整?

Silicon Labs的超高性能抖动衰减器SI5342/SI5344/SI5345已经在通信客户中获得大量的应用。Silicon Labs SI5342/SI5344/SI5345时钟发生器内置Silicon Labs第四代专利锁相环DSPLL,自带I2C、SPI可编程接口,能够实现用户在线编程改变输出频率,实现在线调试和频率更新。本文讲述了实现抖动衰减器锁相环动态调整的方法步骤。

【经验】抖动衰减器Si5345如何匹配选择8K单端输入时钟信号?

Silicon Labs的Si5345的输入时钟最低频率刚好是8kHz信号,通常对于这个最低频率的处理,需要特别注意。很多应用时会直接采用直流耦合的方式进行匹配,但是对于Si5345来说,这个8k不能简单直接使用DC耦合。通常8kHz时钟信号在通信吕一般由两种,一种是正常的占空比40~60%之间的时钟信号,还有一种是占空比远远小于1%的窄脉冲时钟信号,这两种时钟信号的处理实际应用是完全不同的。

一文快速告诉你任意频率时钟抖动衰减器Si539x与Si534x的性能对比

Silicon Labs结合第四代DSPLL™和MultiSynth™技术推出了Si539x和Si534x两款任意频率时钟生成抖动衰减器,抖动极低,适用于要求严格的互联网基础设施,可降低各种定时应用的成本和复杂性。本文将重点介绍超高性能Si539x系列较之Si534x系列有了哪些提升。

Si5376 4-PLL任意频率精密时钟乘法器/抖动衰减器

Si5376是一款高度集成的4PLL时钟倍频器/抖动衰减器,适用于需要亚皮秒级抖动性能的应用。它具有以下特性:支持所有ITU G.709和自定义前向纠错比率;四个独立的DSPLL可以生成任意频率的同步输出时钟;提供几乎任何频率转换组合;自动/手动无中断输入时钟切换;可编程带宽范围从60Hz到8kHz;低抖动(典型值为350 fs rms);符合ITU-T G.8251和Telcordia GR-253-CORE OC-192抖动规格。

SILICON LABS - 4-PLL ANY-FREQUENCY PRECISION CLOCK MULTIPLIER/JITTER ATTENUATOR,4-PLL任意频率精密时钟倍增器/抖动衰减器,高度集成的4-PLL抖动衰减精密时钟倍频器,HIGHLY-INTEGRATED 4-PLL JITTER-ATTENUATING PRECISION CLOCK MULTIPLIER,SI5376,SI5376B-A-BL,SI5376-EVB,SI5376B-A-GL,MSPP,MULTI-SERVICE SWITCHES,ROADM,路由器,SYNCHRONOUS ETHERNET,LINE CARDS,P-OTS,线卡,载波以太网,多业务交换机,同步以太网,CARRIER ETHERNET,MUXPONDERS,MUXPONDERS公司,ROUTERS

【产品】芯科Si5381无线抖动衰减时钟倍频器开发套件Si5381A-E-EVB

芯科推出Si5381 无线抖动衰减时钟倍频器开发套件Si5381A-E-EVB 。利用 Si5381A-E-EVB 可轻松从 ClockBuilder Pro 设备配置转移至手动性能评估。其具有四个独立的输入时钟,以及总共12个带有4/2 PLL的输出。

Silicon Labs(芯科科技) Si5345, Si5344, Si5342系列抖动衰减器/时钟倍频器 参考手册

本资料为Si5345/44/42系列时钟倍频器家族参考手册,旨在为系统、PCB设计、信号完整性及软件工程师提供使用这些器件的技术信息。手册涵盖了DSPLL和MultiSynth技术的应用,支持任意频率的时钟生成,并提供编程接口和多种操作模式。资料详细介绍了器件的工作原理、功能特性、配置方法以及电路布局建议。

SILICON LABS - 晶体及时钟芯片,CLOCK MULTIPLIERS,时钟倍增器,抖动衰减器,JITTER-ATTENUATORS,SI5345A-B-GM,SI5344C-B-GM,SI5345D-B03700-GM,SI5345D-B04500-GM,SI5345B-B04564-GM,SI5344B-B04184-GM,SI5345D-D-GM,SI5345C-A-GM,SI5345B-B-GM,SI5344D-B-GMR,SI5345B-B04881-GM,SI5345D-B04831-GM,SI5344D-B-GM,SI5342D-B05470-GM,SI5345A,SI5345A-B-GMR,SI5345B,SI5345C,SI5345B-B05955-GM,SI5345D,SI5342A-B-GM,SI5345B-B05785-GM,SI5345D-B05731-GM,SI5342D-D-GM,SI5345A-A-GM,SI5345B-B05747-GM,SI5345D-B04501-GM,SI5348B-B05856-GM,SI5342B,SI5342C,SI5342D,SI5342B-B-GM,SI5345D-B04409-GM,SI5348B-B05083-GM,SI5344A-B-GM,SI5345B-B04823-GM,SI5345B-B05971-GM,SI5342C-D-GM,SI5345B-B00021-GM,SI5345B-B06003-GM,SI5348B-B05423-GM,SI5344B-D-GM,SI5342A,SI5345C-D-GM,SI5345B-B-GMR,SI5345D-B04493-GM,SI5345D-B04502-GM,SI5345D-B-GM,SI5345D-B05784-GM,SI5342C-A-GMR,SI5345B-D-GM,SI5345A-D-GM,SI5342A-D-GM,SI5345B-B04421-GM,SI534X,SI5348B-B05017-GM,SI5345A-B04313-GM,SI5345B-B04408-GM,SI5342D-B-GM,SI5345D-B04494-GM,SI5345D-B04528-GM,SI5345C-B-GM,SI5345B-B05825-GM,SI5344D,SI5342B-D-GM,SI5345D-B04834-GM,SI5345B-B04563-GM,SI5342D-B04694-GM,SI5344D-D-GM,SI5345A-B04313-GMR,SI5345A-B04957-GM,SI5344A-D-GM,SI5345D-B04830-GM,SI5345D-B05729-GM,SI5344B-A-GMR,SI5345D-B04410-GM,SI5345A-A-GMR,SI5345B-B03718-GM,SI5342D-B03814-GM,SI5344A,SI5345B-B03234-GM,SI5344B,SI5344C,SI5345B-B05786-GM,玩具,室内照明,个人代步工具,便携数码,手机相关,消费电子部件,通信设备,电脑,工业电子,电脑外设,个人娱乐,智能家居,可穿戴设备

Si5375 4-PLL任意频率精密时钟乘法器/抖动衰减器

Si5375是一款高度集成的4-PLL时钟倍频器/抖动衰减器,适用于需要亚皮秒级抖动性能的应用。它接受2 kHz至710 MHz范围内的输入时钟,并生成2 kHz至808 MHz范围内的输出时钟。该设备提供几乎任何频率转换组合,具有超低抖动的时钟输出。

SILICON LABS - JITTER ATTENUATOR,抖动衰减器,精密时钟倍增器,PRECISION CLOCK MULTIPLIER,SI5375,SI5375B-A-GL,SI5375B-A-BL,SI5375-EVB,ITU-T G.709 OTN自定义FEC,MSPP,协议,任意频率线路卡,MULTI-SERVICE SWITCHES,ROADM,路由器,10/40/100克,ITU-T G.709 OTN CUSTOM FEC,OC-48/192, STM-16/64,P-OTS,10/40/100G,OC-48/192、STM-16/64,载波以太网,多业务交换机,1/2/4/8/10G FIBRE CHANNEL,PROTOCOL, ANY-FREQUENCY LINE CARDS,CARRIER ETHERNET,MUXPONDERS,MUXPONDERS公司,GBE/10GBE同步以太网,ROUTERS,GBE/10GBE SYNCHRONOUS ETHERNET,1/2/4/8/10G光纤通道

Si5369任意频率精密时钟乘法器/抖动衰减器

Si5369是一款高精度时钟倍频器,适用于需要亚皮秒均方根抖动性能的应用。它接受2 kHz至710 MHz范围内的四个时钟输入,并生成五个时钟输出,频率范围从2 kHz到945 MHz,并可选择高达1.4 GHz的频率。该设备基于硅实验室第三代DSPLL技术,提供高度集成的PLL解决方案,无需外部VCXO和环路滤波器组件。

SILICON LABS - JITTERATTENUATOR,抖动衰减器,精密时钟倍增器,PRECISION CLOCK MULTIPLIER,SI5369A-C-GQ,SI5369,SI5369D-C-GQ,SI5369C-C-GQ,SI5369B-C-GQ,STM-64 LINE CARDS,MSPP,OC-192,OTN,STM-64线路卡,光传送网,MEASUREMENT,同步光纤网,TEST,SONET,BROADCAST VIDEO,国际电联G.709,WDM MUXPONDER,SDH OC-48/STM-16,CUSTOM FEC LINE CARDS,WIRELESS BACKHAUL,无线中继器,ROADM线路卡,SYNCHRONOUS ETHERNET,广播视频,测试,10GBE, 1/2/4/8/10G FC LINE CARDS,SDH + PDH CLOCK SYNTHESIS,测量,GBE,DATA CONVERTER CLOCKING,SDH+PDH时钟合成,ITU G.709,波分复用复用转发器,同步以太网,定制FEC线路卡,WIRELESS REPEATERS,无线回程,ROADM LINE CARDS,数据转换器时钟,10GBE、1/2/4/8/10G FC线卡

【技术】Silicon Labs低功耗抖动衰减器的第四代DSPLL技术,可简化时钟设计

Silicon Labs发明了DSPLL®技术,这是一种结合了数字信号处理(DSP)和PLL技术的混合方法,可简化高速互联网基础设施应用所需的时钟倍频和抖动衰减电路。现在已进入第四代,这种先进的专利时序技术现在是用单个集成电路替换多个离散锁相环路PLL元件的最佳解决方案,该集成电路集成了DSP电路和超低抖动时钟或电压控制振荡器。

【经验】SI5342抖动衰减器CML电平设计注意事项

SI5342抖动衰减器是Silicon Labs推出的高性能4输入2输出的时钟芯片,不仅可以作为去抖时钟芯片也可以作为普通的时钟发生器,功能非常强大,其输出电平格式支持LVPECL、LVDS、LVCMOS、HCSL、CML等多种电平选择,并实现GUI软件界面选择设计或者寄存器的直接配置,设计较为方便。今天讨论的是CML电平格式输出配置。

Si5366精密时钟乘法器/抖动衰减器

Si5366是一款用于高速通信系统的精密时钟倍频器,适用于SONET OC-48/OC-192、以太网和光纤通道。该器件接受8 kHz至707 MHz范围内的四个时钟输入,并生成五个频率乘法时钟输出,范围从8 kHz到1050 MHz。Si5366基于Silicon Laboratories的第三代DSPLL技术,提供任意频率的综合和抖动衰减功能。

SILICON LABS - JITTER ATTENUATOR,抖动衰减器,精密时钟倍增器,PRECISION CLOCK MULTIPLIER,SI5366,SI5366-C-GQ,ITU G.709 LINE CARDS,光学模块,10GBE, 1/2/4/8/10G FIBRE CHANNEL LINE CARDS,SYNCHRONOUS ETHERNET,测试,测量,OC-192/STM-64 LINE CARDS,GBE,MEASUREMENT,同步光纤网,10GBE、1/2/4/8/10G光纤通道线路卡,OPTICAL MODULES,ITU G.709线路卡,TEST,SONET,同步以太网,OC-192/STM-64线路卡,SDH OC-48/STM-16

【经验】关于高性能抖动衰减器Si5397的失锁问题分析

Si5397是Silicon Labs公司推出的基于最新DSPLL技术的高性能抖动衰减器产品,有用户使用Si5397评估测试时碰到一个失锁问题:检测发现Si5397无法正常锁定,检测输出时钟与输入时钟完全不同步,检测相关的状态寄存器发现0XC的寄存器为9,0xd的寄存器提示无LOS和OOF告警,0xe寄存器提示有LOL失锁但无法进入free run模式。针对该问题,笔者进行了测试并给出了解决方案。

【经验】如何设置抖动衰减器Si5344以跟踪频偏变化的输入信号?

Silicon Labs推出的抖动衰减器Si5344是基于第四代DSPLL专利技术的高性能4输入4输出的时钟芯片。日前有用户反馈输入的时钟信号是一个周期性的频偏变化信号出现失锁,这个输入时钟的输入频偏每隔几毫秒在±几个ppm到零频偏之间周期性变化。本文就该问题进行分析并给出具体解决措施。

Si5368任意频率精密时钟乘法器/抖动衰减器

Si5368是一款高精度时钟倍频器,适用于需要亚皮秒均方根抖动性能的应用。该设备接受2 kHz至710 MHz范围内的四个时钟输入,并生成五个时钟输出,频率范围从2 kHz到945 MHz,并可扩展至1.4 GHz。Si5368基于Silicon Laboratories的第三代DSPLL技术,提供高度集成的PLL解决方案,无需外部VCXO和环路滤波器组件。

SILICON LABS - 任意频率精密时钟倍增器/抖动衰减器,ANY-FREQUENCY PRECISION CLOCK MULTIPLIER/JITTER ATTENUATOR,JITTER-ATTENUATING PRECISION CLOCK MULTIPLIER,抖动衰减精密时钟倍频器,SI5368C-C-GQ,SI5368,SI5368B-C-GQ,SI5368A-C-GQ,ITU G.709 LINE CARDS,SYNCHRONOUS ETHERNET,广播视频,测试,LINE CARDS,无线基站,测量,DATA CONVERTER CLOCKING,线卡,MEASUREMENT,ITU G.709线路卡,TEST,同步以太网,定制FEC线路卡,BROADCAST VIDEO,数据转换器时钟,WIRELESS BASESTATIONS,CUSTOM FEC LINE CARDS

电子商城

现货市场

品牌:SKYWORKS

品类:HIGH-FREQUENCY, ULTRA-LOW JITTER ATTENUATOR CLOCK WITH DIGITALLY-CONTROLLED OSCILLATOR

价格:¥365.2522

现货:173

服务

可定制射频隔离器/环行器(10M-40GHz),双工器/三工器(30MHz/850MHz-20GHz),滤波器(DC-20GHz),功分器,同轴负载,同轴衰减器等射频器件;可定制频率覆盖DC~110GHz,功率最高20KW。

最小起订量: 1 提交需求>

支持 3Hz ~ 26.5GHz射频信号中心频率测试;9kHz ~ 3GHz频率范围内Wi-SUN、lora、zigbee、ble和Sub-G 灵敏度测量与测试,天线阻抗测量与匹配电路调试服务。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳/苏州 提交需求>

登录 | 立即注册

提交评论