【技术】YouPHY-DDR技术方案集高速率与低功耗性能于一体,支持667Mbps到4800Mbps的数据传输速率

具有专利的YouPHY-DDR先进技术

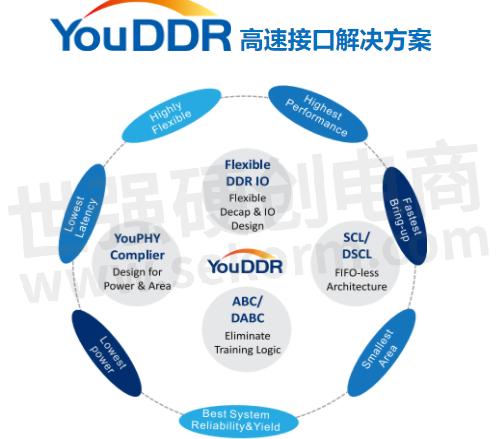

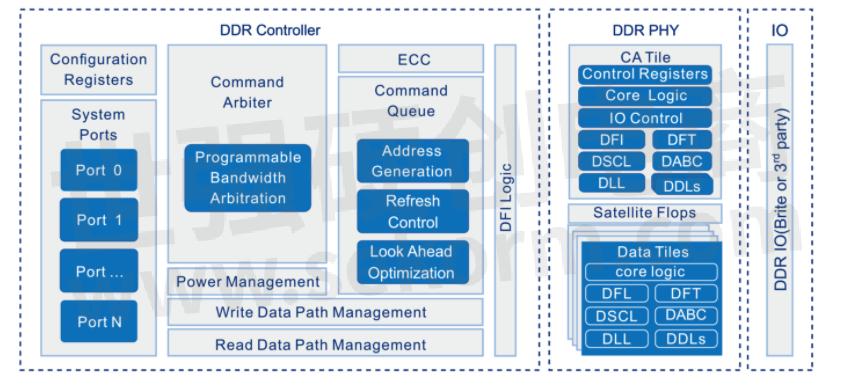

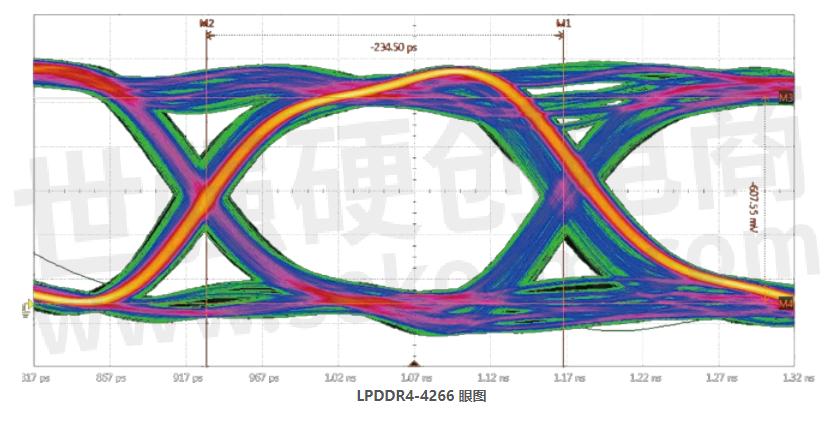

灿芯半导体提供的YouPHY-DDR技术是一个完整的子系统,它不仅包括DDR控制器(controller),物理层(PHY)和接口单元(I/O),而且包括特别开发的调试和测试软件。该方案可支持LPDDR2、 DDR3、LPDDR3、DDR4、LPDDR4和DDR5等应用,支持从667Mbps 到4800Mbps的数据传输速率。YouPHY-DDR是基于中芯国际从130纳米到14纳米的各种先进工艺而开发,创造了一个无法超越的集高速率与低功耗性能于一体的DDR。其特有的动态自校准逻辑(DSCL)和动态自适应位校准技术(DABC),可自动补偿芯片级、封装级、板级和存储器级别的工艺/电压/温度(PVT)波动而产生的器件性能差异,以及实现传输字节间的斜交自动补偿。YouPHY-DDR可以为客户提供最高性能、最低功耗、最小面积和最快上市时间的DDR接口IP方案。

DDR子系统核心特征:

DDR控制器

符合DFI 4.0的 DDR控制器架构,具有高度灵活性且可定制,支持包含AXI, AHB 和FIFO-based等接口在内的可高达32种目标接口,用户可定制的仲裁控制器(scheduler)。

DDR PHY

完整的DDR协议training

-- CA training

-- DQ read training

-- DQ write training

-- Write leveling

-- Vref training

PHY与DFI 4.0 兼容,并可向下兼容DFI标准,以方便客户与原有的早期DFI版本兼容集成

PHY包含动态自校准逻辑(DSCL)技术

-- 可以根据由制造工艺引起的静态变量和使用温度、电压和数据模式引起的动态变量,自动补偿DDR接口时序

PHY包含动态自适应位校准(DABC)技术

-- 自动补偿每条lane中的各个位(bit)的差异,动态自校准逻辑可以提供最低可达0.5 – 1时钟周期的PHY延时,动态自校准逻辑可通过硬件流程快速完成系统配置,更高的长期系统稳定性,提供灵活的PHY布图,以达到业界最小的PHY面积,PHY和可配置的IO可以harden到一起便于应用。

Combo PHY可选项包括:

-- DDR2/DDR3 PHY Combo

-- LPDDR2/DDR3 PHY Combo

-- LPDDR2/LPDDR3/DDR3 PHY Combo

-- DDR3/DDR4 PHY Combo

-- LPDDR3/4 + DDR3 PHY Combo

DDR I/O

--高性能,低抖动DDR IO

--低功耗/面积小

--通过硅验证

IP交付和设计支持

DDR控制器作为RTL交付,而PHY和IO作为加固宏指令交付,以适应目标芯片平面和面板。如有需求,灿芯半导体可以交付完全加固的DDR子系统(控制器,PHY以及IO)

PHY交付物

网表, SDF, LEF, LIB, Verilog,定时报告及技术文档。

IO交付物

所有PHY交付物的框架指导和评估

技术指导

灿芯半导体为DDR IP提供完整的版图和集成指南,并在流片前对DDR子系统实现进行了技术评估。

技术支持在硅验证后也会继续提供。

- |

- +1 赞 0

- 收藏

- 评论 1

本文由顾峥峥转载自灿芯半导体,原文标题为:YouDDR 高速接口解决方案,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

Brite Semiconductor Introduces Zero-Latency and True-Adaptive technologies for High-speed DDR PHY

Brite Semiconductor announced the launch of Zero-Latency and True-Adaptive technologies for high-speed DDR PHYs. These technologies have already begun to be deployed on 22/28nm DDR4/LPDDR4, 4x high-performance PHY IPs, which bring customers a whole new experience with higher efficiency and stability.

灿芯半导体Zero-Latency(零延迟)和True-Adaptive(真自适应)两项创新技术用于DDR物理层

灿芯半导体日前宣布推出用于高速DDR物理层中的Zero-Latency (零延迟)和True-Adaptive(真自适应)两项技术。这两项技术已经开始在12/14 FinFET, 22/28nm的DDR4/LPDDR4,4x高性能物理层IP上进行部署。

DDR信号完整性测试如何测试?

本文简述了启威测对于DDR产品的信号完整性测试及一致性验证的过程,包括测试前需要做的准备,测试的步骤及测试的注意事项,通过简析原理提供多种测试方案。

SGM2054吸电流和源电流DDR终端稳压器

SGM2054是一款专为低成本的DDR(双倍数据速率)端接稳压器设计的器件。它具有逻辑控制的关断模式、输出电流限制和热关断保护等功能。该器件适用于DDR2、DDR3、低功耗DDR3、DDR3L、DDR4和DDR5 VTT总线端接供电,并提供快速瞬态响应、远程感应和软启动功能,以减少浪涌电流。

SGMICRO - 灌和源DDR终端稳压器,接收端和源端DDR(双倍数据速率)终端稳压器,SINK AND SOURCE DDR (DOUBLE DATA RATE) TERMINATION REGULATOR,SINK AND SOURCE DDR TERMINATION REGULATOR,SGM2054,SGM2054XTD10G/TR,STB,机顶盒,伺服器,SERVER,NOTEBOOK,打印机,WIRELESS BASE STATION,无线基站,LCD TV,PRINTER,笔记本,DESKTOP PC,液晶电视,台式机

灿芯半导体DDR4 IP在40纳米工艺上实现了2400 Mbps速率

灿芯半导体YouPHY-DDR系列DDR4,DDR3/LPDDR3子系统通过了40纳米低漏电工艺流片验证。根据实测数据,YouPHY-DDR子系统为客户带来了低功耗、小面积的高速DDR方案,其传输速率成功地在DDR4标准上实现了2400 Mbps,在DDR3/LPDDR3标准上实现了2133 Mbps。

得润电子(DEREN)DDR系列连接器选型指南

DDR4 Series Connector DDR5 Series Connector

得润电子 - CONNECTOR,DDR5 CONNECTOR,DDR4 CONNECTOR,56 7Y D2-001HXRXXR-SQ,568QD1-001HXXXXX-SQ,568QD0-001HXXXXX-SQ,40-42057-2880*******,40-42057-2881*******,40-42057-2882*******,56 7Y D2-002HXSXXR-SQ,40-42181-288XXXXXTX,567U10-00XH-SQ,568QD1-002HXXXXXH-SQ,40-42272-2600XRHF-SQ,40-42273-2600XRHF-SQ,40-42275-2600XRHF-SQ,40-42274-2600XRHF-SQ,40-42057-288XXXXXTX,40-42277-2600XRHF-SQ,40-42181-2881*******,40-42181-2880*******,40-42181-2882*******,40-42276-2600XRHF-SQ,40-42560-288XXXXXTX,40-42057-2883*******,56 7Y D2-001HXSXXR-SQ,40-42181-2883*******,56 7Y D2-002HXRXXR-SQ,567U11-00XH-SQ

【选型】思瑞浦DDR SDRAM存储器助力工控机,集成功率MOSFET,为DDR终端提供灌电流和源电流

某客户由于DDR电源设计中用到VTT电压,对电流要求比较大,且要求电源既能吸电流,也能灌电流,因此考虑采用专用的DDR电源芯片进行设计。本文推荐思瑞浦TPL51200-DF8R应用在工控机DDR电源电路。

遇到DDR信号完整性测试问题?来看这份故障排除指南

DDR测试环境图DDR芯片(Double Data Rate )的信号完整性测试在设计和验证DDR存储系统时非常重要。当在进行DDR(包括DDR3/4/5)信号完整性测试时遇到问题时,本文介绍DDR信号完整性测试问题故障排除指南。

内存DDR4信号一致性眼图测试的案例分享

在 DDR4 规范 JESD79‐4 中,对物理层信号测试要求有:DQ眼图模板测试、抖动分析、电气特性测试,时序测试。相比 DDR3,DDR4 对眼图测试和抖动测试提出了新的要求。启威测实验室提供DDR2/3/4/5以及LPDDR4信号完整性测试及一致性验证。

TPL51200系列3-A吸电流和源DDR端接稳压器

思瑞浦 - 灌和源DDR终端稳压器,SINK AND SOURCE DDR TERMINATION REGULATOR,TPL51200,TPL51200 SERIES,TPL51200-DF8R,电信,联网设备,DDR2地址,工作站,DDR3地址,DDR4地址,DESKTOPS,SERVERS,低功耗DDR3,笔记本,DDR,基站,DDR3L,NOTEBOOKS,BASE STATION,WORKSTATIONS,NETWORKING EQUIPMENT,数据中心,TELECOM,LOW POWER DDR3,服务器,DATACENTERS,台式机,DDR4,DDR3,DDR2

TPL51200-S系列3-A吸电流和源电流DDR终端稳压器

该资料介绍了TPL51200-S系列3-A Sink and Source DDR Termination Regulator的特性、应用和规格。该系列产品专为DDR内存应用设计,具有支持多种电压轨、高电流处理能力、快速负载瞬态响应等特点,适用于笔记本电脑、台式机、工作站、服务器、网络设备和数据中心等领域。

思瑞浦 - 灌和源DDR终端稳压器,SINK AND SOURCE DDR TERMINATION REGULATOR,TPL51200,TPL51200-DF8R-S,TPL51200G-DF8R-S,TPL51200G-S,TPL51200-S SERIES,TPL51200 SERIES,TPL51200-S,电信,联网设备,DDR2地址,工作站,DDR3地址,DDR4地址,DESKTOPS,SERVERS,低功耗DDR3,笔记本,DDR,基站,DDR3L,AUTOMOTIVE APPLICATIONS,NOTEBOOKS,BASE STATION,WORKSTATIONS,汽车应用,NETWORKING EQUIPMENT,数据中心,TELECOM,LOW POWER DDR3,服务器,DATACENTERS,台式机,DDR4,DDR3,DDR2

3A Sink and Source DDR Termination Regulator Supporting 2.5V, 3.3V and 5V Power Rails

3PEAK‘s TPL51200 series devices are 3A sink and source DDR termination regulators specifically designed for the DDR applications with heavy space limitation. The TPL51200 series devices implement a fast load-transient response and only requires a minimum output capacitance of 20μF. The TPL51200 series devices are available in the thermally efficient 10-pin 3×3 DFN package with thermal pad, and support the operating temperature range from –40℃ to +125℃.

Alliance Memory’s Featured Products at Electronica 2022: eMMCs/DDR4 SDRAMs/1.8V Serial NOR Flash/DDR3 SDRAMs

Compliant with the JEDEC eMMC v5.1 industry standard, Alliance Memory’s eMMC solutions integrate NAND flash memory with an eMMC controller and flash transition layer (FTL) management software in a single package for solid-state storage in consumer, industrial, and networking applications.

TPL51206系列2-A灌电流和源DDR端接稳压器

思瑞浦 - 灌和源DDR终端稳压器,SINK AND SOURCE DDR TERMINATION REGULATOR,TPL51206 SERIES,TPL51206-DFFR,TPL51206,联网设备,DDR2地址,工作站,DDR3地址,DDR4地址,DESKTOPS,SERVERS,低功耗DDR3,笔记本,电信站,DDR,基站,DDR3L,NOTEBOOKS,BASE STATION,WORKSTATIONS,NETWORKING EQUIPMENT,数据中心,LOW POWER DDR3,TELECOM STATION,服务器,DATACENTERS,台式机,DDR4,DDR3,DDR2

【经验】DDR终端稳压器SGM2054用于DDR4的设计经验

SGM2054是圣邦微推出的一款具有典型3A灌电流和拉电流的DDR终端稳压器,专门针对低输入电压、低成本、低噪声的空间紧凑型系统而设计。SGM2054具有快速瞬态响应、电压补偿和软启动能力,以减少浪涌电流。本文介绍SGM2054用于DDR4的设计经验。

电子商城

现货市场

服务

深圳市启威测实验室,面向所有企业提供信号完整性测试服务,主要包括USB、HDMI 、DP、MIPI、PCIe 、SD/EMMC、DDR接口信号测试。测试手段有波形测试、眼图测试、抖动测试等。

提交需求>

登录 | 立即注册

提交评论