【经验】通过Si5345时钟IC评估板上的相位噪声测量实例分析半端差分输出时钟情况

通常在时钟IC评估板上实现交流耦合输入和输出时钟,并为差分时钟信号的每个极性提供单独的SMA RF连接器。这能够立即将输出时钟连接到测试设备上的单端50Ω输入,如频率计数器,示波器,相位噪声分析仪,频谱分析仪等。这里有一个最佳实践原则:当进行测量时,差动输出缓冲器的两个极性端都应该连接,即使极性没有被测量。不这样做的后果是什么?这是本文的主题,半端差分输出时钟的情况。

相位噪声测量实例

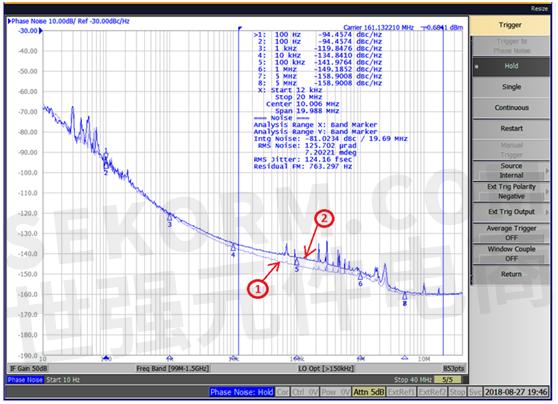

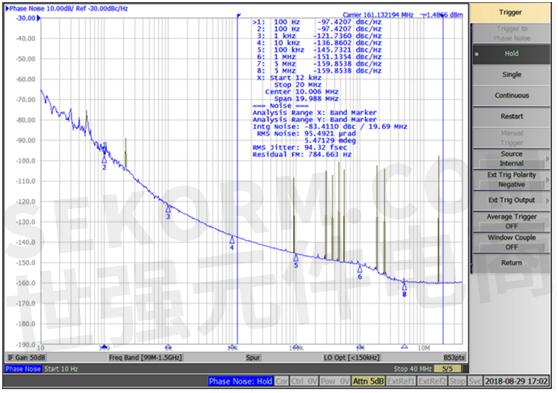

首先,在频域上分析。 参考下面的相位噪声图。这两个在屏幕截图中的案例来自时钟发生器Si5345评估板的OUT0。

1、OUT0B连接到50Ω示波器输入。这是正确(完全)端接情况。

2、OUT0B连接到1MΩ示波器输入。这是半端接的情况。

基于当前的SILICON LABS ClockBuilder Pro(CBPro)样本计划,交流耦合的标称频率设置为161.1328125 MHz,输出格式为2.5V LVDS。该板实际上处于自由运行模式,这是为了最小化工作台设置。在第一种情况下,12kHz至20MHz RMS相位抖动测得为89.512fs。在第二种情况下,12kHz至20MHz RMS相位抖动增加到124.16fs。相对增长约为39%,这是一个显著影响。

图1 相位噪声频域仿真图

相位噪声测量实例

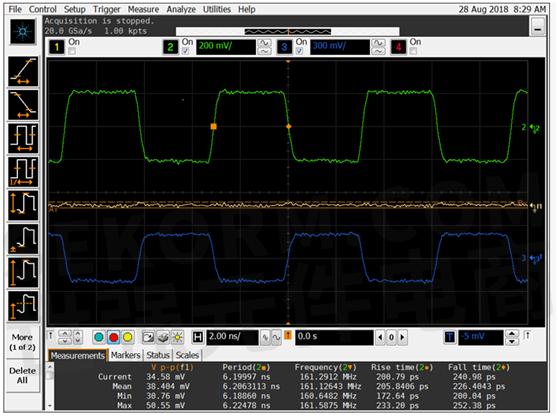

在时域中分析。请参考下面的示波器图,上部迹线是分配给通道2的OUT0,OUT0B分配给通道3,共模(CM)电压计算为f1。可以看出,由于我们位于交流耦合电容的远端,因此不测量直流值,而是测量交流耦合OUT0和OUT0B的平均值所代表的噪声。(这里的比例差异是为了适应半端接的情况,与计算无关)在第一个屏幕捕获中,两个示波器输入被设置为50Ω。波形形状看起来比较合理,CM噪声平均约为38 MVPP。

图2 第一次屏幕捕获示波器波形图(输入设置为50Ω)

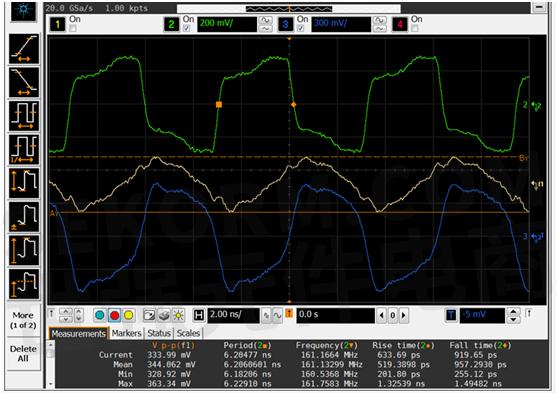

在第二次屏幕捕获中,唯一的区别是OUT0B的输入已设置为1MΩ。现在两种波形形状都更大且失真。此外,CM噪声平均增加到大约344mVpp,这几乎是一个数量级增加的CM噪声。

图3 第二次屏幕捕获示波器波形图(输入设置为1MΩ)

可以看出,在这些实验中,时域测量比频域测量更加直观。相位噪声差异甚至可能在自动化测试中被掩盖。所以对于实验室工作台而言,最好拥有两种类型的仪器。

根本原因

为什么仅端接输出时钟的一半会产生这样的影响?请看简化模型。

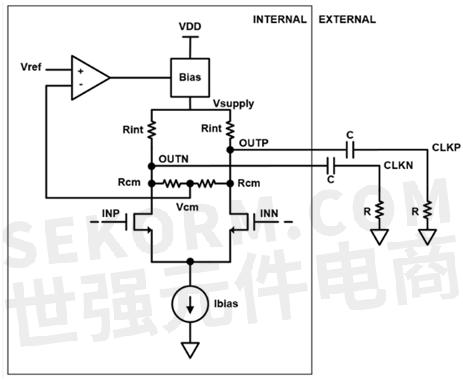

图4 缓冲器设计简化模型

左边框中的元件在IC内部,表示CML或电流模式逻辑驱动器的简化模型,该模型可以与几种摆动格式兼容。交流耦合电容通常位于EVB上,此处所示的负载电阻R通常为50Ω,用于测试设备。传输线未示出,但PCB走线和同轴电缆都可以假定为标称50Ω。(交流耦合负载端接也可视为CLKP和CLKN之间的100Ω差分,其中中心抽头CM电压为GND。)

一些显著的特征包括:

1. 电流源的偏压电流不断下沉。首先,根据输入信号,当完全导通时,电流通过输入NMOS晶体管之一切换。

2. 内部端接电阻Rint通常为~R或2*R以节省电流。

3. 在2个电阻器Rcm的中心点处感测共模电压Vcm。这些电阻的值通常为>> R,例如约为kΩ。

4. 运算放大器驱动偏置网络,使检测到的Vcm等于Vref。

5. 每个输出电压摆幅基于Vsupply减去Rint上随着电流变化的电压降摆动。

驱动器是对称的,设计用于特定的直流偏置超过预期端接操作。为了不影响预期的偏置,直流耦合负载需要具有与Vcm完全相等的公共电压,这就是需要交流仪器负载的原因。然而,如果交流耦合没有对称的负载,那么驱动器将是不平衡的,结果输出共模电压Vcm将被调制,这会影响偏置和操作。在这种特殊情况下,CM反馈电路显然无法跟上。所测量的端接半电路的性能由于未端接半电路的操作而退化。

串扰特性

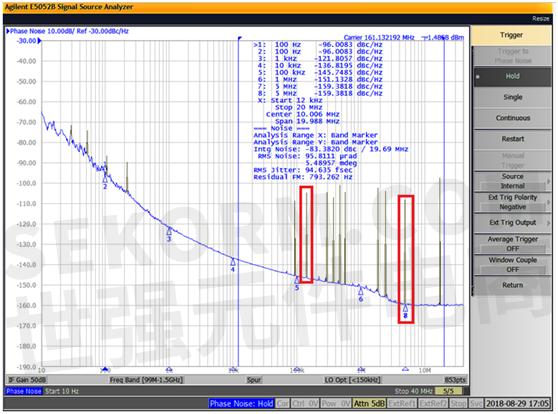

半端差分输出甚至可以以微妙的方式影响相邻输出驱动器的性能。在这个实验中,继续像以使用时钟IC Si5345 EVB。下面的相位噪声曲线是OUT0设置为标称161.1328125MHz,与OUT0B端接之前一样。相邻通道OUT1/OUT1B设置为标称值的2倍或322.265625MHz。两种极性都被正确端接。12kHz至20MHz的相位抖动在5次扫描中平均测得94.32fs。

图5 相位噪声曲线(两种极性都被端接情况)

下一个相位噪声图也是就OUT0分析,此时相邻输出OUT1B未端接,其他条件和前面一样。相位抖动没有显着增加,而在电力线频率区域上方出现了2个新的支线,如下所示。

图6 相位噪声曲线(OUT1B未端接情况)

端接选项

评估板和类似的应用板有许多端接选项,包括:

1. 使用差分限幅放大器或平衡-不平衡转换器将差分时钟转换为单端时钟。

2. 将每个极性连接到50Ω仪器输入。

3. 使用SMA 50RF负载终端端接每个未测量的极性。

衰减器作为实验室应急终端

实验室里通常有许多通道时钟EVB,在测试过程中会消耗大量的终端。如果很多人同时在实验室工作,则不能总是按照想要的方式端接每个时钟。因此,可以使用衰减器作为实验室应急终端。市售衰减器是由3电阻网络组成的PI衰减器。第一个电阻R1分流到GND,接着是R2串联,然后是另一个R1分流到GND。

- |

- +1 赞 0

- 收藏

- 评论 4

本文由鲁班大师翻译自Silicon Labs,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

评论

全部评论(4)

-

![]()

![]() 大公主 Lv5. 技术专家 2018-10-22了解一下

大公主 Lv5. 技术专家 2018-10-22了解一下 -

![]()

![]() duanmaxie Lv8. 研究员 2018-10-22不错

duanmaxie Lv8. 研究员 2018-10-22不错 -

![]()

![]() 用户71119603 Lv6. 高级专家 2018-10-22好文

用户71119603 Lv6. 高级专家 2018-10-22好文 -

![]()

![]() 闲云 Lv7. 资深专家 2018-10-22学习了

闲云 Lv7. 资深专家 2018-10-22学习了

相关推荐

【经验】时钟发生器Si5341型号定制以及输出串扰问题解决方法

Silicon Labs公司推出的时钟发生器Si5341最大能够支持10路差分输出,输出频率范围100Hz~712.5MHz,输出抖动范围均小于100 fs(0.1 ps),并且Si5341内部带有模拟锁相环,配合Silicon Labs的专利MultiSynth技术,能够以0 ppm合成所需的频点,本文将详细介绍Si5341型号定制以及输出串扰问题解决方法。

【经验】Silicon Labs时钟发生器SI5332时钟差分信号变单端输出问题及处理方法

Silicon Labs时钟发生器SI5332在使用CB Pro软件配置好电平之后,有工程师会有疑问,原本配置好的3.3V 125MHz lVDS电平 OUT/OUTB是否可以在配置不动的情况下单独分开做两个125MHZ单端时钟输出?本文将为你解析。

【经验】如何使用CBPro软件配置时钟发生器Si5332的晶体输入端电容

Silicon Labs的时钟发生器Si5332支持外置晶体/晶振/参考时钟输入,也支持内置晶体的版本,目前使用较多的是内置晶体版本,但部分用户在设计时由于自身需求仍然选择外置晶体,而选择外置晶体时通常会发现配置的晶体无法正常启动或者启动时间不太理想,如果使用CBPro软件适当配置Si5332,可以避免大部分问题。本文就将介绍如何使用CBPro软件配置Si5332的晶体输入端电容。

【应用】十路输出时钟的时钟发生器Si5341用于5G CU平台的时钟链路设计,时钟频点范围100Hz~1028MHz

本文推荐使用Silicon Labs高性能时钟发生器Si5341用于5G CU的主控平台时钟设计,有多达十路输出时钟,时钟频点范围是100Hz~1028MHz,涵盖了5G CU主控平台所需的全部频点,时钟路数足够多,可以尽量减少晶振的用量。

【经验】如何实现SI534X/SI538X时钟发生器SPI在线编程?

Silicon Labs SI534X、SI538X时钟发生器包括基于模拟PLL的SI5340、SI5341和基于DSPLL技术的SI5342、SI5344 、SI5345、SI5342H、SI5344H、SI5346、SI5347、SI5348以及无线专用时钟SI5380、SI5382、SI5386等时钟芯片产品。目前在光通信、数据中心、服务器、小基站、光模块等产品中有广泛的应用

【经验】时钟发生器Si5332接地PAD引起的频率计划烧录失败问题及解决方式

Si5332支持多个输出端,每个输出端有独立的输出电压,使用ClockBuilder Pro可以快速轻松地配置频率计划,并且有专门的烧录器可通过I²C接口烧录到芯片内的NVM,但是有时候接地PAD引起的频率计划烧录失败,本文将简要分析。

【应用】时钟发生器SI5351A-B-GTR用于智能音箱,以0 ppm误差产生200 MHz的任意频率合成输出

本文推荐Silicon Labs的SI5351A-B-GTR这颗小封装的时钟发生器作为智能音箱的参考时钟源,替代相关的各种时钟源。SI5351芯片是可通过I2C接口配置的时钟发生器,能以0 ppm误差产生高达200 MHz的任意频率合成输出。

【应用】SDI编解码技术应用之基于高精度时钟发生器的高清视频同步系统设计

在SDI高清视频系统中,我们运用世强代理的Silicon Labs公司系列高精度时钟发生器Si5324,Si5332,Si5338,Si5341,Si5345,Si552等,来组建起整个SDI同步系统。产品覆盖了SD-SDI,HD-SDI,3G-SDI,6G-SDI,12G-SDI等标清、高清和超清的各种SDI标准高低端应用,为SDI设备提供最优的时钟性能。

【应用】3通道输出的Silicon labs时钟发生器可用于视频直播终端,输出频率误差0ppm

时钟发生器SI5351A-B-GT可用在视频直播终端产品中,主要为主板启动时提供初始化时钟信号,让主板能够启动。内置晶体,可工作在25MHZ或27MHZ晶体,由2个锁相环PLLA和PLLB进行相位锁定,通过分频器再分成3个频率输出通道,给主板提供信号源。

时钟发生器Si5351的版本B和版本A有什么变化,推荐使用哪个版本?

时钟发生器Si5351目前主推版本B,版本B和版本A的主要变化有:(1)RevB:频率输出范围是2.5 kHz到200 MHz;RevA:8 kHz 到160 MHz。(2)输出阻抗RevB是50欧姆,RevA是85欧姆。(3)RevB不支持24-QSOP封装。

【经验】如何对SI5338时钟IC进行烧录?

SILICON LABS推出SI5338时钟IC产品在项目开发时需要针对SI5338 进行编程才能输出相对应的频率,本文讲述了两种办法。

【选型】光模块误码仪时钟源推荐高性能时钟发生器SI5340配合京瓷晶振CX3225SB,精度极高

误码设备本身需要测试不同速率的光模块,针对不同速率的光模块还需要不同的频率源作为倍频的信号时钟源。高性能的时钟发生器推荐Silicon Labs高性能时钟发生器SI5340系列,输入的参考晶振推荐京瓷,CX3225SB系列,经过了大量市场验证可放心使用。

【产品】可提供4个PCIe时钟输出的PCIe时钟发生器,支持100MHz的串行ATA(SATA)

Si52144是一款由Silicon Labs(芯科科技)推出的支持扩频的PCIe时钟发生器,可以提供4个PCIe时钟和25 MHz参考时钟,符合PCI-Express Gen 1,Gen 2,Gen 3,Gen 3 SRNS,Gen 4标准。该器件具有四个用于使能输出的硬件输出使能引脚,以及一个用于控制PCIe时钟输出上的扩频的硬件引脚。 除硬件控制引脚外,I2C可编程性还可用于动态控制。

【经验】时钟发生器SI5338的LVDS匹配问题的分析测试案例

SI5338是Silicon Labs推出的一款经典的时钟发生器芯片,是一款目前广泛用于通信基站、传输网、政企网、数据中心、消费电子等多行业通用的时钟芯片。日常使用偶尔会碰到较多SI5338的应用问题,有寄存器配置的,也有输出匹配不一致的,对于寄存器问题,一般配合寄存器列表,可以简单较为容易的解决,对于匹配问题,也是SI5338时钟输出的重点关注部分,日前就有工程师碰到了一起LVDS输出匹配问题。

【经验】时钟发生器SI5332利用FS_INTx硬件管脚进行不同频率选择

Si5332是Silicon Labs公司的一款经典时钟发生器,支持内置多个频率profile的存储。实际使用时,我们往往只针对其中几个或一个输出,或者针对同一分频器的几个输出进行调整,不需要通过切换到新的整个profiles方式实现。这种情况下,利用FS_INTx硬件管脚进行不同频率选择是更好的切换方式。

电子商城

现货市场

服务

支持GSM / GPRS 等多种制式产品的射频测试,覆盖所有上行和下行的各项射频指标,包括频差、相差、调制、功率、功控、包络、邻道泄漏比、频谱、杂散、灵敏度、同道干扰、邻道干扰、互调、阻塞等等。满足CE / FCC / IC / TELEC等主流认证的射频测试需求。

实验室地址: 深圳 提交需求>

提供是德(Keysight),罗德(R&S)测试测量仪器租赁服务,包括网络分析仪、无线通讯综测仪、信号发生器、频谱分析仪、信号分析仪、电源等仪器租赁服务;租赁费用按月计算,租赁价格按仪器配置而定。

提交需求>

登录 | 立即注册

提交评论