【产品】西安智多晶新推Sealion系列FPGA SL2E-7E/V,具有低成本、低功耗优势

西安智多晶微电子有限公司的 Sealion(海狮)系列SL2E-7E/V FPGA 器件(下称“FPGA”),建立在一个优化的低功耗工艺基础之上,并提供最低的功耗,通过最低的成本实现较高的功能性。FPGA器件旨在用于大批量、成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的应用要求,在低成本、低功耗FPGA市场处于领导地位。对无线、有线、 广播、工业用户以及通信等行业中的低成本的小型应用,本 FPGA 无疑是理想的选择。

特性

FPGA 具有以下特性: 丰富的逻辑资源

FPGA 规模为6,864 逻辑单元(LUTs)

低功耗

优化的低功耗 55nm 工艺

核电压 1.2/3.3V

对大量丰富的并行处理资源的应用进行了重点优化

多逻辑单元以及布线资源

高性能可编程逻辑单元

采用 LUT4 查找表,可灵活地优化为 LUT5/LUT6 组合设计

灵活的资源可提升利用率

对逻辑单元操作模式的性能进行了优 化,例如可创建算术模式,用于实现 加法器、计数器、累加器和比较器。

内置 Flash

无须外部配置电路

支持快速上电启动

最大用户区域为 500Kbits

支持分布式和嵌入式存储

嵌入块存储容量为 9Kbits,可配置成单 端口、伪双端口、真双端口以及 FIFO 缓冲器或者 ROM,通过配置可实现多 种数据

宽度最大支持 234Kbits 分布式存储器

丰富的时钟资源

最大频率 Fmax=400MHz

最多可提供 16 个全局时钟,其中 8 个 可以复用为高扇出网络

提供多达 8 个专用时钟输入引脚

2 个 5 路时钟输出内置锁相环(PLL) 提供倍频、分频、相位转移等系统时 钟功能

2 个延时锁相环(DLL),提供分频、 相位偏移时钟功能

灵活强大的 I/O 单元

最高可达到 335 个有效用户 I/O

支持 400Mbps DDR2 SDRAM 接口

支持 Generic DDRx1, DDRx2

输入输出支持 3.3/2.5/1.8/1.5V 电压

支持 MIPI,接口速率高达 1.2Gbps

I/O 支持标准单端, 差分, 伪双端包括 LVTTL、LVCMOS、SSTL, HSTL、PCI, LVDS、BLVDS、mini-LVDS、RSDS

6 个 IO 块(Bank)

15-33MHz 基准晶体震荡输人缓冲器

可配置上拉、下拉及总线保持模式

片内 100 欧姆差分电阻

支持热插拔

配置模式

主模式(Active Serial AS)

从模式(Passive Serial PS)

自刷新配置(Self Refresh Configuration SRC)

JTAG

配置过程支持 SED/SEC 多比特流检测、 校验与单比特修正

配置过程支持多比特流加载,可在第 一个程序文件加载失败后,自动跳到 Golden 区域加载第二个程序文件

安全与 BSCAN

支持 256 比特 AES 比特流加密及压缩

芯片拥有 64-bit UID 的 DNA

兼容 IEEE1149.1 Boundary Scan (BSCAN)

封装

无铅封装

LQFP144

uBGA256

uBGA400

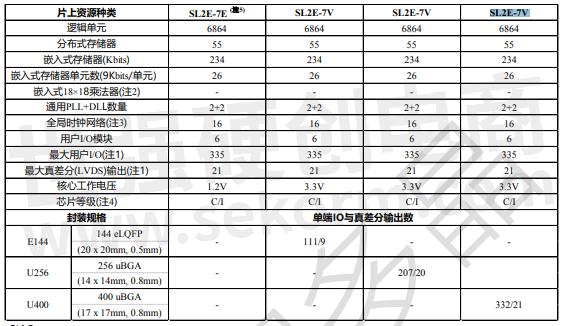

器件资源

- |

- +1 赞 0

- 收藏

- 评论 0

本文由小幸福转载自西安智多晶,原文标题为:Sealion(海狮)SL2E-7E/V FPGA 产品手册,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【产品】基于智多晶SL2-25E FPGA芯片的软件无线电(SDR)评估板,适用于项目开发初期验证、教学及培训

为了更好让无线通信客户评估智多晶FPGA芯片,西安智多晶为客户打造了一个专业的软件无线电(SDR)评估板,可用于客户前期的项目预研,其核心器件是西安智多晶的SL2-25E FPGA芯片,F256封装。这个评估板卡非常适合小带宽、低成本的通信项目,专网或公网的应用。

【产品】基于28纳米技术工艺的Seal 5000系列 FPGA,20K到200K的查找表逻辑单元

西安智多晶推出的Seal 5000 FPGA同样采用正向设计,芯片软件设计流程和ISE/Quartus II/Diamond 类似。智多晶的芯片架构可以接受ISE和Quartus II的代码,使用自主研发的FPGA开发软件“HqFpga”, 完成综合、布局布线、时序分析、配置编程和片内逻辑分析。智多晶的Seal 5000系列FPGA芯片和Virtex-7系列的FPGA芯片相容。

【产品】基于28nm国产FPGA的高性价比、高集成度软件无线电(SDR)方案平台 | 视频

在2021年3年31日ICT及5G通信专场|世强硬创新产品研讨会中,西安智多晶基于28nm技术设计了一款专业的软件无线电(SDR)评估板,可帮助客户做前期的项目预研,方便研发评估和导入智多晶FPGA,该评估板的核心器件是SL2-25E 。

【经验】如何在FPGA上实现低成本开根号运算?

开根号运算是科学计算和工程应用中基本而重要的运算之一,在QuartusII和ISE开发软件中,都集成了开根号的ip核,这些底层源码对于用户来说是不可见的,那么如何在西安智多晶的FPGA中实现开根号运算,是本文要探讨的课题。

【选型】西安智多晶(XIST)FPGA/CPLD可编程逻辑器件选型指南

目录- Seagull1000/Sealion2000/Sealion合封系列

型号- SL2D-25E,SEALION2000,SL2E-5E,SEAGULL1064C,SEAGULL1000,SG1128V,SEAGULL1256C,SEAGULL1064V,SG1064V,SEAL 5000,SG1256V,SEAGULL1256V,SL2-12E,SL2S-25E,SEAGULL 1000,SG1128C,SG1064C,SL2-25E,SL2S-12E,SL2-7E,SL2-5E,SEAGULL1128C,SL2E-7V,SEALION 2000,SG1256C,SEAGULL1128V

【应用】国产海狮系列FPGA SL2E-5E用于扩展外设接口,集成flash,工作频率高达300MHz

西安智多晶的SL2E-5E是一款集成了5K逻辑单元的小规模FPGA,但是比CPLD容量更大,能实现更多的逻辑设计,同时该FPGA内部集成了Flash,不需要再外接配置用的Flash,简化了电路设计。

【经验】西安智多晶5000系列FPGA内嵌MCU调试测试指南

西安智多晶推出的Seal 5000 FPGA SA5Z-30系列内部合封Cortex M3硬核,最高主频可达200Mhz,32KB数据RAM和128KB指令RAM。本文针对FPGA内嵌M3硬核的使用做简洁的开发过程。

西安智多晶发布软件无线电评估板,基于28nm FPGA芯片SA5Z-30并搭载ECR8661 RF收发器助力研发

为了让无线通信客户更方便评估智多晶FPGA芯片以及国产RF Transceiver,西安智多晶联合智锐星科技为客户打造了一个专业的软件无线电(SDR)评估板,可用于客户前期的项目预研。评估板的核心器件是28nm FPGA芯片SA5Z-30。

【经验】智多晶FPGA上实现LTE削峰算法PC-CFR

CFR算法是一种直接在数字域上面处理的方法,对于超出设定门限值的信号,直接在数字域上进行处理和消除。目前CFR算法有PW-CFR、NS-CFR和PC-CFR,常用的还是PC-CFR,其削峰能力最佳,本文就针对PC-CFR算法,在智多晶AD9365射频开发板上进行测试和实现。

Sealion(海狮)2000 系列 FPGA数据手册

型号- SL2D-25E,2000S,SL2E-5E,SEALION 2000S,SL2E-5E-8M121I,2000E,SL2-12E-8F256C,SEALION 25K,SL2-18,SEALION 5K,2000E 系列,SL2S-25 V,SEALION 2000E 系列,SL2-12,SL2S-12E,2000,SL2E-7V-8U400I,SL2S-25 E,SL2-25 V,2000 系列,SL2E-7 E,SL2E-7V,SL2E-5 E,SEALION 2000,SL2S-12E-8E176C,SL2S-12 V,SL2E-5E-8N84I,SL2E-7 V,SL2-25 E,SL2D-25 V,SL2E,SL2S-25,SL2S-12 E,SL2D,SL2S-12E-8F256C,SEALION 2000 系列,SL2-12 V,SL2-5,SL2S-25E-8U213C,SL2D-25 E,SL2-7,SEALION 7K,SL2E-7E,SL2S-25E,SL2S,SL2-25E-8U324C,SL2-12 E,SL2S-12,SEALION 12K,SL2,SEALION 2000D,SEALION 2000E,SL2-25

电子商城

现货市场

登录 | 立即注册

提交评论