【应用】Si5317抖动衰减时钟提供正确的锁相环带宽抖动衰减方案

时钟信号为每个集成电路和电气系统提供参考定时,客户通常是使用简单的时钟晶体作为时钟参考源。然而当电路应用有更加复杂的时序要求,通常需要用组合时钟来提供同步,生成和分发,如在无线基础设施和医学成像等一些需要高保真模拟到数字信号转换的应用领域。在下一代设计时,则需要更高的分辨率和更快的传输速率,下一代高性能网络和通信应用需要更快的传输速率和更高的数据处理速度,在这些应用中,时钟信号在整个体系结构中起着至关重要的作用, 如果设计欠妥,则整个系统的性能水平则受限于最底层的时序分辨率性能。在设备选择和硬件设计过程中必须特别注意,以确保在时钟设计方面能最大限度地提高系统性能。

2. 相位噪声和抖动

时钟信号的质量在很大程度上取决于它的相位噪声和抖动,理想的时钟源会产生纯正弦波。所有的信号功率将用一个频率产生。然而,实际上,所有的时钟信号都有一定程度的相位调制噪声,这种噪声将时钟信号的能量传播到邻近的频率,从而产生边带噪声。相位噪声通常用dBc/Hz表示,表示某一给定偏移频率处的功率大小与理想时钟频率的比值。射频(RF)和模数数据转换(ADC)应用需要非常低的相位噪声时钟。在射频RF应用中,相位噪声的增加会造成信道间的干扰,降低射频信号的质量。在ADC应用中,相位噪声的增加会限制数据转换器的信噪比(SNR)和等效比特数(ENOB)。

相位噪声是时钟噪声的频域表示。相位抖动,另一方面,是表示时钟信号的时域不稳定性,通常以皮秒(ps)表示。抖动可以描述为实际时钟信号的边缘与理想波形之间的随机变化。相位抖动是高速数字应用方面的性能因素,如数据通信、网络和高清视频传输,这些应用需要高达40gbps的数千兆数据传输速率,网络和高清视频的物理层收发器依赖于收发器内部相乘的低抖动参考时钟,来对从设备传输的高速数据应用进行计时。过度的抖动会导致更高的误码率,可能超过系统级的要求。

3. PLL带宽优化

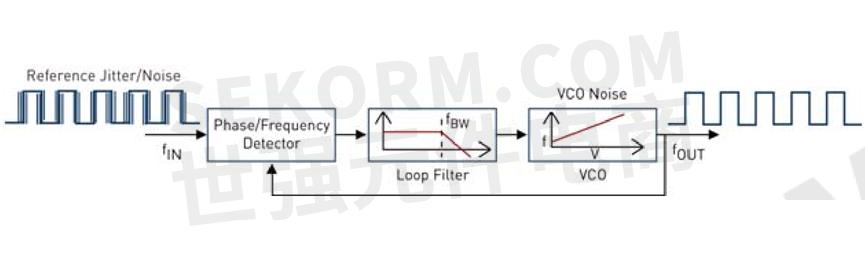

在高性能应用中是有必要关注相位噪声和抖动的。通常来说,抖动衰减时钟IC或离散锁相环(PLL)被用来产生低抖动时钟,传统的锁相环结构由相频检测器(PFD)、环路滤波器(LF)和压控振荡器(VCO)组成,如图1所示。锁相环滤波器通常使用分立器件实现。在使用高性能PLLs进行设计时,更具有挑战性因素之一是如何为给定的应用选择合适的环路带宽。与许多工程挑战一样,这是一个必须在应用层面上做出的权衡决定。

图 1. 锁相环输出抖动源

如图1,锁相环输出抖动由两个源控制:传输参考噪声和内部VCO噪声。参考噪声源包括参考定时源产生的抖动、PCB噪声耦合和电源噪声,VCO噪声源包括回路滤波器、VCO放大器和电源噪声。

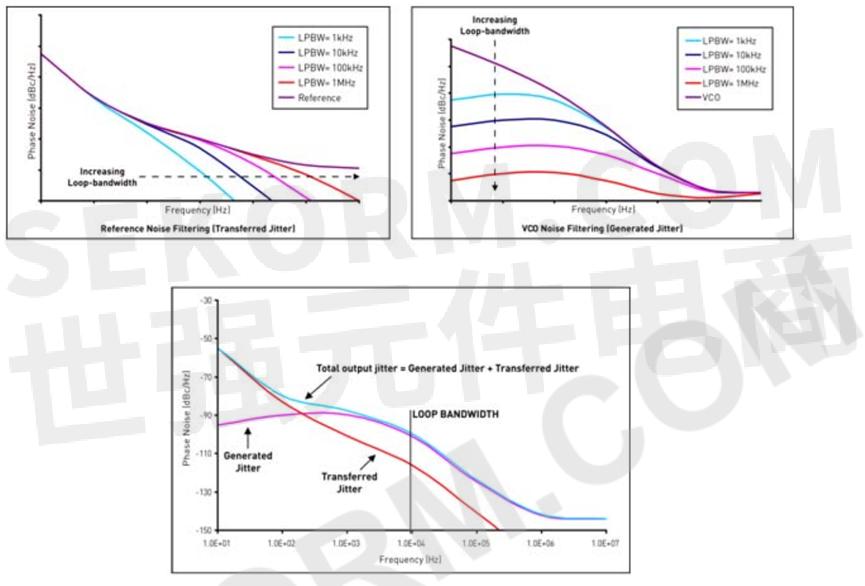

一个抖动衰减锁相环可以用来过滤来自输入时钟的噪声,并产生一个低抖动输出时钟。减少环路滤波器的带宽会增加参考时钟上抖动衰减量,从而减少从输入到输出的抖动。如果参考时钟有大量的抖动,通常建议使用低锁相环带宽来过滤这种噪声。然而,使用非常低的锁相环带宽并不总是有利的。主要原因是VCO噪声对锁相环输出抖动的相对贡献是随着环路带宽的减小而增大。除非锁相环具有非常低的噪声VCO,否则使用低锁相环带宽的影响实际上会增加输出时钟抖动,这就需要权衡决定。PLL带宽需要被设置为最小化VCO和参考抖动。由于参考时钟抖动可能因应用程序的不同而不同,所以这是需要在每个设计上独立做出的决定。如图2所示。

图2. 平衡抖动传输和抖动生成实现优化锁相环抖动性能

使用高质量电压控制晶体振荡器(VCXO)构建的分立锁相环可以用于这种情况;但是,本设计电路仍对电源开关噪声、PCB噪声耦合以及分立环滤波元件引入的噪声敏感。另一种选择是使用带有内部VCO的时钟IC,但是这些设备通常需要外部环路滤波器组件,这些组件对外部噪声源敏感。锁相环滤波器与VCO之间的接口是锁相环设计中最具噪声敏感性的节点之一。通过外环路滤波器元件进入锁相环的噪声会出现在VCO的输入端,并与VCO的增益系数相乘,增加VCO噪声,进而增加设计中的锁相环噪声。

使用分立循环滤波器的解决方案也增加了锁相环的设计和布局的复杂性。PLL稳定性需要针对每个独特的频率计划+环路带宽组合进行计算,以确保设计中有足够的相位余量。在一些高性能锁相环设计中使用了特殊的PCB布局技术,例如在环路滤波器组件周围使用保护环来提供隔离和最小化泄漏电流。由于大多数传统的高性能时钟集成电路需要多个、隔离的电源平面,循环滤波器布局的考虑为PCB设计增加了更多的复杂性。

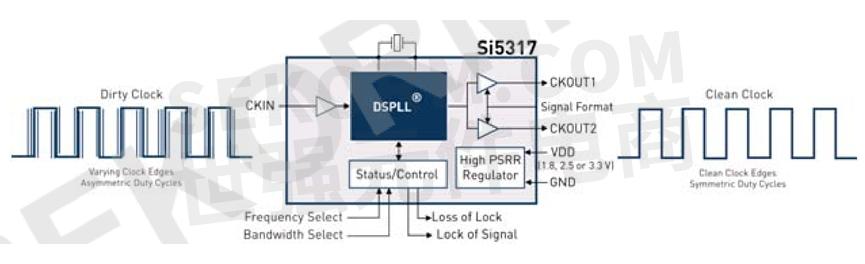

4. 使用SI5317进行在线抖动优化

图3显示了更好的方法。Si5317是一种低成本、高性能的抖动衰减时钟,基于已证明的SILICON LABS第三代DSPLL技术。该芯片可接受1 - 710 MHz任意频率的噪声基准时钟,并提供两个相同频率的超低抖动(0.3 ps rms, 12 kHz - 20 MHz)输出时钟。使用控制引脚设置设备的工作频率,不需要微处理器干预。此外,该设备还包括一个完整集成的数字控制环路滤波器,通过简单的引脚控制,硬件设计人员可以从60hz到8.4 kHz的最多8个设置中选择最优的环路滤波器值,使得管理传输抖动和生成抖动之间的权衡非常容易,从而在应用方面优化抖动性能。这种低成本、pin控制的设备可以添加到任何时钟路径,并进行数字优化以产生尽可能低的输出抖动,从而简化了对抖动敏感的应用方面的设计。

图3 抖动清除时钟

- |

- +1 赞 0

- 收藏

- 评论 6

本文由翻译自Silicon Labs,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

评论

全部评论(6)

-

![]()

![]() 慧慧1985 Lv7. 资深专家 2018-12-26下载,学习

慧慧1985 Lv7. 资深专家 2018-12-26下载,学习 -

![]()

![]() 志成 Lv7. 资深专家 2018-12-26学习,下载

志成 Lv7. 资深专家 2018-12-26学习,下载 -

![]()

![]() 花开富贵 Lv6. 高级专家 2018-12-26学习

花开富贵 Lv6. 高级专家 2018-12-26学习 -

![]()

![]() 世强代理 Lv7. 资深专家 2018-12-26支持

世强代理 Lv7. 资深专家 2018-12-26支持 -

![]()

![]() Harlin Lv5. 技术专家 2018-12-26好好好,狂赞这样的技术贴

Harlin Lv5. 技术专家 2018-12-26好好好,狂赞这样的技术贴 -

![]()

![]() 行行摄摄 Lv7. 资深专家 2018-12-26学习一下

行行摄摄 Lv7. 资深专家 2018-12-26学习一下

相关推荐

【应用】采用72fs低抖多路时钟合一芯片实现5G小基站设计,节省PCB面积和BOM成本

在5G小基站的原始设计中,由于产品推出的时间紧,通常采用的都是通用器件,而且时钟方案多采用两个时钟芯片,电路设计复杂,同步性能不好控制,导致系统噪声高、EVM指标差、成本高等问题。为解决上述问题,本方案采用低抖动多路时钟芯片Si5386,并搭配低噪声放大器、高精度授时模块、高精度晶振、高频板材、低热阻凝胶、高导热垫片等器件和材料实现了高性价比的5G小基站产品设计。

【应用】推荐小体积时钟芯片SI545用于400G相干光光模块,最低抖动80ns、温度稳定性±7ppm

当今光通信,传输速率高、传输距离远,400G ZR相干光光模块就是典型的应用代表。相干光光模块对频率稳定性要求极高,这给参考时钟芯片的选择,带来了极大的挑战。Silicon Labs推出的SI545支持837.5MHz频率、LVDS输出,抖动仅80fs、温度稳定性±7ppm、总体稳定性±20ppm。SI545为QFN-6封装,仅3.2×2.5 mm,完全满足400G相干光光模块的需求。

【应用】一种基于SI53301时钟芯片的光传输设备线卡应用方案

Silicon Labs时钟芯片SI53301相对的附加抖动仅为45fs,因此只要输入源(一般是XO)的抖动指标不高的话,不会引入过大的额外相位噪声。SI53301自带分频功能,在某种程度上可以代替实现PLL的部分功能,SI53301支持2分频和4分频,有两个输出Bank,每个Bank分别对应DIVA和DIVB分频器。

【选型】Silicon Labs 时钟和振荡器芯片选型指南

目录- 计时解决方案 晶体振荡器(XO) 压控晶体振荡器(VCXO) 时钟发生器 时钟缓冲器 抖动衰减器 无线时钟 网络同步器

型号- SI56X,SI5382,SI5383,SI5380,SI5381,SI5386,SI5331X,SI5384,SI590,SI5315X,SI591,SI595,SI510,SI598,SI511,SI596,SI597,SI514,SI515,SI512,SI513,SI516,SI52142,SI52143,SI52144,SI51210,SI5394,SI5391,SI5392,SI5397,SI5332X,SI5395,SI569,SI54X,SI567,SI52111,SI52112,SI570,SI571,SI5344H,100G,SI53212,SI5332,SI53208,SI5330X,SI5335,SI53204,SI5334,SI5338,SI547,SI545,SI546,SI549,SL18860,SI5311X,SI5342,SL18861,SI5340,SI52208,SI5341,SI5346,SI52202,SI5347,SI5344,SI52204,SI5345,SI550,SI5348,SI554,SI552,SI5342H,SI5350,SI53306,SI5351,SI53102-AX,SI52212,SI5336X,SI561,SI562,SI560,SI565,SI566,SI564,SI51214,SI51211,SI51218,SI52146,SI52147,SI532,SI533,SI530,SI531,SI534,SI5334X,SI540,SI544,SI541,SI542

一款适合IEEE 1588V2的专用时钟芯片

Silicon Labs日前推出了专门实现IEEE 1588协议的超低抖动时钟芯片SI5348,这款芯片可以满足IEEE 1588 V2组网对系统时钟极其苛刻的指标要求,完美实现IEEE 1588 V2协议。

【经验】超低相位噪声抖动衰减时钟芯片Si5382如何输出同步使能?

Si5382是Silicon Labs超低相位噪声抖动衰减时钟芯片,为每个输出端口时钟提供单独的使能OE控制bit位和外部全部输出使能控制引脚,没有可以同时控制其中几个输出使能的引脚或者寄存器。本文将具体说明如何解决同步使能。

Silicon Labs(芯科科技) Si53340/41/42/43/44/45低抖动时钟缓冲器 数据手册

描述- Si53340-45系列低抖动LVDS扇出时钟缓冲器适用于时钟和数据分配以及冗余时钟应用。这些设备具有典型超低附加抖动(50 fs),工作频率范围为直流到1250 MHz。内置稳压器提供高PSRR性能,减少了对外部组件的需求,简化了在噪声环境中低抖动时钟的分发。它们有多种配置选项,并提供可选择的输入时钟使用2:1输入多路复用器。其他功能包括独立的输出使能和内置格式转换。

型号- SI53340-B-GM,SI53344-B-GM,SI53342-B-GM,SI53343-B-GM,SI53341,SI53342,SI53343,SI53344,SI53344-B-GM,SI53340,SI53341-B-GM,SI53342-B-GM,SI53345-B-GM,SI53345,SI53345-B-GM,SI53343-B-GM,SI53340-B-GM,SI53341-B-GM

【产品】抖动率低至0.3ps的去抖时钟芯片Si5326在光模块中的应用

去抖是光模块接收中极其重要的设计之一。Silicon labs的去抖时钟芯片Si5326采用DSPLL专利技术,输出频率抖动最小可以达到0.3ps,因此常被用于光模块接收器当中用来做去抖设计。

【经验】高性能抖动衰减器时钟芯片Si5326在free run模式下锁定时间的几点注意事项

Si5326是Silicon Labs的基于第三代DSPLL专利技术的高性能抖动衰减器时钟芯片,有用户反馈Si5326在以自由振荡模式工作时锁定时间接近30s,与理论值相差甚远,因为即使是free run模式,也是Si5326内部锁相环锁定XA/XB的时钟,也有DSPLL完整的锁定追踪过程,影响锁定时间的因素很多,不过有几个因素需要特别引起注意。

【经验】Silicon Labs时钟芯片Si5332更改时钟输出频率的方法

Silicon Labs推出的Si5332任意频率的时钟发生器提供最高级别的集成,实现在 10/25/100G 数据中心、通信和工业应用程序中的完整时钟树整合。该芯片输出频率范围为5~ 333.33 MHz,具有 175fs 典型值的抖动性能,根据封装不同有 6路、8路、12路-时钟输出。它既可以工厂预先编程,也可以通过I2C接口,进行系统内编程。

【产品】更适合IEEE 1588设计的超低抖动时钟芯片SI5388/SI5389

Silicon Labs在充分调研了各大设备商的IEEE 1588产品设备后,实时发布了另外一款支持最新IEEE 1588协议的时钟芯片SI5388/SI5389,并且在全球主流的通信设备厂家配合Xilinx、Intel等平台进行了完整的同步测试。

【经验】如何优化时钟芯片Si5395P以保证高精度时钟输出?

为了进一步降低56G/112G PAM4 高速SerDes接口在各种数据通信设备中应用时的抖动需求,以实现更高速率、更大带宽的高速以太网和光传输设计,Silicon Labs公司推出了性能更佳的Si5395P时钟芯片。Si5395P对各个输出做了详细的优化,以更好地降低额外的抖动,本文就将详细说明如何规划各个输出时钟频点以保证高精度时钟输出。

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

【经验】Silicon Labs时钟芯片Si5332写入配置寄存后无频率输出解决方法

Si5332是Silicon Labs公司推出的任意频率的时钟发生器,被广泛应用于消费电子、电信传输网、基站、数据中心等。该芯片输出频率范围为5~333.33 MHz,具有175fs典型值的抖动性能,同时该芯片具有任意频点输出、可内置多组频率计划等特点。在应用中,Si5332在写入配置寄存器后,没有频率输出,该如何解决呢?本文将详细讲解。

【经验】通过配置输出时钟来优化抖动性能的方法-使用CBPro软件进行调整,以SI5345时钟芯片为例

Silicon Labs公司提供各种高速时钟信号发生器、抖动衰减器的芯片供应商。广泛用于传输网、移动回传网、接入网等设备。很多反馈使用CBPro软件配置频率计划时都会存在串扰警告,串扰问题会带通信质量问题,本文讲述配置输出时钟来优化抖动性能的最佳方式——使用CBPro软件进行调整。

电子商城

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥8.1764

现货: 101,879

品牌:SILICON LABS

品类:Mighty Gecko Multi-Protocol Wireless SoC

价格:¥27.0929

现货: 90,767

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥10.4994

现货: 50,699

现货市场

品牌:SILICON LABS

品类:Switch Hall Effect Magnetic Position Sensor

价格:¥2.2924

现货:126,000

服务

测试范围:扬兴晶振全系列晶体,通过对晶体回路匹配分析,调整频率、驱动功率和起振能力,解决频偏、不起振、干扰、频率错误等问题。技术专家免费分析,测完如有问题,会进一步晶振烧录/修改电路。

实验室地址: 深圳 提交需求>

使用FloTHERM和Smart CFD软件,提供前期热仿真模拟、结构设计调整建议、中期样品测试和后期生产供应的一站式服务,热仿真技术团队专业指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论