抖动性能可达到150fs以下的高效时钟解决方案

随着现代社会网络带宽的以及换联网基础设施和数据中心系统复杂度的增长,人们对时钟的频率、输出格式和电压也有了更高的要求。为了实现超高速网络,对于抖动性能的要求同样苛刻。由于传统时钟解决方案的灵活性和集成度的不足,硬件设计人员只能采用复杂的高成本时钟发生器和抖动衰减器组合方案来完成时钟树设计。SILICON LABS推出的Si5346/47抖动衰减器和时钟发生器,在单芯片上集成了分立时钟芯片功能,实现了一个简单高效的时钟解决方案。

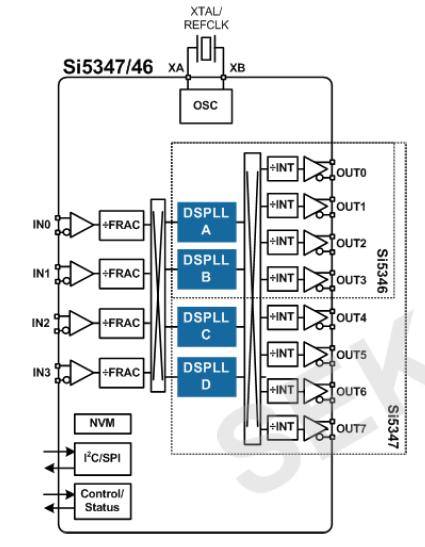

Si5347作为一款高性能抖动衰减器和时钟倍频器,集成了4个独立抖动衰减PLL,可以适应任何晶体或参考时钟频率;Si5346则是更小封装的双DSPLL版本;基于第四代DSPLL技术,该芯片的抖动性能可达到150fs以下,每个DSPLL都可向外部设备提供低抖动时钟输出,支持独立运行、保持运行以及无中断自动输入时钟交换功能,Si5347/46带有非易失性存储器,可使用Silicon Labs公司的Clock Builder Pro进行编程,同样支持出厂预编。

图一1:Si5346/47内部结构

Si5346/47可应用于抖动性能要求苛刻光传输网络、无线基础设施、宽带接入/汇聚、数据中心设备(边缘路由器,交换机,存储和服务器)等。

Si5346特性如下:

• 2个PLL

• 4个时钟输入,4个时钟输出

• 输入频率为8KHz~750MHz

• 输出频率为1KHz~800MHz

• 封装为44QFN 7X7mm

Si5347特性如下:

• 4个PLL

• 4个时钟输入,8个时钟输出

• 输入频率为8KHz~750MHz

• 输出频率为1KHz~800MHz

• 封装为64QFN 9X9mm

Si5346/47应用领域如下:

• OTN复用转发器

• 以太网交换机

• 网络线路卡

• 视频广播

• 同步以太网

- |

- +1 赞 0

- 收藏

- 评论 1

本网站所有内容禁止转载,否则追究法律责任!

相关推荐

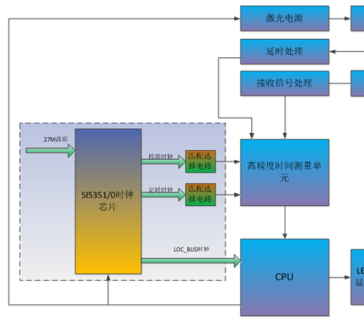

【产品】利用时钟发生器SI5351简化手持式激光测距仪设计

基于Silicon Labs SI5351单时钟芯片的手持式激光测距仪方案,测量部分多采用高精度时间测量单元电路实现测距。其中,SI5351可直接通过I2C接口配置,实现单一芯片取代锁相环、晶振、压控振荡器,能够有效减少系统BOM成本和PCB面积。

一款适合IEEE 1588V2的专用时钟芯片

Silicon Labs日前推出了专门实现IEEE 1588协议的超低抖动时钟芯片SI5348,这款芯片可以满足IEEE 1588 V2组网对系统时钟极其苛刻的指标要求,完美实现IEEE 1588 V2协议。

【产品】支持任意频率、任意输出的时钟发生器

基于Silicon Labs突破性的MultiSynth技术,Si5338能合成从0.16 至 350 MHz间的任何频率,并能在每个装置的四个不同输出选择高达700 MHz的频率。

【经验】高性能抖动衰减器时钟芯片Si5326的频率配置问题解析及替代方案推荐

Si5326是Silicon Labs推出的基于第三代DSPLL专利技术的高性能抖动衰减器时钟芯片,最近有工程师在做设计时要求Si5326输入为25MHz时钟,2路输出分别是25.8MHz和27.5MHz的3.3V时钟信号,使用DSPLLsim配置时,发现无论该2路时钟位置如何调换,无论如何调整分频比,输出频点都不能同时实现整个两个频点的输出。本文就将解答这一问题并给出替代方案。

【经验】Silicon Labs时钟芯片Si5332写入配置寄存后无频率输出解决方法

Si5332是Silicon Labs公司推出的任意频率的时钟发生器,被广泛应用于消费电子、电信传输网、基站、数据中心等。该芯片输出频率范围为5~333.33 MHz,具有175fs典型值的抖动性能,同时该芯片具有任意频点输出、可内置多组频率计划等特点。在应用中,Si5332在写入配置寄存器后,没有频率输出,该如何解决呢?本文将详细讲解。

时钟发生器Si5351的版本B和版本A有什么变化,推荐使用哪个版本?

时钟发生器Si5351目前主推版本B,版本B和版本A的主要变化有:(1)RevB:频率输出范围是2.5 kHz到200 MHz;RevA:8 kHz 到160 MHz。(2)输出阻抗RevB是50欧姆,RevA是85欧姆。(3)RevB不支持24-QSOP封装。

【经验】时钟发生器SI5338的LVDS匹配问题的分析测试案例

SI5338是Silicon Labs推出的一款经典的时钟发生器芯片,是一款目前广泛用于通信基站、传输网、政企网、数据中心、消费电子等多行业通用的时钟芯片。日常使用偶尔会碰到较多SI5338的应用问题,有寄存器配置的,也有输出匹配不一致的,对于寄存器问题,一般配合寄存器列表,可以简单较为容易的解决,对于匹配问题,也是SI5338时钟输出的重点关注部分,日前就有工程师碰到了一起LVDS输出匹配问题。

【应用】10路差分输出!DSP时钟电路中少不了这款时钟发生器

SI5341最大能支持10路差分输出,低抖动,完全满足DSP所需的时钟性能需求。

抖动衰减时钟芯片Si5381内部有4个独立DSPLL,其中DSPLLB的结构不同于其它的三个DSPLL,请简述各个DSPLL的具体作用?

Si5381内部自带4个独立的DSPLL,其中专门为实现无线基站设备时钟配置的锁相环是DSPLLB,DSPLLB的输出范围最高可达1.47456 GHz,环路带宽范围是10 Hz ~ 100 Hz,支持高速接口JESD204B的DCLK 和 SYSREF时钟处理。其它DSPLLA/C/D可以作为普通时钟发生器DSPLL使用,其输出范围和带宽范围相对DSPLLB要窄,可以作为普通本地总线、交换芯片等设备的参考钟使用。

想提高网络数据中心的速率?非要频率灵活时钟发生器不可!

Si5341/4元件能产生任何频率,在整数模式中不到100 fs RMS,在小数合成模式中不到150 fs RMS,将成为未来高速网路和数据中心不可或缺的关键设计元素。

Silicon Labs(芯科科技) Si5380时钟发生器数据手册(简略版)

描述- Si5380是一款基于Silicon Laboratories第四代DSPLL技术的整数时钟发生器,专为小型基站应用设计,提供高集成度和相位噪声性能。该器件结合了频率合成和抖动衰减功能,无需外部VCXO和环路滤波器组件,采用低成本固定频率晶体振荡器保证频率稳定性。

型号- SI5380-D-EVB,SI5380-A-ZXM,SI538X,SI5380

Silicon Labs(芯科科技) Si5345, Si5344, Si5342系列抖动衰减器/时钟倍频器 参考手册

描述- 本资料为Si5345/44/42系列时钟倍频器家族参考手册,旨在为系统、PCB设计、信号完整性及软件工程师提供使用这些器件的技术信息。手册涵盖了DSPLL和MultiSynth技术的应用,支持任意频率的时钟生成,并提供编程接口和多种操作模式。资料详细介绍了器件的工作原理、功能特性、配置方法以及电路布局建议。

型号- SI5345A-B-GM,SI5344C-B-GM,SI5345D-B03700-GM,SI5345D-B04500-GM,SI5345B-B04564-GM,SI5344B-B04184-GM,SI5345D-D-GM,SI5345C-A-GM,SI5345B-B-GM,SI5344D-B-GMR,SI5345B-B04881-GM,SI5345D-B04831-GM,SI5344D-B-GM,SI5342D-B05470-GM,SI5345A,SI5345A-B-GMR,SI5345B,SI5345C,SI5345B-B05955-GM,SI5345D,SI5342A-B-GM,SI5345B-B05785-GM,SI5345D-B05731-GM,SI5342D-D-GM,SI5345A-A-GM,SI5345B-B05747-GM,SI5345D-B04501-GM,SI5348B-B05856-GM,SI5342B,SI5342C,SI5342D,SI5342B-B-GM,SI5345D-B04409-GM,SI5348B-B05083-GM,SI5344A-B-GM,SI5345B-B04823-GM,SI5345B-B05971-GM,SI5342C-D-GM,SI5345B-B00021-GM,SI5345B-B06003-GM,SI5348B-B05423-GM,SI5344B-D-GM,SI5342A,SI5345C-D-GM,SI5345B-B-GMR,SI5345D-B04493-GM,SI5345D-B04502-GM,SI5345D-B-GM,SI5345D-B05784-GM,SI5342C-A-GMR,SI5345B-D-GM,SI5345A-D-GM,SI5342A-D-GM,SI5345B-B04421-GM,SI534X,SI5348B-B05017-GM,SI5345A-B04313-GM,SI5345B-B04408-GM,SI5342D-B-GM,SI5345D-B04494-GM,SI5345D-B04528-GM,SI5345C-B-GM,SI5345B-B05825-GM,SI5344D,SI5342B-D-GM,SI5345D-B04834-GM,SI5345B-B04563-GM,SI5342D-B04694-GM,SI5344D-D-GM,SI5345A-B04313-GMR,SI5345A-B04957-GM,SI5344A-D-GM,SI5345D-B04830-GM,SI5345D-B05729-GM,SI5344B-A-GMR,SI5345D-B04410-GM,SI5345A-A-GMR,SI5345B-B03718-GM,SI5342D-B03814-GM,SI5344A,SI5345B-B03234-GM,SI5344B,SI5344C,SI5345B-B05786-GM

【经验】论开启OFF检测功能对SI5347高性能抖动衰减器的重要性

工程师使用SI5347时,首先要开启OOF检测功能,否则将导致锁相环长期处于校准状态,无法正常锁定。

时钟发生器Si5351的I2C工作正常,但是PLLA的时钟倍频不上去不能正常输出148.5M的时钟,请问是什么原因?

Si5351是一款I2C可配置时钟发生器,基于MultiSynth分数分频器的结构,可以以0 ppm误差输出任意高达200MHz的时钟频率。Si5351的时钟配置过程需要按流程进行,配置频率修改寄存器后必须配置初始化寄存器(软复位),该问题原因是修改频率配置寄存器后没有继续配置软复位寄存器。

用TCXO产生25M时钟作为时钟发生器Si5335D的输入信号,实测输出信号有多达20Hz的频率偏差,请问是什么原因?

Si5335D是线性时钟发生器,输出频率与输入频率偏差完全相同,如果输入有较大频率偏差,输出也会有较大频率偏差。一般TCXO的稳定度在±1ppm以内,25M换算成频率偏差量就是25*1000000/1000000Hz=25Hz,所以20Hz的频率偏差是可能存在的。

电子商城

现货市场

服务

提供CE测试服务,通过晶体回路匹配分析,给出测试报告。支持EPSON所有MHz无源晶体、32.768KHz晶体。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳/上海 提交需求>

测试范围:扬兴晶振全系列晶体,通过对晶体回路匹配分析,调整频率、驱动功率和起振能力,解决频偏、不起振、干扰、频率错误等问题。技术专家免费分析,测完如有问题,会进一步晶振烧录/修改电路。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论