【经验】SATA物理层一致性测试案例分享

SATA——Serial Advanced Technology Attachment , 由Intel、APT、Dell、IBM、希捷、迈拓这几大厂商组成的Serial ATA委员会正式确立了Serial ATA 1.0规范,70个公司联合开发制定的一种新的硬盘串行传输规范。本文中Misenbo将与大家分享SATA物理层一致性测试案例。

SATA特性:

1、以串行方式传输数据,一次只传输1位数据。这样的结构在较少位宽下可以使用较高的工作频率来提升数据传输的带宽。

2、串行方式使SATA接口使用更少的接线引脚,接口分为信号与电源两部分。

3、具有低功耗,支持热插拔,差分信号保证传输准确性等优势,内置数据校验,具备更强的纠错能力。

SATA应用:

SATA在接口的规范和定义、功能及使用方法上与普通硬盘的完全相同,在产品外形和尺寸上也完全与普通硬盘一致。被广泛应用于军事、车载、工控、视频监控、网络监控、网络终端、电力、医疗、航空、导航设备等诸多领域。

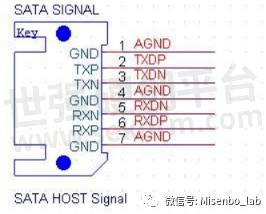

SATA信号接口定义:

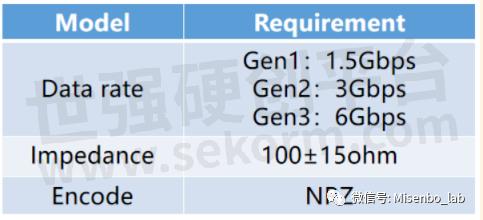

SATA电气特性分类:

SATA层分类:

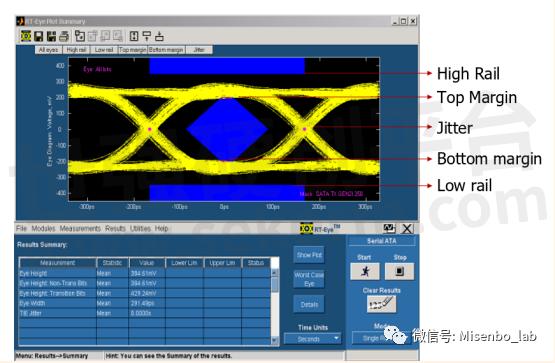

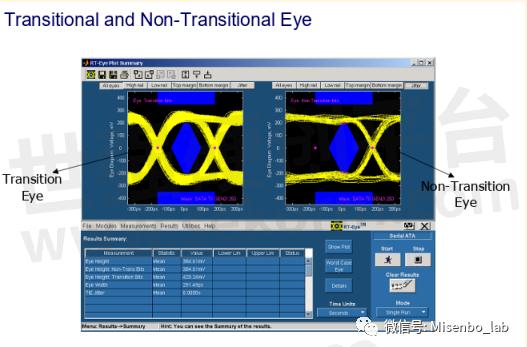

SATA3.0 物理层一致性测试项目

PHY/TSG/OOB测试

RSG(接收端测试)

Rx/Tx和SI测试

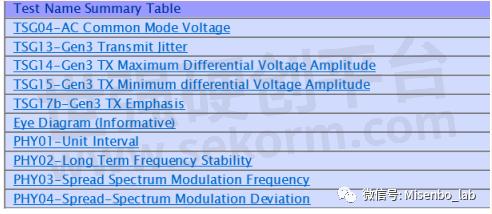

PHY/TSG测试项目:

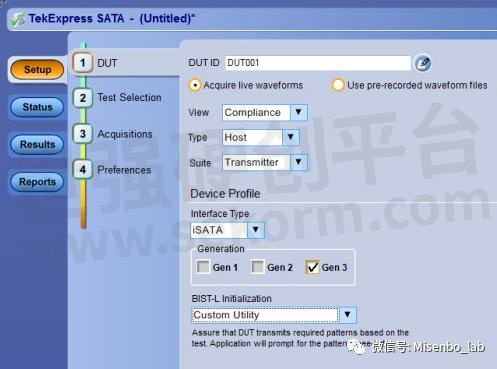

SATA3.0测试环境:

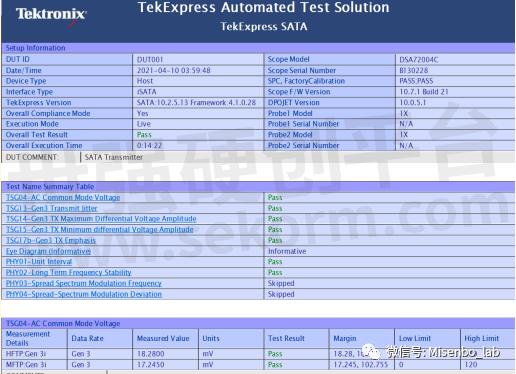

示波器,Tektronix DSA72004C示波器带宽20GHZ,

测试夹具,专用SATA3.0

测试软件,专用

测试探头,SMA-292M

DUT准备好测试码型或信号发生器

SATA3.0测试方法:

AWG方法

使用AWG提供激励源

使SATA/SAS设备产生ALIGN Test Patterns

BIST FIS(Built In Self Test Frame Information Structure)Method

配置SATA/SAS的寄存器强制其处于测试模式。

配置SATA/SAS的寄存器强制其发送不同的测试Pattern。

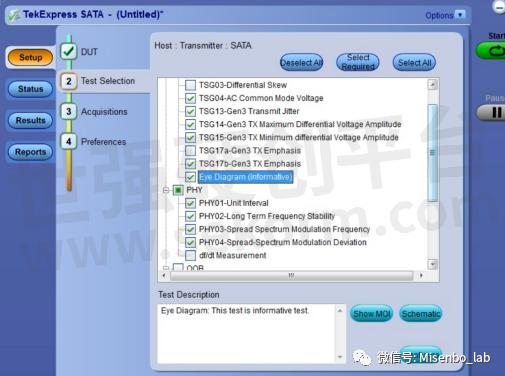

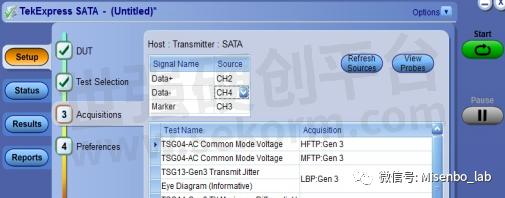

SATA-测试流程:

1、建立测试环境

2、配好软件

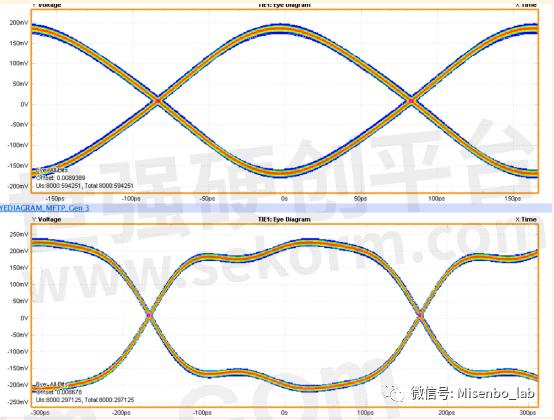

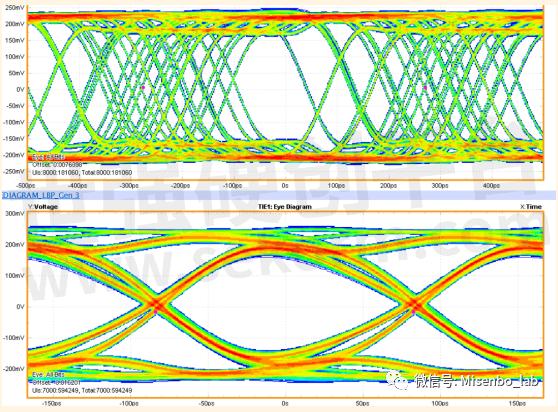

SATA测试码型

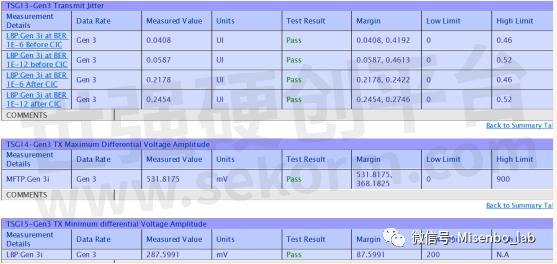

HFTP(High Frequency Test Pattern)高频测试码型,1010101010 1010101010b,即重复的D10.2。

MFTP(Middle Frequency Test Pattern)中频测试码型,1100110011 0011001100b,即重复的D24.3。

LFTP(Low Frequency Test Pattern)低频测试码型,0111100011 1000011100b,即重复的D30.3。

LBP(Lone-Bit Pattern)单独位码型,主要用于测试SATA性能。

CJPAT(Compliant Jitter Tolerance Pattern),一致性抖动容忍度码型

SRAMBLE_0 Pattern 主要用于测试SAS 1.5, 3 and 6 Gbps WDP性能

IDLE dwords pattern 主要用于SAS 12 Gbps测试,配合 SAS3_EYEOPENING script

3、调用示波器测试软件

4、测试报告

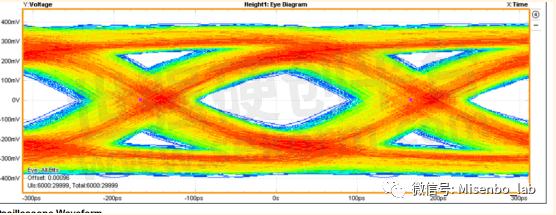

SATA眼图测试:

若是因为DUT不能配置寄存器不能发码型也没有专用的信号发生器,推荐测试一下SATA的眼图信号质量。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由Jessica_li转载自淼森波公众号,原文标题为:【测试那点事儿】SATA 物理层一致性测试,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

HDMI闪屏故障的成因及相应的解决方法

在现代多媒体设备中,HDMI(高清多媒体接口)是连接显示器与电脑、游戏机等设备的主流方式。然而,许多用户在使用HDMI连接时会遇到闪屏现象。本文Misenbo将探讨该问题的成因及相应的解决方法,帮助用户快速排查和修复问题。

设计经验 发布时间 : 2024-11-20

解析LPDDR4硬件设计及测试注意事项

LPDDR4(Low Power Double Data Rate fourth generation)是一种低功耗的存储器标准,用于移动设备和便携式应用。本文中Misenbo为大家介绍LPDDR4硬件设计及测试注意事项。

设计经验 发布时间 : 2023-12-30

MIPI接口闪屏怎么解决?

在现代移动设备中,MIPI(移动行业处理器接口)因其高速串行数据传输能力被广泛应用于显示屏和摄像头模块。然而,用户在使用这些设备时可能会遇到闪屏现象,即图像频繁闪烁或不稳定。本文将深入探讨MIPI接口闪屏的成因及解决方案。

设计经验 发布时间 : 2024-11-08

详解DDR技术内核 及Layout注意事项

这些是一些常见的DDR走线规则,当然,具体的规则可能因DDR版本、芯片厂商和PCB设计要求而有所不同。在进行DDR走线设计时,务必参考相关的DDR规范和芯片厂商的建议,以确保良好的信号完整性和性能。

技术探讨 发布时间 : 2023-11-01

DDR芯片的PCB设计要点

DDR PCB布局设计需要考虑诸多因素,包括DDR规格、频率、时钟速度等。因此,确保与DDR芯片厂商的规格和设计要求保持良好的沟通和协作,是非常重要的。

技术探讨 发布时间 : 2023-12-01

解析DDR信号完整性测试内容、技巧及注意事项

DDR(双数据速率)信号完整性测试是对DDR系统中信号传输的稳定性和准确性进行验证的过程。那么关于DDR信号完整性测试的内容、技巧及注意事项您有了解吗?本文将为您进行详细介绍。

技术探讨 发布时间 : 2024-05-09

【经验】淼森波实验室DDR测试案例,如何区分DDR1,DDR2,DDR3,DDR4还有DDR5?

DDR1、DDR2、DDR3、DDR4和DDR5都是不同类型的同步动态随机存取存储器,它们提供了不同的性能和带宽,并不断演进和发展。 都是不同类型的内存规格,它们的速度、带宽、工作电压和能耗等方面都有所不同,DDR5 内存规格最高,速度最快,带宽最宽,能耗最低。

设计经验 发布时间 : 2023-08-01

LVDS闪屏的原因及解决办法

LVDS(低电压差分信号)闪屏问题通常指的是显示屏在使用过程中出现闪烁或不稳定的现象。本文将为您介绍 LVDS(低电压差分信号)闪屏的原因及解决办法。

设计经验 发布时间 : 2024-09-06

DDR3信号速率问题详解

MISENBO实验室探讨了DDR3内存速率不足的问题,指出时序、信号质量、串扰、电源噪声和等长匹配是主要原因。建议使用等长设计、差分信号、优化电源和终端电阻来解决这些问题。实验室提供高速信号测试和硬件研发服务,帮助提升DDR性能。

技术探讨 发布时间 : 2024-11-04

【应用】淼森波MIPI/LVDS/FPDLINK/GMSL/以太网等多种智能座舱信号完整性测试案例分享

Misenbo森波实验室测试了智能座舱的多种信号的完整性,帮客户解决了许多信号完整性的问题,本文将为大家分享淼森波MIPI/LVDS/FPDLINK/GMSL/ 以太网/DP/USB3.0/USB2.0测试案例。

应用方案 发布时间 : 2023-06-28

SI/PI信号完整性测试

SI/PI信号完整性测试的重要性SI(Signal Integrity)和PI(Power Integrity)信号完整性测试在现代电子设备设计和制造中非常重要。以下是SI PI信号完整性测试的重要性、SI/PI信号完整性测试内容和案例。

设计经验 发布时间 : 2024-03-13

1000M以太网信号测试不过,咋办?

1000M以太网物理层一致性测试中模板测试不过,通常表明被测试设备(DUT)在物理层上未能满足IEEE 802.3标准中规定的要求。物理层是OSI模型的第一层,主要负责在介质上发送和接收原始比特流。要解决此类问题,通常需要从以下几个方面去入手。

设计经验 发布时间 : 2024-10-26

【经验】解析HDMI Sink一致性测试及眼图测试案例

HDMI测试主要有Source端测试、Sink端测试、单项眼图信号质量测试。Source端测试已介绍、接下来淼森波实验室分享HDMI的Sink端一致测试、Sink端眼图文测试。

设计经验 发布时间 : 2023-09-01

eMMC信号完整性测试注意事项分享

本文中Misenbo将为大家分享eMMC信号完整性测试的注意事项,希望对各位工程师朋友有所帮助。

设计经验 发布时间 : 2024-01-25

1000M以太网信号测试不过怎么办?

1000M以太网物理层一致性测试中模板测试不过,通常表明被测试设备(DUT)在物理层上未能满足IEEE 802.3标准中规定的要求。物理层是OSI模型的第一层,主要负责在介质上发送和接收原始比特流。

设计经验 发布时间 : 2024-10-26

服务

根据用户的接口模块,使用是德示波器及夹具查看实时眼图演示,测试USB/MIPI/DDR/SATA/HDMI协议,支持最高到1.2GHz的实时眼图协议测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

使用FloTHERM和Smart CFD软件,提供前期热仿真模拟、结构设计调整建议、中期样品测试和后期生产供应的一站式服务,热仿真技术团队专业指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论