Keysight解决和测试方案轻松应对5G及云计算和大数据时代的PCI Express4.0/5.0应用挑战

PCI Express作为二十年来电子和通讯产业界发展最为成功的数字标准之一,在近年随着云计算和大数据的蓬勃发展以及今年的5G商用启动呈现加速趋势。本文对5G加速部署背景下的各标准的发展与应用场景及当前的挑战作一简单介绍。

近两年来,在5G加持下,PCI-Sig组织开始进入“暴走模式”。当前在PCIE4.0尚未完成全面商用的情况下,PCIE5.0 Base1.0规范刚刚发布,就迫不及待地在19年Q3公布了PCIE6.0 Base 0.3规范。

一、PCI Express标准应用场景

PCI-Sig组织当前真正演绎了什么叫“筷子上夹一个,眼睛同时还盯着碗里和锅里”。

那么是什么样的市场和应用场景造成了今天这样的三箭齐发的局面?下面这幅图充分说明了当前的迫切状况和压力:

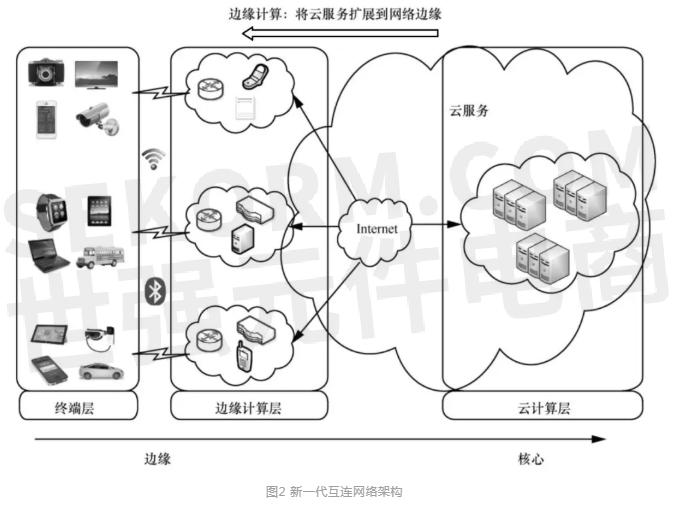

云计算和大数据发展到2019年,叠加5G商用开始启动,以及以车联网和智能驾驶为主导推动发展到未来智慧城市的建设,万物互联和海量数据时时刻刻均在生成对传统的星形核心状互联网络架构的传输带宽产生巨大压力,近几年高速光电接口模块的长足发展也衬托出全网络的带宽瓶颈已经从外部系统互连接口(即各种光电模块)转移到内部的高速处理器和外部接口之间。

同时海量数据对传统的围绕核心网进行通讯和计算的架构也带来巨大挑战,因此对海量数据进行分层并采用分布式或者混合架构计算成为必然。因次基于成本的考虑,需要不同速率的标准未来适用于不同的应用场景或级别。

典型地,PCIE3.0/4.0将广泛用于数据和信息汇聚设备即终端,包括PC/NB,智能电话以及汽车等设备;

PCIE4.0/5.0则会用于边缘计算层,比如5G基站配套或智能网联汽车接入网关设备等;

而PCIE6.0则会用于核心网数据中心和服务器设备。

当前「PCIE3.0」已经成熟应用在传统的PC/笔记本和服务器以及采用U.2或M.2接口的SSD存储设备上,乃至移动终端设备的AP与Wifi芯片连接。

「PCIE4.0」已经完成在服务器产品初期样机开发阶段,今年9月在中国上海,产业界上游公司完召集国内主要服务器厂家成了第一次Plugfest测试

而「PCIE5.0」在完成Base规范制定后,预计在2020会完成CEM规范,迈向正式商用。PCIE5.0依然采用NRZ编码实现32GT/s传输,在X16链路宽度配置下提供对400Gbps光电接口的强力支撑。针对未来核心网的更高传输要求即800Gbps则留待「PCIE6.0」的部署。

事实上,PCI-Sig组织依托其背后强大的业界产业链上游成员单位的支持和影响力,其开发的标准已经不仅在X86处理器领域获得巨大成功,而且在多种架构如Power等均在采用。而近几年,业界开发的几种基于不同平台和架构处理器进行异构计算的总线尤其是在AI(人工智能)应用领域,如CCIX、OpenCAPI、GenZ等底层多是基于PCIE标准。

在今年上半年I公司新发布的标准CXL,其物理层当然也将采用PCIE标准。在可预期的未来,PCIE标准将统一高速计算平台和处理器系统内的互连接口。因此今天对PCIE标准无论如何强调其重要性和对高速数据传输和通讯产业的价值都毫不过分。

二、标准快速迭代带来的挑战

近10来年PCIE标准快速迭代带来的物理层设计和测试巨大挑战,主要体现在如下几个方面:

① 信号速率快速倍增的同时信号幅度和眼高在快速压缩

信号速率在近几年的迅猛增长的同时,对应的是在接收端信号幅度的持续压缩。在PCIE3.0时代,接收端眼高35mV,到4.0标准,眼高只有20mV左右。PCI-Sig最初规划PCIE5.0,眼高在10mV左右。最终在Base规范发布时,重新定义为15mV。这一5mV的眼高增量,主要是相对于PCIE4.0标准在32Gbps速率上采用了更强的CTLE和3-tap DFE,并且要求采用低损耗板材,这一增量期望最终能够在实际产品化过程中缓解业内的仿真设计开发人员和信号完整性及测试工程师的压力。

然而这一眼高实际是在接收端均衡后必须达到的眼高,实际上在均衡前眼睛是完全闭合的。即便如此,这一要求对传统的8bit示波器还是产生巨大压力。除了8bit示波器本身的有限的量化等级之外,还有随着信号频率提高示波器带宽的延展其本底噪声也在扩大,因此动态有效位数在持续下降。

比如典型地,业界许多8bit实时示波器到25GHz带宽时ENOB只有4位左右,已经严重影响测量精度,KEYSIGHT最新UXR则可以达到6.2位。考虑到未来PCIE6.0 64GT/s,将采用PAM-4电平,相对NRZ电平调制方式信噪比减小9.6dB,因此对示波器的本底噪声和动态有效位会带来更大挑战。总之,未来针对信号继续迈向高速、低幅度和更低的裕量方向,10bit示波器必将成为主流。

② 发送端和接收端均衡日益复杂导致互动链路训练(Interactive Link Training)日益复杂

在TX EQ方面,

• PCIE标准从早期的1.0a/1.1标准的单一的3.5dB Pre-Emphasis/De-Emphasis;

• 到之后2.0标准的3.5或6dB的De-Emphasis;

• 再到PCIE3.0时代的引入3-Tap FIR 滤波器实现TX EQ,除了跳变后的De-Emphasis之外还有跳变前的Pre-Shoot,基于此定义了常见的11种Preset组合;

• 在PCIE4.0则基本保留了PCIE3.0标准的TX EQ定义和组合。11种组合信号中必须有一种通过或符合规范要求。

在RX EQ方面,

• 从PCIE3.0开始就在接收端引入了CTLE+1 Tap DFE。

• 在PCIE4.0标准,接收端采用CTLE+ 2 Tap DFE。

• 而当前5.0规范中,则采用CTLE+3-tap DFE。

(CTLE,英文名称Continuous Time Linear Equalizer)

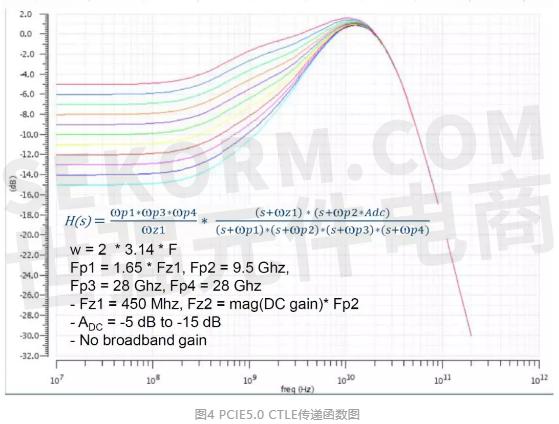

PCIE5.0 CTLE传递函数如下图示:

从上图可以看到,CTLE原理是对部分频段的信号进行放大以弥补链路的传输损耗。在实际的测试过程中,由于示波器固有的信号路径和AD采样芯片引入的噪声叠加到信号上,在后期进行均衡算法处理时在放大信号的同时会放大信号采集和处理路径的本底噪声,因而引入测量误差,这一误差对PCIE5.0有限的15mV的眼高可能是致命的。因此低本底噪声和高ADC位数及ENOB示波器对未来5.0测试意义将更显重要。

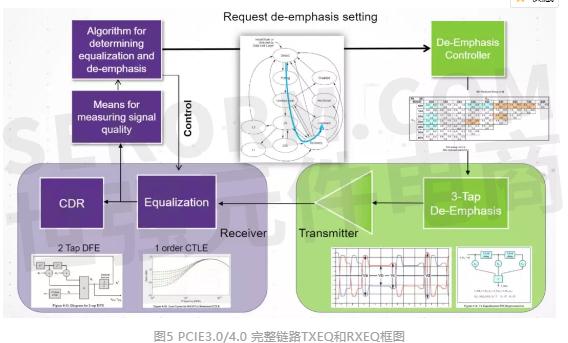

下图是PCIE4.0完整链路的TXEQ和RXEQ框图。

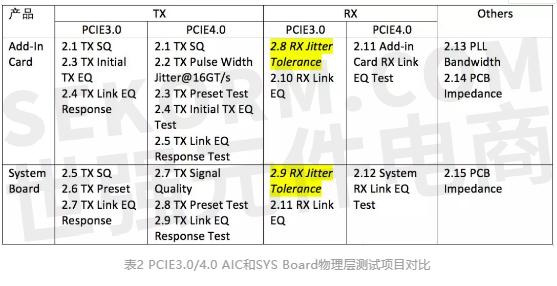

针对这一复杂的协商机制,PCI-Sig在PCIE4.0 CEM标准针对RX测试相对以往PCIE3.0做出了修改。以往PCIE3.0 RX测试中的Jitter Tolerance项目在PCIE4.0已经拿掉,更注重Link EQ测试,无论在发送端还是接收端。

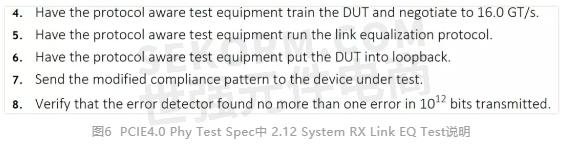

以2.12项目为例,在规范中明确说明需要“Protocol aware”设备即BERT训练DUT到16.0 GT/s,运行链路均衡协议并设置DUT到环回模式后再发送一致性码型,经过DUT环回到误码检测模块后进行BER测试。

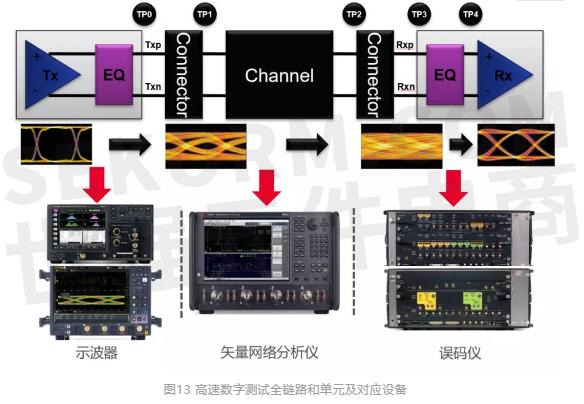

在这一测试项目中,对误码仪的协议感知能力要求越来越高。另外实时示波器也是必不可少的工具,示波器主要有两个作用。

一个是针对误码仪发出的信号进行精确校准以确保误码仪发出的信号经过电缆和夹具等连接输出到被测设备的端面时完全符合规范。

另外示波器还用于测试2.5和2.9——TX Link EQ Response Time,由误码仪发出设置命令以要求DUT发出某个Preset,然后示波器通过捕获到的波形观察DUT是否在规范要求的1ms内响应这个命令。

从P0到P9,需要全部遍历一遍。可以看到在规范要求的1ms的反应时间内,假定以80 GSa/s采样,那么存储深度则要求80M点以上,这一要求远高于眼图测试的2M UI样点。事实上,当前Keysight 支持PCIE4.0/5.0测试的示波器Z/UXR系列均提供了最低100M/CH的存储深度,充分满足这一测试要求。

下图即为TX Link EQ Response Time实测波形,从中还可以看到为了准确观察这一响应过程,还启用了PCIE协议解码应用,也就是说协议解码和触发对PCIE测试也是一个重要工具。

总体来看,在今天的PCIE4.0测试中,实时示波器和误码仪两台设备协同工作,二者缺一不可。当然如果采用同一品牌设备将对测试联调和协调及除错带来极大的便利性。

③ 时钟传递系统和架构中的抖动要求越来越高

从PCIE4.0开始,时钟传递系统和架构主要采用两种:

• CC(Common Clock)架构

• IR(Independent Reference CLK)架构

IR又分成两种:

• SRIS(Separate Reference Clocks With SSC)

• SRNS(Separate Reference Clocks With No SSC)

未来在PCIE5.0时代,各种时钟架构采用状况如下表:

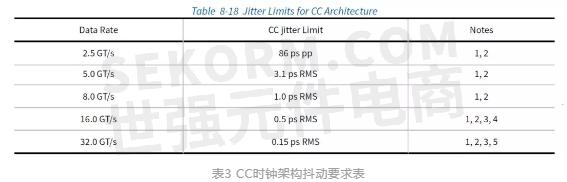

在无Riser扩展槽情况,必需使用CC时钟架构,同时其抖动指标日益严苛,到PCIE5.0标准,CC Jitter最低为0.15ps,采用0.5MHz PLL带宽——1.8MHz CDR带宽范围滤波器进行滤波处理,主要以Rj形式体现:

这一测试要求对今天的实时示波器指标要求已经达到极限,对示波器的固有抖动及通道间偏差都提出了很高的要求。因此未来采用相噪分析仪(Phase Noise Analyzer)进行测量已经成为一种可能,但是这对产业界来说是一笔额外的投资开销,因为相噪分析仪在传统的数字应用领域功用有限。

Keysight Z系列示波器以单一平台实现4通到33Ghz带宽,提供最低75fs抖动。UXR系列10bit实时示波器单一平台提供业界最高四通道带宽13GHz-33GHz@128GSa/s,40-110GHz@256GSa/s,最小25fs固有抖动,在当前PCIE5.0早期的时钟测量中已经显现出明显的优势。另外业界其它一些采用多个机箱拼凑实现2/4通道33GHz或50GHz带宽除了本身单台机箱的固有抖动外,其不同机箱通道间的时间偏差会带来额外的测试误差,导致最终测试不能通过。

另外为了满足PCIE5.0标准的这一严苛要求,Keysight除了在硬件上提供多种高性能的平台外,在软件和算法上也在配合PCI-Sig组织进行更多的有益的改进和建议,包括推出了基于实时示波器的「相位噪声分析选件」(Phase Noise Analyze),以及在抖动分软件里提供去除或采用外部信号源校准示波器的抖动和底噪的功能,以期望通过提过实时示波器测量精度的方法来满足新的应用挑战,降低额外的投资成本。

④ 信号传输链路的设计和测试要求越来越高

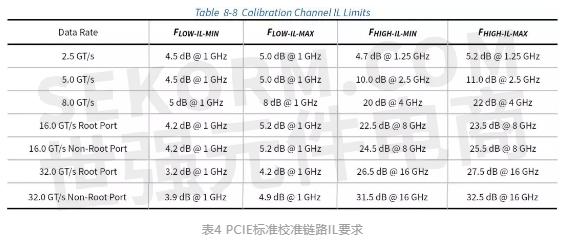

最新的PCIE5.0 Base1.0规范里给出了各种架构和速率下信号传输链路典型频点插入损耗的最低和最高要求如下表示,可以看到正负偏差在0.5-1dB左右,足见要求之高和严格。

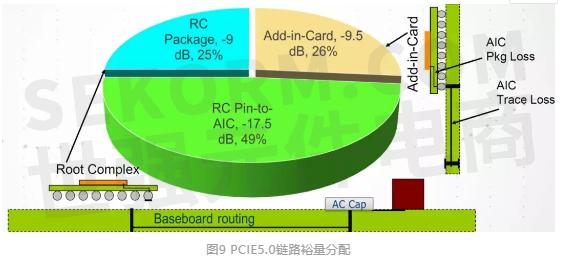

如果计入RX端的封装损耗,PCIE4.0 16GT/s总体链路损耗目标在27-30dB@8GHz,而PCIE5.0当前目标为36dB@16GHz。PCIE5.0全链路裕量分配如下图:

鉴于PCIExpress标准最初仅用于支持IA架构的PC和传统服务器,因此对成本的敏感度非常高。一直到PCIE3.0 8Gbps,依然在传统FR4板材上实现。发展到PCIE4.0,FR4板材已经很难保证信号能经过两个以上连接器和长达12英寸的链路后还能保持足够的信号完整性,无论采用多么强大的TX EQ和RX EQ也不能实现信号的可靠传输。因此要么采用低损耗板材比如Megtron-4或者增加Retimer芯片。

到底采用什么方案需要从两者的成本进行权衡,而且如果采用前期的仿真设计可以帮助做出更好的判断和取舍。这一判断对未来边缘计算的进一步发展尤为重要,因为边缘计算层的中端性能服务器需求和市场可能极大,产品放量的时候成本就成为市场竞争的关键因素之一。

而发展到未来PCIE5.0标准实现32G T/s时,甚至可能需要采用更昂贵的Megtron-6板材乃至直接采用高频电缆线束传输信号。

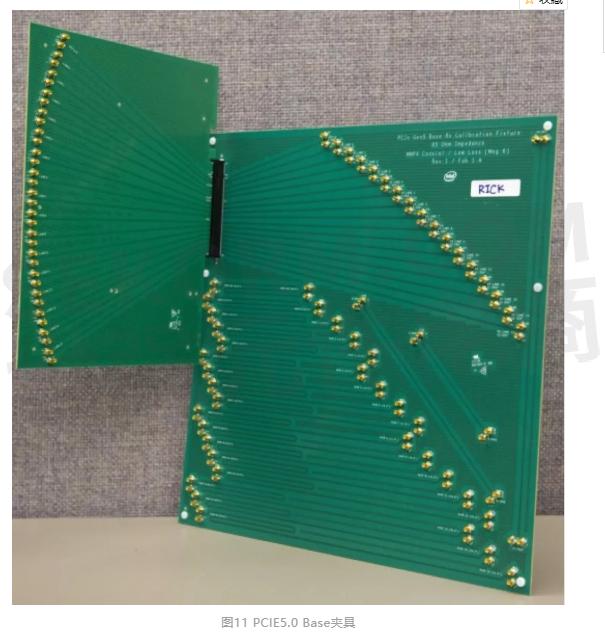

在前两个月,PCIE5.0 Base RX校准和测试夹具也已经上线。

上图即为PCIE5.0 Base RX校准和测试夹具。左边的卡是Variable ISI Base Spec Riser Card,右边的是Base RX Calibration夹具。

仔细观察可以看到为了确保信号完整性,CEM连接器开始采用SMT表贴,夹具上的连接头也采用了MMPX连接器。另外其材质在夹具上也标明了采用Megtron-6板材,阻抗为85欧姆

不管未来到底要如何多快好省地实现信号在物理链路层的可靠传输,网络分析仪对PCIE标准的成功部署已经成为必备工具了。事实上,今天的网络分析仪不仅具备强大的频域参数测试能力如IL,RL等,还可以增加TDR(时域反射)选件,完成阻抗测量,支持PCIE PHY Test Spec标准里规定的针对AIC和Sys-Board的2.14和2.15阻抗测试项目。

通过最近在上海举行的PCIE4.0 Plugfest活动发现在做RX测试前除了例行针对包括Variable ISI夹具在内的全链路进行标定并选择总链路损耗在27-30dB之外,由于针对多个项目及多个链路反复插拔测试,发现反复多次插拔和连接之后夹具上的SMP连接头容易出现过劳和损伤进而导致夹具的信号完整性下降,因此在大批量测试情况下需要不定期采用网络分析仪进行测试标定,目前看来至少1-2周需进行一次标定测试。也就是说,网络分析仪的使用频度大大超出了我们早先的认识。

以上对当前PCIE4.0/5.0标准的发展演进和已经和即将遇到的挑战略谈了几个方面,挂一漏万,不足或错误之处欢迎指出。

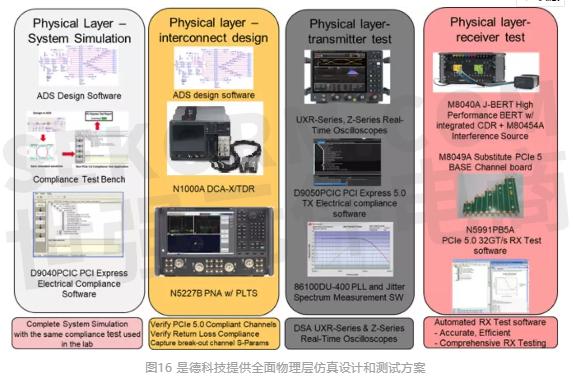

三、是德科技助产业界轻松应对挑战

挑战与机遇并存,挑战越大则意味着征服之后的回报越高。要想征服这一巨大挑战,Keysight公司全面的解决和测试方案涵盖:

• 高性能实时示波器Z/UXR系列提供业界精度领先的发送端测试能力;

• M8020A误码仪用于RX接收端测试,具有高集成度,超强的协议感知能力,或者高性能误码仪M8040A,直接支持后升级最高到64G Baud NRZ 或PAM-4速率信号(等效实现128Gb/s速率NRZ),单台设备全面支持当前PCIE4.0,以及PCIE5.0,通过软件升级支持未来3年后的PCIE6.0标准PAM-4信号;

• 丰富的网络分析仪产品,带宽最高110GHz和强大的软件功能,包括阻抗测试用TDR选件及传输链路测试验证用PLTS软件;

• 以及Pathwave ADS软件High Speed Digital模块可以提供功能强大的前期仿真设计和开发软件——为产业界的各路精英提供最佳的设计开发服务和测试验证保障!

针对PCIE5.0测试,Keysight目前已经可以提供分别针对TX和RX测试的软件。如下图示:

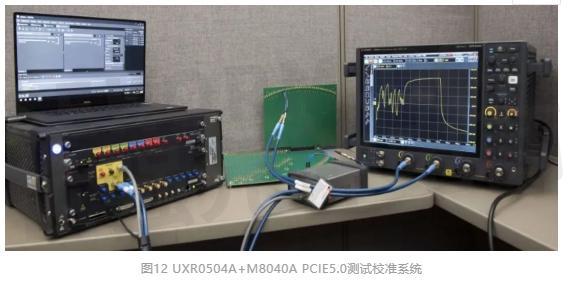

产业界上游I公司在2019年PCI-SIG开发者大会上,发表文章《Design and Analysis of 32GT/s SerDes for PCIe 5.0 in 10nm》,展示其实验室用于验证PCIe5.0的测试环境,设备为M8040A及DSAZ634A,目前该系统在I公司已经广泛采用。

另外一家上游IP供应商S公司宣布DesignWarePHY IP满足PCIe 5.0 基础规范1.0版本,并公开其实验室基于M8040A和DSAZ634A的芯片验证和演示视频。

此外还有业界其它前沿FPGA和IP公司也都在采用Keysight测试方案进行早期的PCIE5.0 32GT/s验证。

总结,高速数字科技发展到今天,早已经不是当年仅仅依据参考设计就能完成项目开发的时代。“工欲善其事,必先利其器”,或者“没有金刚钻,揽不了瓷器活”,测试工具和设备保障是必不可少的。当然,选择正确的合作伙伴也是成功的必要条件。是德科技作为业界唯一一家拥有三级研发体系:从核心芯片研发到硬件平台研发再到应用层解决方案研发的厂家是业界唯一提供从仿真设计,到物理层囊括发送端,传输链路和接收端测试的全面测试方案供应商,是更值得信赖的合作伙伴。

环顾业界,其它公司一般只能提供部分测试产品或方案,因此在今天日益普遍的几十个Gbps速率的如此高难度的设计和开发挑战面前,常常只能看到局部,或者需要多家协调配合,其中必然存在许多不确定性,自然无法提供足够的支持和保障。

真实案例:

业界在今年进入PCIE4.0正式测试时,个别几家服务器厂商因为早先的误码仪选择不当导致PCIE4.0接收端链路互动训练失败,无法进入环回导致测试不能进行进而延误项目转产交割,造成重大投资浪费,值得反思,不可不察!在最近的PCIE测试Workshop上也发现不同厂家设备搭建测试系统时,发生因为多种软件升级步调不一和协调不畅等引发的自动化测试的兼容性问题,不仅导致误工误时而且严重影响项目进度。

- |

- +1 赞 0

- 收藏

- 评论 215

本文由CrazyFeng转载自Keysight,原文标题为:5G及云计算和大数据时代的PCI Express4.0/5.0发展和应用挑战,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关研发服务和供应服务

评论

全部评论(215)

-

![]()

![]() 善感的灵魂 Lv7. 资深专家 2020-02-13学习

善感的灵魂 Lv7. 资深专家 2020-02-13学习 -

![]()

![]() lizzy Lv5. 技术专家 2020-02-10谢谢分享

lizzy Lv5. 技术专家 2020-02-10谢谢分享 -

![]()

![]() 朱朋 Lv6. 高级专家 2020-02-09学习讯息

朱朋 Lv6. 高级专家 2020-02-09学习讯息 -

![]()

![]() 独角兽 Lv9. 科学家 2020-02-08不错

独角兽 Lv9. 科学家 2020-02-08不错 -

![]()

![]() 用户14629492 Lv7. 资深专家 2020-02-07学习

用户14629492 Lv7. 资深专家 2020-02-07学习 -

![]() Microwave Lv7 2020-02-07学习

Microwave Lv7 2020-02-07学习 -

![]() Microwave Lv7 2020-02-07学习

Microwave Lv7 2020-02-07学习 -

![]()

![]() Hard Lv8. 研究员 2020-02-05学习了

Hard Lv8. 研究员 2020-02-05学习了 -

![]()

![]() 飞哥哥 Lv7. 资深专家 2020-02-04学习

飞哥哥 Lv7. 资深专家 2020-02-04学习 -

![]()

![]() 真大虫无双 Lv8. 研究员 2020-01-31Mark~

真大虫无双 Lv8. 研究员 2020-01-31Mark~

相关推荐

【经验】如何快速使用示波器DSO9404A实现一键眼图测量

是德科技示波器的软件不断创新和优化,增加非常多的人性化功能。对于眼图的测量。只需要通过鼠标或者触控屏控制,一键式点击就可以快速地基于实时波形形成出眼图,为用户提供了非常便捷地方式。本文以Keysight DSO9404A型示波器为例讲解一键快速眼图测量。

为什么香农定理和频率无关?

香农极限(或称香农容量)指的是在信道上进行无差错传输的理论最大传输速率,是香农定理在有限带宽的信道上的理论。

【经验】实时示波器的经典抖动分析(上)

本文Keysight介绍关于抖动测试和分析的设计经验,包括:01. 抖动研究的源起02. 抖动测试和分析的基本方法和经典理论03. 抖动测试的演进和新挑战。

DDR5和DDR4的区别是什么 ?谈谈DDR5测试方法

是德科技可以给大家带来完整的端到端解决方案。包括设计前期的仿真,涵盖了memory designer的建模和ADS的前后仿真。发送端测试中,我们提供业内旗舰级性能指标的UXR实时示波器和高性能的RC模型探头,有效降低测试负载。

绝对干货!PCIE6.0技术剖析

从正式发布至今,PCI Express®(PCIe®)发展迅速,已经成为高性能计算、人工智能/机器学习(ML)加速器、网络适配器和固态存储等应用不可或缺的一项技术。本文中是德科技将介绍PCIe 6.0的几个主要变化和技术能力。

芯科技,解密ChatGPT畅聊之算力输出

现在的算力服务器中,里面并不是一颗颗芯片堆叠在一起,而是一张张算力卡并排插在卡槽里。目前大部分算力服务器单台放置8张或者16张算力卡。是德科技推出PCIe 6.0全链路测试方案。

解密ChatGPT算力芯片技术

ChatGPT的轰动引发全球人工智能大模型训练及应用的浪潮,驱动算力需求进入爆炸式增长阶段。尤其是针对人工智能的智能算力,更成为了算力产业未来发展的重要方向。今天我们将解密ChatGPT背后的算力芯片技术,算力芯片如何工作?HBM内存是什么?GPGPU/CPU/FPGA区别于优劣?一切从芯片开始。

解析DDR测试解决方案

为大家带来数字芯片的重要分支:存储器,DDR5技术及完整的DDR测试方案。

【应用】Keysight提供完整PCI-E 3.0协议信号质量、一致性、可靠性测试方案

PCI-E标准自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于满足高速显卡、高速存储设备对于高速数据传输的要求。

KEYSIGHT自动驾驶与车规芯片测试技术研讨会,共同推动技术创新与发展!

2024年3月15日,KEYSIGHT是德科技与IC PARK共同举办“自动驾驶与车规芯片测试技术”研讨会。本次讲座在中关村集成电路设计园芯学院举行,涵盖毫米波雷达、高级辅助驾驶系统、车载MCU、域控制器高速接口PCIe/DDR,车载以太网以及车载serdes发展趋势与测试挑战等多个热门话题,同时有是德科技示波器、误码仪、网络分析仪、信号分析仪等新品展示与测试技巧交流。

KEYSIGHT示波器选型表

KEYSIGHT示波器选型,高清晰度示波器、混合信号示波器、手持式示波器等,最大存储器深度120kpts-2Gpts。

|

产品型号

|

品类

|

描述

|

宽带(MHz、GHz、GBd)

|

最大存储器深度(kpts、Mpts、Gpts)

|

最大采样率(GSa/s、KHz)

|

操作系统

|

类型

|

|

DSAZ504A

|

示波器

|

Infiniium 示波器:50 GHz

|

50 GHz

|

2 Gpts

|

160 GSa/s

|

Windows 10

|

Real-Time

|

选型表 - KEYSIGHT 立即选型

是德科技新一代C系列光衰减器,提高测试结果的准确性和重复性

光衰减器分为可调光衰减器与固定光衰减器。其主要指标有工作波长、回波损耗、衰减量及精度(衰减范围及分辨率)及工作温度等,常用于评估系统的损耗及各种测试。下面就跟小编一起来了解一下是德科技光衰减器系列产品: N7752C和N776XC系列可变衰减器能够精确控制进入被测件的输入功率,提高测试结果的准确性和重复性。新一代C系列光衰减采用统一的机电和触发设计,能够提高系统搭建的效率,提高设备空间利用率。

【经验】Keysight对实时示波器与采样示波器进行详细剖析—两者概念、区别及应用优势

实时示波器和采样示波器,相似的名字,不同的方法,让Keysight为您理清实时示波器、采样示波器。首先了解这两种仪器的区别,其次分析它们在特定的应用中各有优势,确定哪种仪器更适合使用。

Keysight为400G光模块测试提供高性能采样示波器(光/电眼图仪)及时钟恢复、高速PAM4误码仪、数据流量测试仪

PAM4、FEC技术的广泛采用也使得400G光模块的测试和评估方法与传统的100G光模块有比较大的区别。为了保证其在有限成本和功耗下的性能,需要对其光口、电口的输出质量、接收容限,以及承载真实业务数据下的误码率等表现进行详细的测试,以保证设备间良好的互联互通及可靠数据传输。Keysight为400G光模块测试提供高性能采样示波器(光/电眼图仪)及时钟恢复、高速PAM4误码仪、数据流量测试仪。

解析DDR5技术及DDR测试方案

介绍存储器,DDR5技术及完整的DDR测试方案。

现货市场

服务

提供是德(Keysight),罗德(R&S)测试测量仪器租赁服务,包括网络分析仪、无线通讯综测仪、信号发生器、频谱分析仪、信号分析仪、电源等仪器租赁服务;租赁费用按月计算,租赁价格按仪器配置而定。

提交需求>

朗能泛亚提供是德(Keysight),罗德(R&S)等品牌的测试测量仪器维修服务,包括网络分析仪、无线通讯综测仪、信号发生器、频谱分析仪、信号分析仪、电源等仪器维修,支持一台仪器即可维修。

提交需求>

正在努力加载……

正在努力加载……

登录 | 立即注册

提交评论