【经验】如何为非整数频率配置ClockMatrix时钟器件以获得零转换误差?

IDT(RENESAS收购)ClockMatrix时钟器件设计用于支持非整数频率的精确转换。在10GB以太网LAN/WAN传输中,前向纠错(FEC)应用经常需要用一个基频乘以比率来表示时钟速率(例如,156.25MHz *66/64=161.1328125)。问题是,一些比率例如OTU1 (255/238*2,488.320kHz),会导致非常长的小数,这些小数经常会被截断。本文讨论如何为非整数频率配置ClockMatrix器件,以获得零转换误差。

1. ClockMatrix M/N结构

在ClockMatrix器件的寄存器中表示频率的格式为:

其中M为48位整数,N为16位整数。M/N是可以创建非整数频率的分数。例如:

2.精度要求

由于ClockMatrix器件的结构可以产生精确的频率,这对提供精确的频率配置很重要。例如,接收133.3MHz输出的需求是很常见的。器件和GUI都支持这个比例:

然而,可能系统实际上需要133.333MHz。这意味着133.3MHz实际上是-250ppm偏移的频率。

即使是万亿分之一的错误也足以对1588系统的锁相造成负面影响,或者在视频应用中导致屏幕上偶尔出现一条线。所以,准确的配置是至关重要的。

3. ClockMatrix GUI中的算术表达式

为了支持精确的转换,ClockMatrix GUI里支持输入和输出频率字段的算术表达式。图1显示输入和输出频率字段的位置。

图1 GUI 的输入输出频率字段

这些字段支持加法、减法、除法和乘法。它们还支持分数频率偏移(ffo),例如加1ppm。而且,它们还支持绝对偏移量,比如增加1kHz。下面是有效输入的示例:

· 400/3

· 100+10K

· 156.25+1ppm

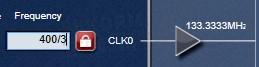

注意: 输入/输出的默认单位是MHz. 这是它在GUI中的样子:

图2 设置PPM偏移的输出频率

4. 输入频率的M/N配置

下面是一个配置输入频率133.333MHz的示例。输入为“400/3”(默认单位是MHz)。

图3 用算术表达式作为输入频率

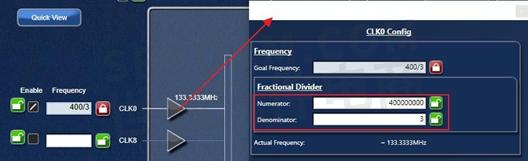

单击CLK0的“buffer”符号会出现“CLK0 Config”对话框,其中显示了M/N设置的详细信息(参见图4)。GUI识别出这个比率,并将M(分子)设置为400,000,000,将N(分母)设置为3。

图4 133.333MHz输入频率设置

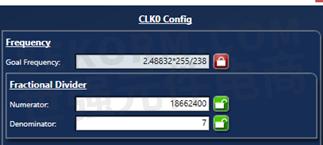

在另一个示例中,像OTU4这样的系统可能需要2.6660571428MHz这样的时钟。在引言中的确切比值是(255/238)*2,488.320,这个分数的小数表示形式是2.6660571428571428571428571428571…(由于64位系统的限制,这个比率被截断了)。

图5 输入频率的复杂算术表达式示例

GUI识别这个比率并将其简化为18662400/7,如图6所示。

图6 CLK0 M/N计算

一些基本的数学计算表明,这与原始的输入比率是完全等价的:

5. 输出频率的M/N配置

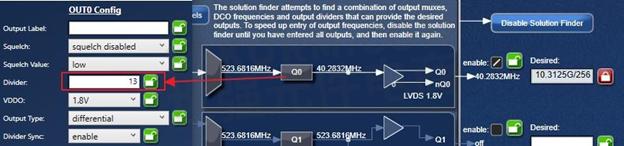

输出频率也支持M/N配置。在本例中,我们用一个普通PHY中使用的频率10.3125GHz/256。在Q0字段中输入频率,然后打开Q0配置窗口,如图7所示。

图7 Q0输出分频器

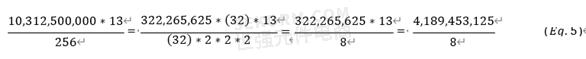

注意,在输出路径中有一个被13整除的设置。这意味着理想的DPLL0频率是(10.3125GHz/256)*13。简化比例计算如下。

接下来,通过按Config按钮打开Channel 0 DPLL配置窗口,如图8所示。

图8 输出频率的算术表达式

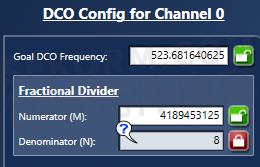

打开DCO配置,显示“目标”和“实际”DCO频率。它们是四舍五入的,只能用于频率的近似。

图9 DCO M/N配置

仔细查看图9中的N值,它不是8,而是65528,即8 * 8191。这是因为GUI总是最大化分母值,以提高设备的相位噪声性能。将方程5的约简分数乘以8191和GUI结果是等价的。

另一种检查结果的方法是设置N值,并允许GUI计算M值(参见图10),得出的减少比例与公式5中计算的相同。

图10 DCO改写分母

比较明智的做法是始终检查M/N比值,以确保这些值是准确的。一种快速、偷懒的检查方法是用一个支持非常精确的分数或小数简化计算的网站。

6. 单步计算建议

在计算翻译时,建议时钟用单个计算步骤,而不是一次计算一个步骤。中间步骤会导致四舍五入错误,这些错误会一直延续到计算的下一个步骤。简单的计算可以避免额外的错误。

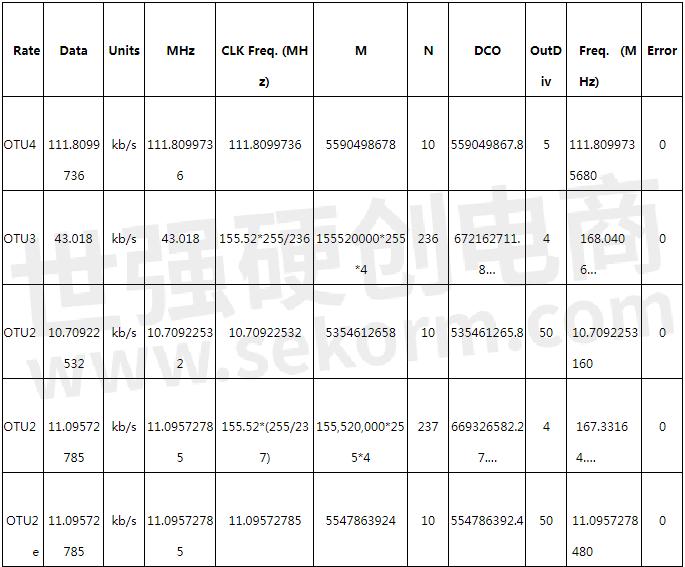

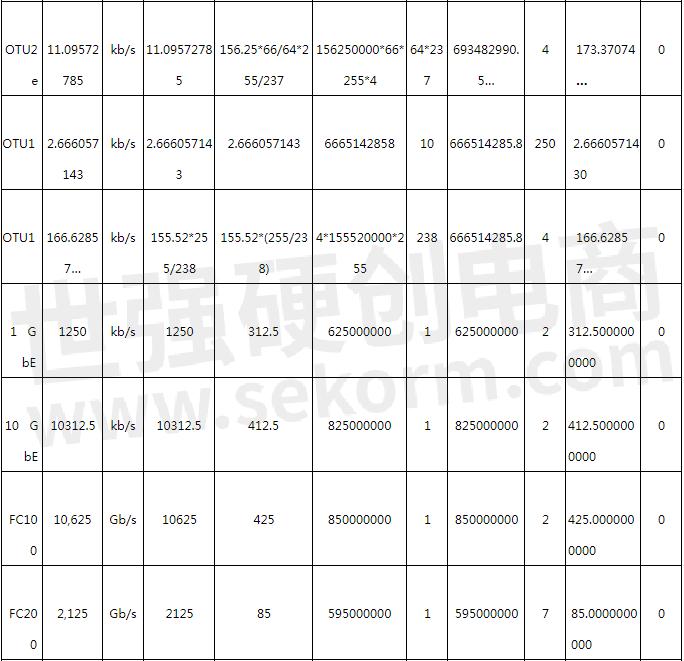

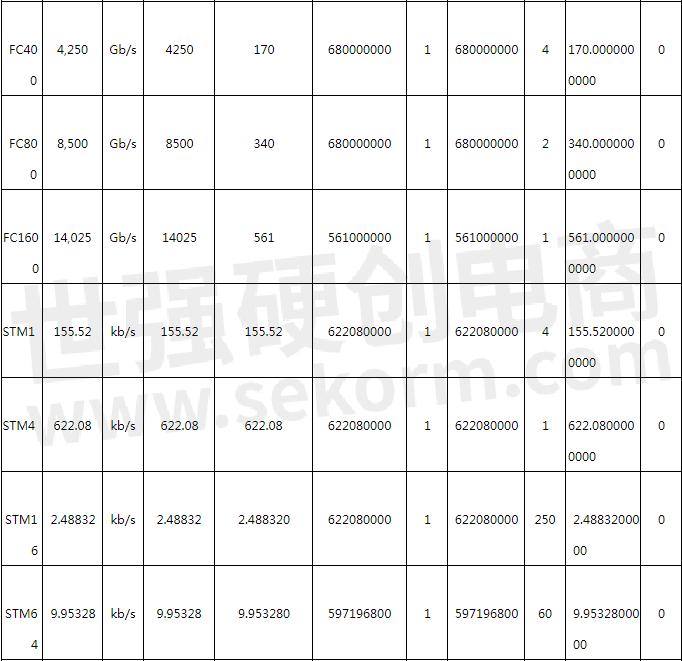

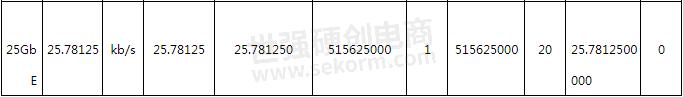

表1显示了标准应用程序的M/N计算的几个示例。

表1 计算示例

- |

- +1 赞 0

- 收藏

- 评论 0

本文由深蓝的鱼翻译自IDT(Renesas收购),版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【经验】Renesas 5P49V6965可编程时钟发生器输入时钟的配置方式

Renesas 5P49v6965是可编程的时钟发生器,抖动低于0.5ps,内置有4组OTP,可支持固化四组频率计划,实现上电既可输出,也支持IIC配置,支持差分频点高达350MHz。可以根据需要选择外部时钟或晶振输入,本文将介绍配置方式。

设计经验 发布时间 : 2022-12-07

【经验】解析Renesas时钟发生器通过软件查看PLL锁定状态的方法

Renesas时钟发生器5P49V6965A000NLGI是可编程时钟发生器,相位抖动低至0.5ps,支持单端输出1kHz~200MHz,差分格式输出频点1kHz~350MHz,广泛应用于基站、数据中心等应用中。本文解析通过软件查看PLL锁定状态的方法。

设计经验 发布时间 : 2022-10-03

【经验】Renesas时钟发生器5P49V6965为实现高稳定时钟输出的设计注意事项

5P49V6965是可编程时钟发生器,内置有4组OTP,可通过固化频率计划,上电即可实现频率输出,也支持IIC每次上电配置,支持外部时钟或晶振输入,本文将介绍时钟发生器5P49V6965在设计时的注意事项,实现高稳定的时钟输出。

设计经验 发布时间 : 2022-10-04

IDT 时钟分配器(缓冲器/多路复用器/时钟分频器)选型指南

目录- Clock Distribution Overview LVCMOS Buffers LVDS Buffers LVPECL Buffers HCSL Fanout Buffers/Universal Output Fanout Buffers LVCMOS Zero Delay Buffers HCSL Zero Delay Buffers LVCMOS Multiplexers LVDS Multiplexers LVPECL Multiplexers HCSL Multiplexers Clock Dividers

型号- 8SLVD1208-33I,8V74S4622,854S058I,854S1208I,8305I,83058I,8T33FS314I,8L30110,9DBU0631,853S057I,8SLVP2102I,9DBU0241,9ZXL0651,8P34S1204I,5V41067A,9DMV0441,87973I-147,870S208,83940DI,558-01,8SLVP1104I,9ZX21201,853S058I,9ZX21200,853S006I,8T79S818I-08,9DBU0741,86004I,9ZXL1231,8L30210,8P34S1106I,87972I-147,74FCT38072S,8530I-01,553S,9DBV0941,831721I,8SLVD2102I,9DBV0541,8S89876I,674-01,527-01,5PB1110,670-03,8SLVD1208I,8SLVP1204I,83056I,853S011BI,853S310I,DB1200Z,850S1601I,DB1200ZL,8L30205,831724I,651S,86004,9ZXL0831,8SLVD1208-33,8SLVP2108I,831752I,8S89831I,8714004I,9ZML1232,8V79S674,DB800ZL,5PB11XX,87002-02,9DMU0441,87002-05,8T39S10I,854S057BI,5PB1108,8SLVD1212,5PB1106,853S011CI,5PB1104,74FCT3807S,8T39S11,5PB1102,9DBU0641,853S012I,9ZXL1530,542,859S0424I,859S0412I,9ZXL1251,8T349316,9DBV0841,9DBV0441,854S01I,9ZXL1930,2308B,83054I,9DBV0241,8L3010,854S054I,8705I,9DBU0431,853S54I,5P1105,853S013I,9DBU0441,8P34S1212I,9ZX21901,8SLVP2106I,9ZX21501,87001I-01,8T33FS6222,87004I,8P34S1208I,8T33FS6221,831742I,87016I,9DMU0141,853S014I,8308I,9DBU0941,8343-01,9DBU0541,9ZXL1550,5P1103,8P34S1102I,859S0212I,8T33FS6111,83918I,670-01,9ZXL1950,9DBV0741,8SLVD1204I,85356I,8SLVP1212I,853S12I,8SLVP1208I,850S1201I,8T73S208I,8SLVD1204-33I,570,571,9DMV0141,574,74FCT38075S,8SLVD1204-33,8SLVP2104I,8714008I,8S89875I,8T74S208I,DB1900Z,8SLVP1102I,8S89874I,524S,8T53S111I,621S,853S01I,8P73S674I,8SLVD2104,9DBU0841,74FCT38074S,5V41068A,551S,853S111BI,9DBV0641,8S89834I

RC32112A FemtoClock Network Synchronizer, Jitter Attenuator and Clock Generator

型号- RC32112ADDDGN2#KB0,RC32112A,RC32112ADDDGN2#BB0

【应用】瑞萨多款时钟缓冲器和多路复用器用于PCIe Gen6时钟解决方案,满足开发高性能系统需求

瑞萨Renesas率先推出符合PCIe Gen6严格标准的时钟缓冲器和多路复用器。这些新器件,应用在PCIe Gen5时抖动余量更大,为客户提供完整的PCIe Gen6时钟解决方案,用于数据中心/云计算、网络和高速工业等应用。

应用方案 发布时间 : 2022-04-25

【产品】支持1GHz时钟输入的高性能差分时钟分频器和扇出缓冲器8T73S208、8T73S208B-01

8T73S208和8T73S208B-01是IDT(Renesas收购)推出的两款高性能差分LVPECL时钟分频器和扇出缓冲器,两款器件设计用于高频、低相位噪声时钟的分频和信号输出。其主要用于网络存储、多功能打印机,无线接入,路由器等领域。

新产品 发布时间 : 2019-04-02

【产品】瑞萨新推ClockMatrix系统同步器8A34001,可在O-RU参考设计中实现S-plane功能

全球半导体解决方案供应商瑞萨电子推出支持IEEE 1588的ClockMatrix™系统同步器——8A34001,其将应用于针对5G NR应用的AMD Zynq® UltraScale+™ RFSoC DFE ZCU670评估套件及参考设计。

新产品 发布时间 : 2022-10-14

MC100ES6226 2.5v/3.3v Differential LVPECL 1:9 Clock Distribution Buffer and Clock Driver

型号- MC100ES6226AC,MC100ES6226ACR2,MC100ES6226,MC100ES6226FAR2,MC100ES6226FA

【产品】两对差分参考时钟输入对的时钟扇出缓冲器8T39S11A,晶振输入可接受10MHz至40MHz晶振或单端时钟

8T39S11A是IDT(Renesas收购)推出的一款高性能时钟扇出缓冲器,可用于高频低相位噪声时钟和数据信号的信号扇出。其输入时钟可从两个差分输入或一个晶振输入中选择。如果未选择晶振输入,则缓冲器内部振荡器电路将自动禁用。晶振引脚可以由单端时钟驱动。所选信号分配到十个差分输出,这些输出可以配置为LVPECL、LVDS、HSCL输出和LVCMOS输出。所有输出均可被禁用为高阻抗状态。

新产品 发布时间 : 2019-10-22

6V49205A FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

型号- 6V49205A,6V49205APAG8,6V49205APAGI,6V49205APAGI8,6V49205APAG,6V49205B

在Renesas 78K4的指令手册中SUBWAX,#Word这条指令的时钟周期是3个时钟,但真正执行该计算时却需5个时钟周期。为什么?

你所说的3个时钟周期是在假设一条指令已经被加入到预取指令队列中的情况下所估计出的值。 你所说的案例可以参照执行分支指令之后而使指令队列为空时的执行情况。 SUBW指令执行时钟周期并非3个时钟是因为除了这3个时钟之外还要加上取指令时间。 另外,执行时钟周期的不一致还取决于该地址是奇地址还是偶地址。

技术问答 发布时间 : 2019-07-30

【产品】采用IDT第五代可编程时钟技术的可编程时钟发生器,频率均由单个参考时钟或晶体产生

IDT(瑞萨收购)推出的5P49V5907和5P49V5908可编程时钟发生器,采用IDT第五代可编程时钟技术(VersaClock®5),配置可以存储在片上一次性可编程(OTP)存储器中,也可以使用I2C接口进行更改。频率均由单个参考时钟或晶体产生。两个选择引脚允许编程最多4种不同的配置,并可使用处理器GPIO或通过自举进行访问。 具有高性能,低相位噪声等优势,适用于高性能消费类、网络、工业等。

新产品 发布时间 : 2019-04-11

电子商城

现货市场

登录 | 立即注册

提交评论