【经验】解析智多晶合封系列FPGA中DDR2的应用

智多晶Sealion2000的合封系列FPGA,提供一款25K逻辑,QFN96封装(10mm x 10mm)的高性价比FPGA,其器件资源信息如下表所示:

DDR2型号为ESMT M14D5121632A,容量为8M*16bit*4 Bank,Vdd=1.8V±0.1V,Vddq=1.8V±0.1V,接口属性SSTL_18,Column Address:A0~A9,ROW Address:A0~A12,具体更多的参数,可以网上查阅对应的规格书。

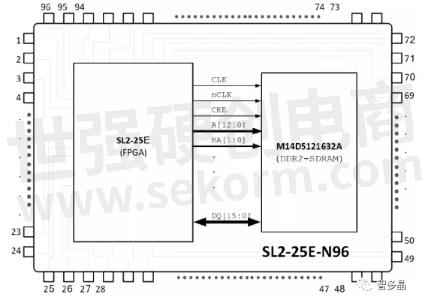

FPGA与DDR2的内部连接如图1所示:

图1 芯片内部连接

由于颗粒集成在FPGA内部,对比于传统的FPGA+外挂DDR2颗粒,有明显节约PCB尺寸的优点,减轻板卡布线压力。

对于前期硬件设计而言,硬件工程师需要注意:

1)BANK 1、2、5、6必须接1.8V,其余BANK则可以接1.2~3.3V

2)外挂Flash芯片需用1.8V的

DDR2的应用例子

合封系列FPGA可以应用在需要大量缓存数据的场合,比如工业数据采集卡、视频处理应用以及无线通信中的数据采集板,如果各位读者朋友们有需要用到FPGA+DDR2架构的,可以联系智多晶,智多晶会提供完整的DDR2 Control IP,甚至亲手为用户写好应用层部分的程序,并为用户调试好。

下面将举一个例子来阐述DDR2-SDRAM的应用:三角波数据的缓存与读取

例子中由几大部分构成:

1)DDR2控制器程序

2)用户CMD控制部分

3)FIFO数据&时钟域处理

图2 程序框图

这个例子可以让用户更深刻了解控制器的使用方法,且如何规划颗粒内部的存储单元,体现出来的就是控制器程序端口中23bit的行列地址,以及2bit的Bank地址。

1)用户CMD控制部分

这部分简单来讲,就是用户自己规划何时去读写DDR2,读写的长度可以自由规划,只需注意发出正确的CMD指令,其中CMD=010表示往DDR2写数据,CMD=100表示从DDR2读数据,且BL=8,控制器程序的用户接口端,数据是32bit,而物理芯片接口端是16bit,因此控制器是在DDR时钟的上升沿和下降沿完成一次32bit数据的存储,每完成4个32bit数据写入,地址需要递增8(BL=8)。这部分程序需要用户自己根据项目特点来写,智多晶也可以根据用户的需求,给用户写这部分功能,并参与调试。

2)FIFO部分

CMD FIFO:用于缓存CMD指令,包括读写指示及读写起始地址,DDR2控制器检测到CMD FIFO非空,就会读出指令,来执行写/读操作;

Write FIFO:用户写入数据, DDR2控制器过来获取,达到转换时钟域,并写入颗粒内部的功能

Read FIFO:DDR2控制器读出数据,存到Read FIFO里,用户再读取,同样是转换时钟域

3)DDR2控制器

这部分智多晶将以黑盒子IP的形式提供,用户也不需要关注内部的细节,只要调用就行。

3. DDR2的读写验证

把三角波,以4000个16bit为一组,写入DDR2内部,总的写入4000组,每个Bank存1000组,存储规划为:

Bank 0 :4000*1000,占用地址为0x0~0x3D0900

Bank 1 :4000*1000,占用地址为0x0~0x3D0900

Bank 2 :4000*1000,占用地址为0x0~0x3D0900

Bank 3 :4000*1000,占用地址为0x0~0x3D0900

CMD控制部分就是用于控制行列地址与Bank地址,注意需要把16b数据,每2个叠成1个32b,再写入FIFO;同理,DDR2内部读出来的数据,需要把32b转16b拆分开。

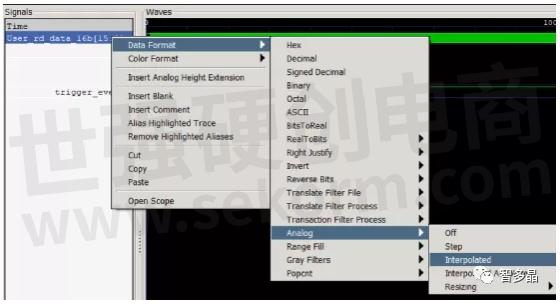

在Hq编译工具里,进行板级Debug,抓取其中一部分的波形:

注:这里可以把数据设置成Analog的属性,这样便于观察数据是否有误。

操作步骤:

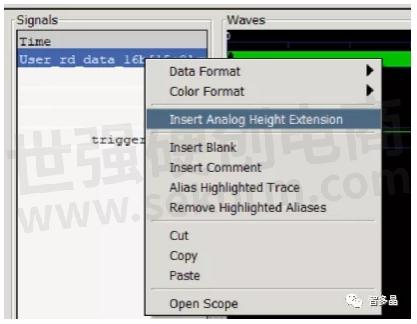

如果波形显示不够大,可以调节窗口:

- |

- +1 赞 0

- 收藏

- 评论 1

本文由犀牛先生转载自西安智多晶,原文标题为:浅谈智多晶合封系列中DDR2的应用,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【经验】如何在FPGA上实现低成本开根号运算?

开根号运算是科学计算和工程应用中基本而重要的运算之一,在QuartusII和ISE开发软件中,都集成了开根号的ip核,这些底层源码对于用户来说是不可见的,那么如何在西安智多晶的FPGA中实现开根号运算,是本文要探讨的课题。

【经验】西安智多晶5000系列FPGA内嵌MCU调试测试指南

西安智多晶推出的Seal 5000 FPGA SA5Z-30系列内部合封Cortex M3硬核,最高主频可达200Mhz,32KB数据RAM和128KB指令RAM。本文针对FPGA内嵌M3硬核的使用做简洁的开发过程。

【经验】智多晶FPGA上实现LTE削峰算法PC-CFR

CFR算法是一种直接在数字域上面处理的方法,对于超出设定门限值的信号,直接在数字域上进行处理和消除。目前CFR算法有PW-CFR、NS-CFR和PC-CFR,常用的还是PC-CFR,其削峰能力最佳,本文就针对PC-CFR算法,在智多晶AD9365射频开发板上进行测试和实现。

【选型】西安智多晶(XIST)FPGA/CPLD可编程逻辑器件选型指南

目录- Seagull1000/Sealion2000/Sealion合封系列

型号- SL2D-25E,SEALION2000,SL2E-5E,SEAGULL1064C,SEAGULL1000,SG1128V,SEAGULL1256C,SEAGULL1064V,SG1064V,SEAL 5000,SG1256V,SEAGULL1256V,SL2-12E,SL2S-25E,SEAGULL 1000,SG1128C,SG1064C,SL2-25E,SL2S-12E,SL2-7E,SL2-5E,SEAGULL1128C,SL2E-7V,SEALION 2000,SG1256C,SEAGULL1128V

【选型】国产FPGA SL2-25E-8U324替代XC6SLX16 CSG324用于工业伺服控制器,有效应对交期问题

客户在工业伺服控制器中用到一款Xilinx FPGA,但因为交期问题需要国产化替代,使用型号是XC6SLX25-CSG324,主要用于做逻辑控制和与MCU交互数据、进行数据处理,给客户推荐了西安智多晶SL2-25E-8U324,可以兼容替代。

SA5Z-30 FPGA 器件概述

型号- SA5Z-30-D3-U256,SA5Z-30,SA5Z-30-D0-U324,SA5Z-30-D1-U213,SA5Z-30-D0-U324C,SA5Z-30-D2-U256,SA5Z-30 系列,SA5Z-30-D2,SA5Z-30-D3,SA5Z-30-D0,SA5Z-30-D1

【应用】国产海狮系列FPGA SL2E-5E用于扩展外设接口,集成flash,工作频率高达300MHz

西安智多晶的SL2E-5E是一款集成了5K逻辑单元的小规模FPGA,但是比CPLD容量更大,能实现更多的逻辑设计,同时该FPGA内部集成了Flash,不需要再外接配置用的Flash,简化了电路设计。

西安智多晶发布软件无线电评估板,基于28nm FPGA芯片SA5Z-30并搭载ECR8661 RF收发器助力研发

为了让无线通信客户更方便评估智多晶FPGA芯片以及国产RF Transceiver,西安智多晶联合智锐星科技为客户打造了一个专业的软件无线电(SDR)评估板,可用于客户前期的项目预研。评估板的核心器件是28nm FPGA芯片SA5Z-30。

【产品】基于智多晶SL2-25E FPGA芯片的软件无线电(SDR)评估板,适用于项目开发初期验证、教学及培训

为了更好让无线通信客户评估智多晶FPGA芯片,西安智多晶为客户打造了一个专业的软件无线电(SDR)评估板,可用于客户前期的项目预研,其核心器件是西安智多晶的SL2-25E FPGA芯片,F256封装。这个评估板卡非常适合小带宽、低成本的通信项目,专网或公网的应用。

Seal(海豹)SA5Z-30 FPGA 产品手册

型号- 海豹5000系列,SA5Z-30-D2,SA5Z-30-ES,SA5Z-30-D0-UBGA324,SA5Z-30-D0,SA5Z-30-D1,SA5Z-30-D1-UBGA213,SA5Z-30-D2-8U213C5,SA5Z-30,SA5Z-30-D1-8U213C4,SA5Z-30-D2-8U213C6,SA5Z-30-D2-UBGA213,SEAL 5000系列,SA5Z-100-D1-8U324C,SA5Z-30-D0-8U324C6,SA5Z-30 系列,SA5Z-30-D1-8U213C,SA5Z-30-D2-8U213C

SA5Z-50 FPGA 器件概述

型号- SA5Z-50-D0-7F484,SA5Z-50,SA5Z-50-D0-U324,SA5Z-50-D0-F484,SA5Z-50-D0-7U196,SA5Z-50-D0-U196,SA5Z-50-D0-8U324C,SA5Z-50-D0,SA5Z-50 系列,SA5Z-50-D1

电子商城

现货市场

登录 | 立即注册

提交评论