【技术】DSPLL为何能轻松KO级联,两级PLL?

【摘要】RAN 设计具有空间受限特点,与其他联网设备相比价格低廉,并且可以部署在非温度控制的位置。它们必须针对尺寸、功耗、性能和成本进行优化。而经验证的DSPLL定时技术,可减少66%的现有定时BOM占用空间、降低30%的功耗、增强设计灵活性及降低系统成本。

RAN节点针对尺寸,功耗和性能进行优化

下图为目前网络基础设施中应用RAN节点的架构图:

RAN定时要求多样化而苛刻

尽管RAN 设备在外部元件中必须具有小体积和经济可靠的特点,但由于无线相位噪声要求,RF定时规范仍然十分严格。RAN设备需要更多混合频率以支持系统级功能。

RAN系统要求增加了定时复杂性

上述的一系列要求增加了复杂性、功耗和占用空间,因为传统的定时解决方案不够灵活,更耗能且需要不同的离散元件。RF定时规范仍然十分严格。需要更多的混合频率以支持系统级功能,同时不影响性能。

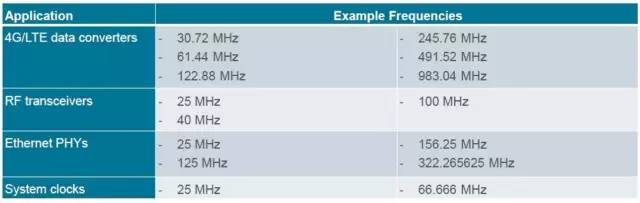

RAN 设备所使用点常见定时参考频率:

DSP与当前定时结构的对比简介

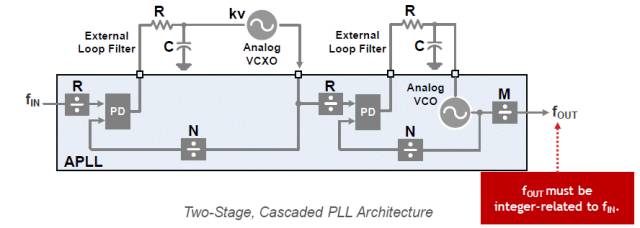

传统的RAN设计采用了级联的两级锁相环(PLL)技术以应用于高性能、低相位噪声时钟合成。级联、两级锁相环PLL 提供了卓越的相位噪声性能,但具有有限的频率灵活性、高功耗,对噪声和振动的敏感性,以及较大的离散占用空间(包括外部VCXO 和环路滤波器)等缺点。

级联、两级PLL 是RAN 设计中的传统模拟架构。它实现了较低的相位噪声但仅限于一组有限的输出频率,输出频率必须与其输入频率整数相关。

该架构使用了基于离散、模拟、窄带的基于VCXO的PLL,以在其第一级实现抖动清除。VCXO必须作为PLL的VCO与外部环路滤波器结合使用以实现低相位噪声。第2级PLL依靠模拟宽带PLL提供整数时钟倍频。这就需要额外的外部环路滤波器。

然而,RAN设计需要更小体积、更灵活和更优化的定时解决方案,对此,新型的DSPLL定时技术可以迎合了RAN的定时需求。

DSPLL解决上述挑战,通过提供单一IC,对比现有解决方案可实现低相位噪声,更大的频率灵活性,更低的功率,以及更好的抗噪声和抗振效果。这项新技术令人惊艳!

DSPLL已经广泛部署于电信应用中

实际上DSPLL 已经广泛运用和部署于核心、地铁和接入设备中的苛刻的电信和网络应用中,其中包括先进的100G/400G SerDes 时钟应用。

• 超过50 百万的支持DSPLL 的节点已经部署于高性能、苛刻的电信和网络应用中。

• 数以百万计的可靠运行时间。

DSPLL架构综述

• DSPLL 架构集成并改进了传统解决方案。

• DSPLL 技术提供了系统时钟,例如以太网和基带。

• 满足苛刻的4G/LTE 相位噪声要求且具有裕度的RF 超低相位噪声时钟。

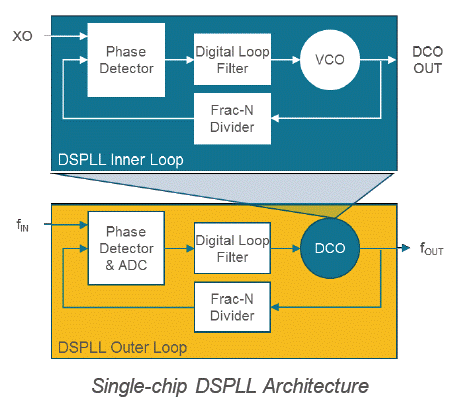

DSPLL架构说明

内环用作外环的数字控制振荡器,提供具有低相位噪声的分数时钟合成,无需LC振荡器和离散VCO。

外环数字调谐内环的工作频率,与外部参考时钟同步,衰减抖动并生成时钟。DSPLL的所有元件都集成在芯片上,无需使用离散滤波器组件,并可实现简单的PLL带宽调整,优化相位噪声性能。

简化设备编程

传统的级联PLL 计算和设置是手动完成,这一过程很繁琐且容易出错。SILICON LABS ClockBuilder Pro是简单而易于使用的软件工具,可在数分钟内定制DSPLL。

• 键入输入和输出频率

• 设置DSPLL 带宽和其它工作参数

• 并生成设备配置

如此可实现简单、高效的测试,并加快产品上市。

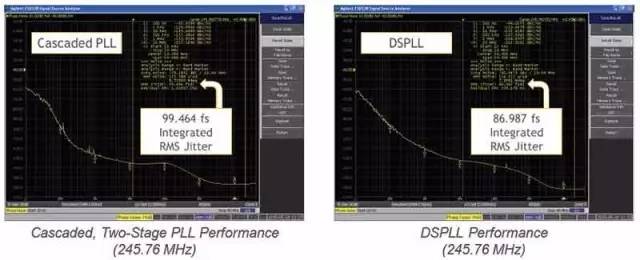

性能:DSPLL对比级联,两级PLL

DSPLL 技术性能达到或超越了传统解决方案的性能。

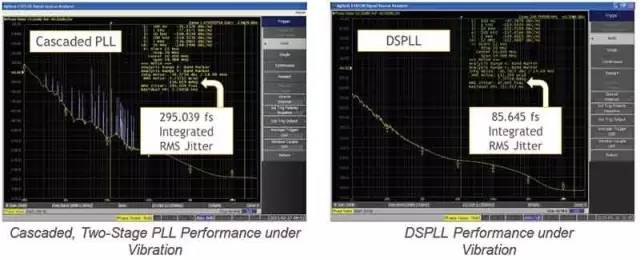

DSPLL抗振性能

RAN设备通常部署在外部环境中,其中风、建筑物或机械设备都可能引起振动。DSPLL对这些影响具有良好的抗干扰性能:

DSPLL的体积比级联、两极PLL小66%

下表显示了元件尺寸并未考虑 PCB 间距或布线规则,进一步提升了 DSPLL 的尺寸优势。DSPLL 简化了设计,因为它在片上集成了灵敏的大型元件,包括 VCXO 和电源滤波元件。

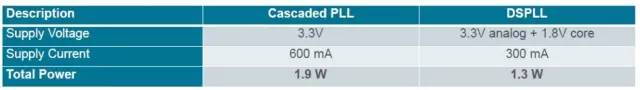

DSPLL 的功耗比级联、两极 PLL 小 30%

通过减少小型机箱中的电流消耗和热量来改善RAN 设备设计,如下表的DSPLL功耗对比级联、两极PLL所示:

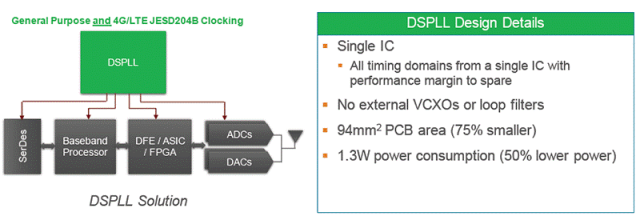

具有DSPLL的设计

RRH、小基站和MDAS设计需要低相位噪声 RF 时钟加上基带和以太网的组合。这些时钟域非整数相关。这对DSPLL而言不是问题。

DSPLL尺寸更小、功耗更低、性能更优、上市更快

Silicon Labs业经验证的DSPLL技术可显著节省空间,降低功耗和成本,并且更易于设计并加快上市。DSPLL的性能优于传统解决方案。

- |

- +1 赞 0

- 收藏

- 评论 3

本网站所有内容禁止转载,否则追究法律责任!

评论

全部评论(3)

-

![]()

![]() 世强代理 Lv7. 资深专家 2018-07-06支持支持

世强代理 Lv7. 资深专家 2018-07-06支持支持 -

![]()

![]() 小蛮大人 Lv9. 科学家 2018-06-29学习了

小蛮大人 Lv9. 科学家 2018-06-29学习了 -

![]()

![]() 我的名字 Lv7. 资深专家 2018-01-06学习学习

我的名字 Lv7. 资深专家 2018-01-06学习学习

相关推荐

一款适合IEEE 1588V2的专用时钟芯片

Silicon Labs日前推出了专门实现IEEE 1588协议的超低抖动时钟芯片SI5348,这款芯片可以满足IEEE 1588 V2组网对系统时钟极其苛刻的指标要求,完美实现IEEE 1588 V2协议。

时钟树设计原则你还不造 来get一下吧

在进行时钟树设计时,“一成不变”的策略并不适用,优化时钟树以满足性能和成本的要求取决于多种因素,包括系统架构、集成电路(IC)时序需求(频率、信号格式等)和终端应用的抖动需求。

【技术大神】Femto TD-LTE基站产品时钟设计注意要点

本文讲的是基于Si5338芯片的Femto TD-LTE基站产品的时钟设计项目,该芯片是一款支持iic管理的4路时钟生成器芯片,该芯片可以输出0.16MHz至350MHz任意频率时钟信号。

【技术大神】论时钟电路设计中时钟芯片的重要性

在时钟选型和设计中除了要特别注意时钟的参数、性能、可靠性,同时还需要注意时钟的原理设计、EMI设计以及PCB走线,只有这样才能设计出一款好的产品。

【产品】高精度“迷你”晶体,轻松实现通信设备的小型化

EPSON的FC1610AN具有高精度的输出频率,可用于网络时钟同步、计时系统等。

【经验】可编程晶体振荡器增加寄存器校验的重要性

本文介绍了Si514可编程晶体振荡器配合某DSP使用时,出现远远超过默认频率的输出的解决方法。

Si50x CMEMS振荡器架构剖析,超越传统振荡器性能

本文档主要介绍CMEMS工艺技术、目前的混合振荡器架构和Si501/2/3/4(Si50x)CMEMS振荡器架构。

【产品】抖动仅0.25ps的可编程晶振,分辨率优于1ppb

Si57x采用第三代DSPLL技术,可输出10MHz~1.4GHz间的任意频率,且稳定性是SAW晶振的三倍。

想提高网络数据中心的速率?非要频率灵活时钟发生器不可!

Si5341/4元件能产生任何频率,在整数模式中不到100 fs RMS,在小数合成模式中不到150 fs RMS,将成为未来高速网路和数据中心不可或缺的关键设计元素。

【产品】支持任意频率、任意输出的时钟发生器

基于Silicon Labs突破性的MultiSynth技术,Si5338能合成从0.16 至 350 MHz间的任何频率,并能在每个装置的四个不同输出选择高达700 MHz的频率。

【产品】业内首款抖动<100fs的分数合成与抖动衰减时钟

业内首款抖动<100fs的分数合成与抖动衰减时钟---Si534x片上时钟树,具备超高频率灵活性,可为时钟合成与抖动衰减需求提供当前最佳解决方案。

【产品】抖动时间小于50ps的CY28800低抖动差分缓冲器,为PCI Express和SATA通信保驾护航

Silicon Labs(芯科实验室有限公司)发布了一款低抖动差分缓冲器——CY28800,该器件CTC抖动时间小于50ps,可以作为CK409和CK410的配套器件使用。CY28800具有8组0.7V的差分时钟输出,采用OE_INV输入实现OE,PWRDWN以及 SRC_STP活动电平的翻转,同时该产品具有可编程的带宽,扩展了产品的使用范围。

超小!一颗让你实现小基站无线应用的时钟发生器

在这个准备迈入5G技术的时代,具有“小”这一特点的小基站成为通讯产品开发的热点,但同时小基站对于系统体积、射频收发性能、功耗的要求都非常严格,也为设计带来了诸多挑战。本文介绍一款时钟发生器让你更好地实现小基站无线应用。

爱普生TSX-3225(X1E0000210173xx)兆赫范围晶体单元

晶体及时钟芯片,X1E0000210173xx,TSX-3225

EPSON - 兆赫范围晶体单元,晶体及时钟芯片,MHZ RANGE CRYSTAL UNIT,X1E000021026400,X1E000021029511,X1E000021048711,X1E000021012911,X1E000021015900,X1E000021100700,X1E000021012511,X1E000021001900,X1E000021059600,X1E000021012900,X1E000021048700,X1E000021011811,X1E000021069700,TSX-3225 40.000000 MHZ 10.0 +10.0-10.0,X1E000021016700,TSX-3225,X1E000021016300,X1E000021064811,X1E000021043411,X1E000021012500,X1E000021071100,X1E000021050211,X1E000021008711,X1E000021024600,X1E000021013900,X1E000021011600,X1E000021015400,X1E000021042711,X1E000021012011,X1E000021017700,X1E000021043800,X1E000021062400,X1E000021043400,X1E000021012411,X1E000021037511,X1E000021014711,X1E000021013500,X1E000021011200,X1E0000210173XX,X1E000021037512,X1E000021035211,X1E000021092211,X1E000021050200,X1E000021024611,X1E000021002200,X1E000021049611,X1E000021015911,X1E000021069600,X1E000021012000,X1E000021063500,X1E000021041211,X1E000021062411,X1E000021014700,X1E000021012400,X1E000021015511,X1E000021001911,X1E000021037000,X1E000021028500,X1E000021025511,X1E0000210487,X1E000021057900,X1E000021025512,X1E000021068000,X1E000021013800,X1E000021011900,X1E000021069611,X1E000021048111,X1E000021063511,X1E000021016911,X1E000021089900,X1E000021088000,X1E000021079411,X1E000021031400,X1E000021075900,X1E000021013911,X1E000021083400,X1E000021015814,X1E000021068011,X1E000021048100,X1E000021015411,X1E000021017317,X1E000021016900,X1E000021036411,X1E000021037500,X1E000021059511,X1E000021035200,X1E000021083411,X1E000021083414,X1E000021012611,X1E000021016411,X1E000021016811,X1E000021012211,X1E000021013300,X1E000021058411,X1E000021059500,X1E0000210502,X1E000021076200,X1E000021025500,X1E000021101000,X1E000021014900,X1E000021013811,X1E000021060200,X1E000021041011,X1E000021011911,X1E000021016400,X1E000021016800,X1E000021013011,X1E000021013014,X1E000021012200,X1E000021059611,X1E000021059612,X1E000021076211,工业电子,消费电子,汽车电子,通信设备

抖动性能可达到150fs以下的高效时钟解决方案

Silicon labs 推出一款高性能防抖时钟芯片Si5346/Si5347,Si5347则集成了4个独立抖动衰减PLL,Si5346是更小封装的双DSPLL版本。可应用于抖动性能要求苛刻光传输网络、无线基础设施、宽带接入/汇聚、数据中心设备。

电子商城

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥8.1764

现货: 85,574

品牌:SILICON LABS

品类:Mighty Gecko Multi-Protocol Wireless SoC

价格:¥27.0929

现货: 57,517

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥17.6531

现货: 47,856

现货市场

品牌:SILICON LABS

品类:Switch Hall Effect Magnetic Position Sensor

价格:¥2.2924

现货:126,000

服务

测试范围:扬兴晶振全系列晶体,通过对晶体回路匹配分析,调整频率、驱动功率和起振能力,解决频偏、不起振、干扰、频率错误等问题。技术专家免费分析,测完如有问题,会进一步晶振烧录/修改电路。

实验室地址:深圳 提交需求>

提供CE测试服务,通过晶体回路匹配分析,给出测试报告。支持EPSON所有MHz无源晶体、32.768KHz晶体。支持到场/视频直播测试,资深专家全程指导。

实验室地址:深圳/上海 提交需求>

登录 | 立即注册

提交评论