【应用】SIDesigner实现并行接口信号完整性分析案例

并行接口如DDR、EMMC等在消费类电子以及高端服务器产品中应用越来越广泛,数据速率越来越高。由于并行接口同步切换时各信号之间相互干扰较强,且电流较大,抖动以及电源噪声会造成较大的系统时序损失,而一旦设计完成再发现问题重新设计会造成较大的成本损失。因此在设计前以及设计中对并行接口进行信号完整性、电源完整性分析以确保设计速率满足规格要求是信号完整性工程师的一个主要任务。

进行信号完整性分析一般分为EM仿真器物理建模和用SPICE工具进行系统时序电路分析两个步骤,而在pre-layout阶段,由于缺少具体的layout物理设计,通常选用相近似的PCB或者package设计模型并根据实际情况用传输线模型以及过孔模型来进行评估,从而在设计初期对系统结果有一定预期。巨霖科技SIDesigner作为信号完整性与电源完整性电路级仿真平台,可以在PCB、Package物理模型已有的情况下进行系统级信号完整性、电源完整性分析,或者pre-layout阶段的系统时序性能评估。本案例介绍基于SIDesigner仿真平台的pre-layout阶段并行接口信号完整性分析,案例涉及IBIS模型、S参数模型以及传输线模型等。

仿真准备工作

在仿真评估开始前,必须对要仿真对象全貌以及要评估的内容进行充分的准备,所谓garbage-in garbage-out。

本案例以LPDDR3为例,对其中的一个byte进行信号完整性评估,准备工作如下:

1)DDR接口速率:简单起见以1Gbps为例。

2)DDR TX/RX IO模型:以下为例,TX为controller,需控制芯片IP提供商提供IO模型,RX为DRAM,需要DRAM厂商提供对应的IO模型。

3)Channel模型:封装模型由DRAM、controller厂商提供,PCB由于还未设计,以接近设计的传输线模型代替。

4)电源模型:在pre-layout阶段评估,以理想电源代替,暂不考虑电源噪声的影响。

以上准备工作就绪后,即可开始在SIDesigner中进行系统级信号完整性仿真工作。

SIDesigner进行并行接口信号完整性仿真具体步骤。

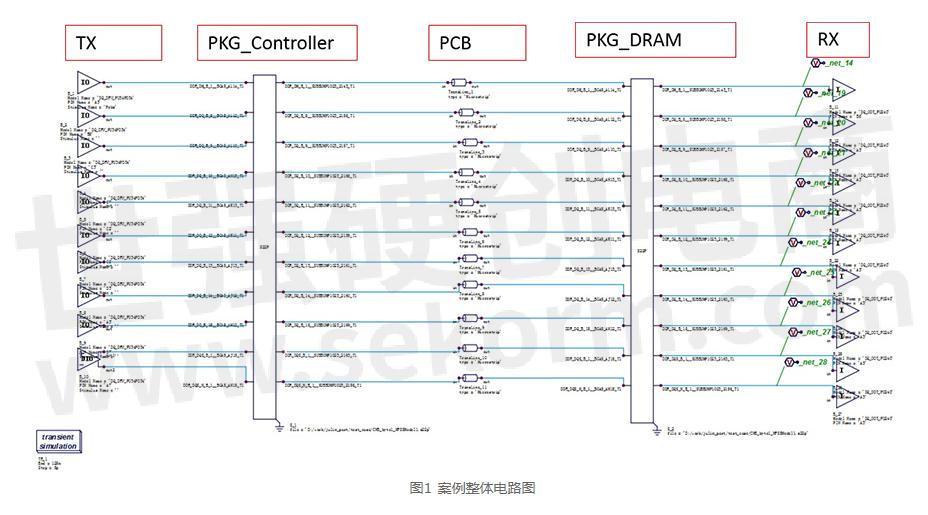

本案例的最终电路结构图示如下,下面将分步介绍案例在SIDesigner中的创建过程。

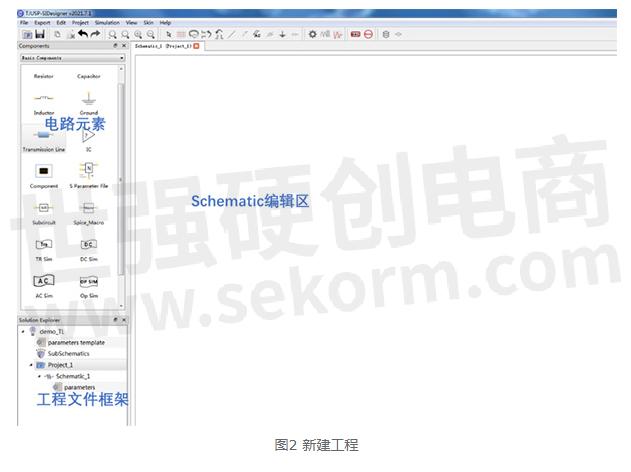

步骤一:工程创建

Step 1:

SIDesinger中需要先创建Solution,然后创建Project,并进行命名。 在Project下面,可以创建具体的电路schematic。

通常在创建完成后,首先设置仿真所用的S参数模型及IO IBIS模型所在的路径,以便后续设置时快速获取。

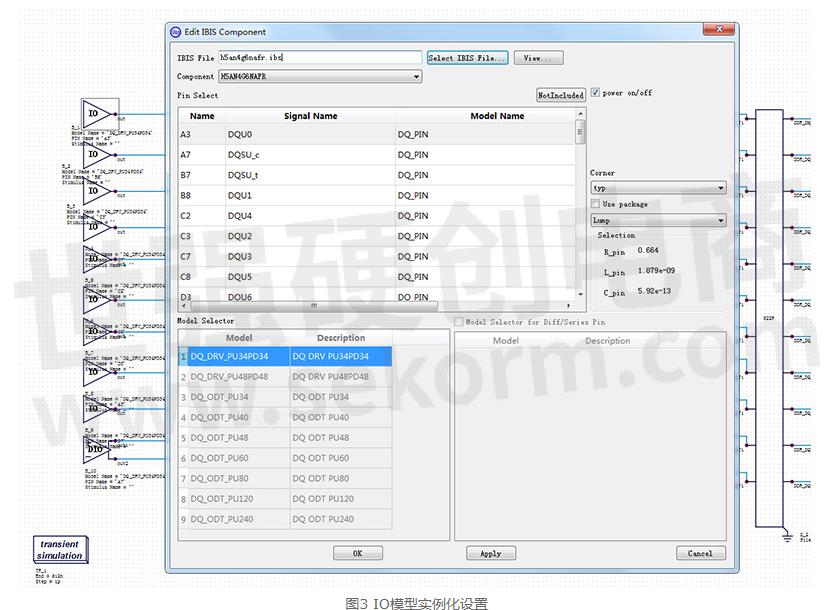

Step 2:IO模型实例化

放置IO buffer模型并进行模型实例化:导入IBIS文件,选择相应的component,然后选择pin及对应的IO model,逐一完成IO实例化。注意需要对发送端和接收端设置响应的Output和Input模型。图示为Output模型,驱动选择34ohm。

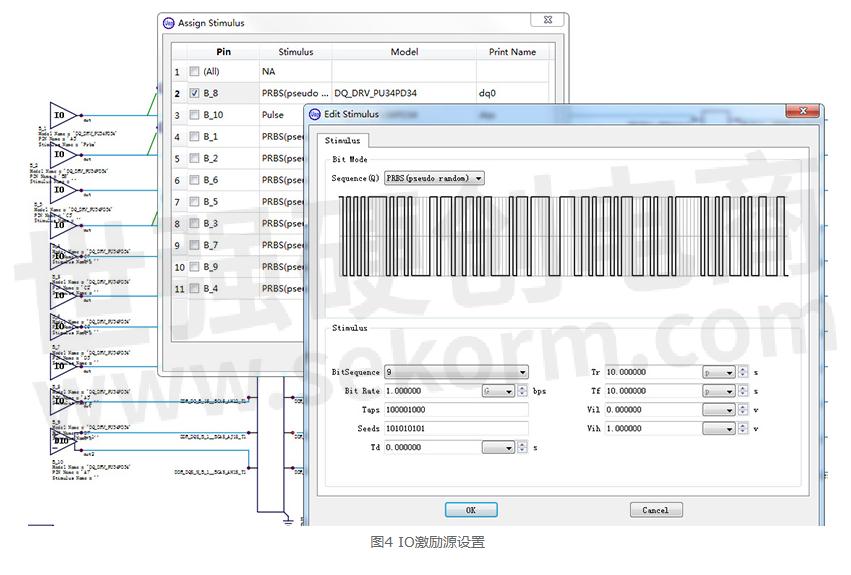

Step 3:信号激励设置

IO模型实例化结束后,即可对发送端的IO设置激励波形。SIDesigner支持各种类型的激励设置,包括PRBS、PWL、Pulse、PAT以及各种基于文件输入的形式。在DDR接口仿真中,通常DQ信号用PRBS激励,而DQS信号用PULSE激励。

需要注意的是对于DDR接口来说,DQ、DQS之间根据SPEC的需求有响应的延时,在设置仿真激励时必须予以考虑。

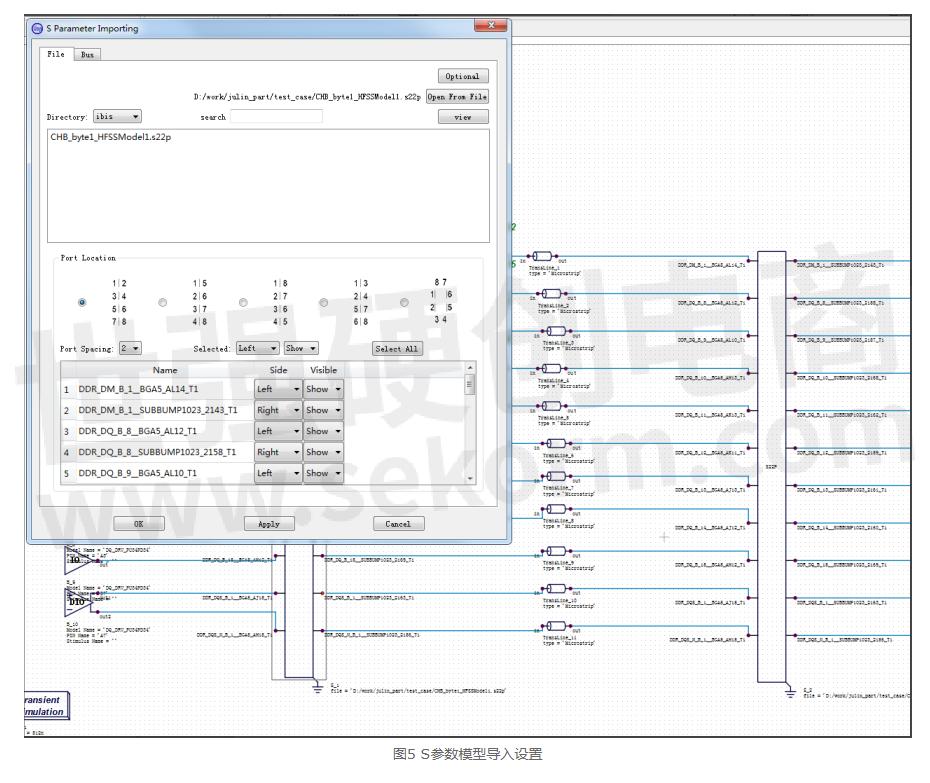

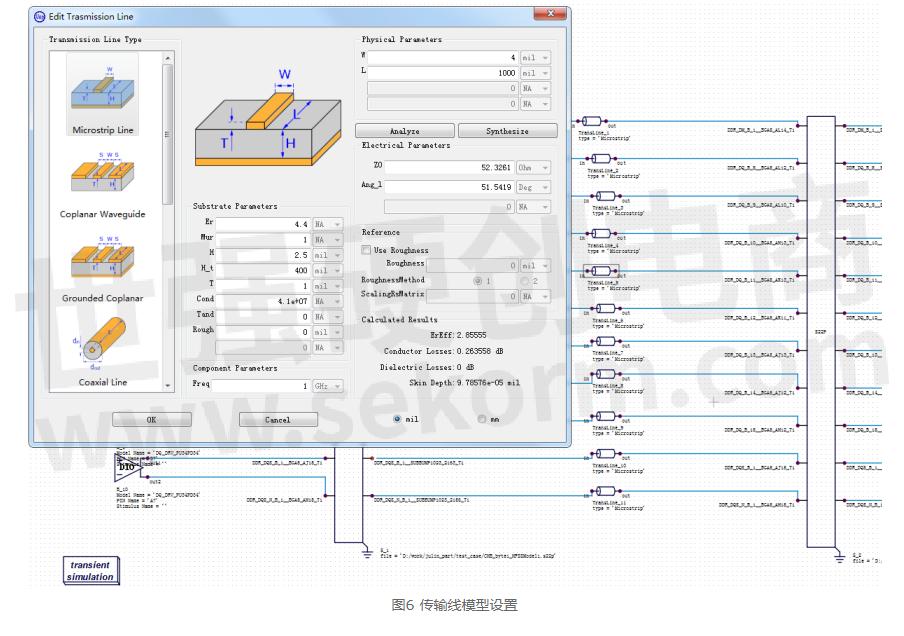

Step 4:Channel模型创建

信号完整性仿真中Channel一般由S参数或者响应的宽带电路模型组成。在pre-layout阶段也可有传输线以及过孔模型作为补充。

本例即为S参数和传输线组合而成。

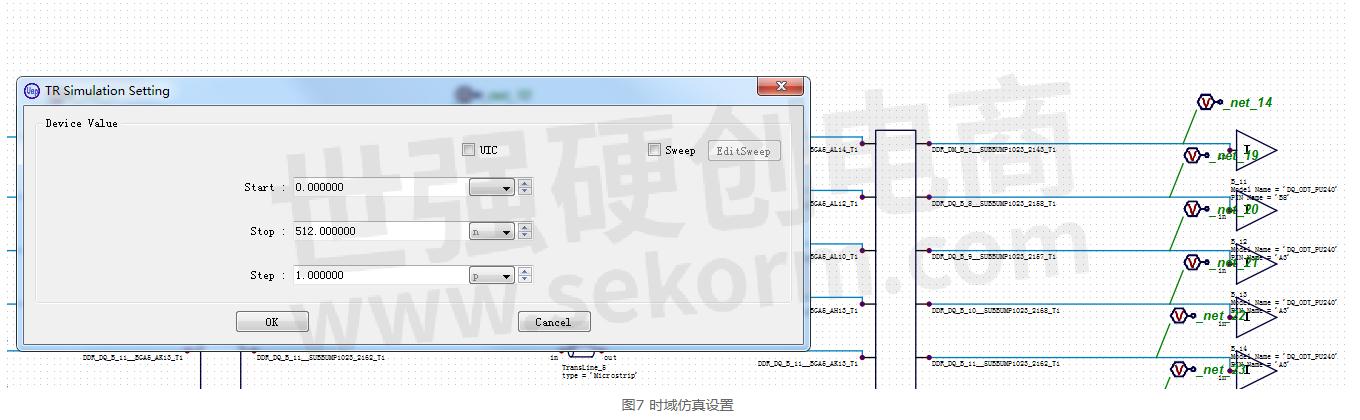

Step 5:仿真设置

系统电路搭建完成后,需要添加波形/眼图观测点以及瞬态仿真控制,如下图:

仿真时间以码型长度*UI来衡量,观测点一般以激励点和接收端输入点作为必选点。

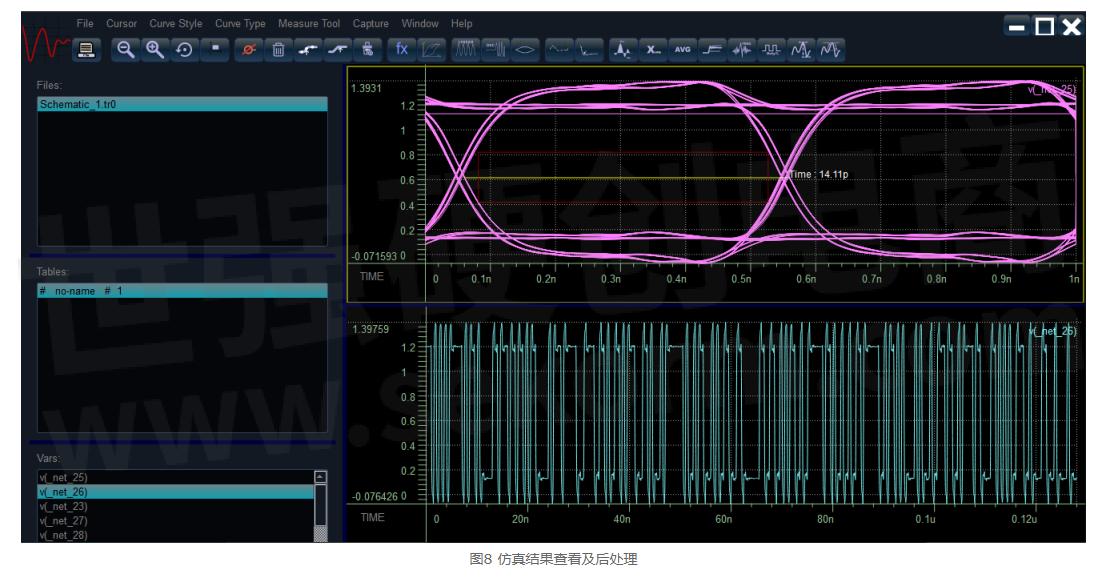

Step 6:波形查看及后处理

仿真结束后,SIDesigner内嵌的波形处理器自动允许导入生成的波形,用户可以对仿真结果进行后处理以及测量。

本文以一个简单的DDR仿真案例来介绍如何在SIDesigner中完成并行接口的信号完整性分析。作为一款以信号完整性为重心的通用电路仿真软件,SIDesigner能完成除3D EM建模之外的所有SI/PI相关工作。用户可以在SIDesigner中方便的进行各种假设性分析以挖掘设计优化方向。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由可莉转载自巨霖科技,原文标题为:SIDesigner实现并行接口信号完整性分析案例,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

巨霖科技PowerExpert软件——简单易用的自定义变压器仿真

电源设计在现在的硬件产品设计里是绕不开的课题。在前面的文章中,我们已经探讨过几种DCDC转换器,今天我们来探讨另一个低损耗的升降压方案变压器。使用巨霖科技的PowerExpert软件搭建一个简单的自定义变压器,实现仿真,方便产品设计。

【应用】沁恒USB转串口芯片CH340N用于消费类电子产品,采用SOP-8封装,无需外部晶振

沁恒推出的USB转串口CH340N可广泛应用于消费类产品中,实现将MCU串口信息通过USB打印到上位机终端,采用标准8脚贴,尺寸比较小,而且内部已集成时钟电路无需外部晶振,用户使用比较简单,完全满足普通用户的串口调试功能。

SUNSTAR聚氨酯体系底部填充胶991,具有低温快速固化性能,用于消费类电子芯片底部填充

SUNSTAR日本经过不断尝试研发出一款单组份聚氨酯底部填充胶产品,可以80℃*10min完全固化,硬度85A,返修温度降低到220℃*80s,同时产品的可靠性测试也都满足测试要求,得到客户的高度好评;同时具有良好的抗弯疲劳强度性能、耐落下冲击性能,用于消费类电子产品。

IBIS文件中的Series Model简介及设计仿真实例

本文详细了解一下文件中的一类特殊模型——Series Model。以巨霖科技的信号完整性仿真工具SIDesigner为例,查看如何在信号完整性分析中使用Series Model。

CX3225GB〔消费类电子产品应用〕晶体谐振器

描述- 该资料主要介绍了CX3225GB型号的表面贴装型晶体谐振器,适用于消费类电子产品。资料详细描述了该产品的型号表示方法、特点、规格、应用领域以及外形尺寸等信息。

型号- CX3225GB

【产品】支持蓝牙5.2的SoC EFR32BG22系列,可满足智能家居、消费类电子、商业和工业物联网应用需求

Silicon Labs(亦称芯科科技)新年发布的特别优化的蓝牙单芯片SoC解决方案-EFR32BG22(BG22),支持蓝牙5.2、Bluetooth® Low Energy、蓝牙网状网络和1米以下测向精度,适用于物联网产品的大量生产。该系列提供了三种蓝牙SoC产品供选择,专为满足智能家居、消费类电子、商业和工业物联网应用(包括那些需要多年电池使用寿命的应用)对价格/性能的各种要求所打造。

Jitter简介及仿真案例分析

在高速信号传输系统中,Jitter是指信号到达时间的不可预测变化,这种变化可能会导致信号失真、数据错误以及系统性能下降,尤其是在高频应用中,如数据通信、视频传输和高速数字电路,Jitter直接影响着信号的完整性和系统的可靠性。本文巨霖科技来与大家分享Jitter简介及仿真案例分析,希望对各位工程师朋友有所帮助。

CX3225SB〔消费类电子产品应用/ 移动通信应用〕晶体谐振器

描述- 该资料介绍了表面贴装型CX3225SB晶体谐振器,适用于消费类电子产品和移动通信应用。产品具有小型、薄型设计,陶瓷封装,可对应回流焊,并提供多种频率、负载容量和频率容差选项。

型号- CX3225SB,CX3225SB25000D0GSSCC

巨霖科技携EDA核心产品亮相CCIC 2024并发表《高精度通用EDA平台,助力探索未来世界》重要演讲

6月20日-21日在青岛胶州举办了“第21届中国通信集成电路技术及应用大会暨上合新区集成电路产业创新发展大会”(CCIC 2024)。 作为行业领军企业受主办方邀请巨霖科技携带其核心产品参展出席本次大会并发表了重要演讲,成为了本次活动的亮点之一。在展会现场,巨霖的工程师们向与会者详细介绍了巨霖“高精度EDA通用电路仿真平台” 包含的多款核心产品及其技术优势。

【IC】晟矽芯高性能通用型8位MCU MC32P7051系列,消费类电子、锂电数码产品、智能化产品的首选

MC32P7051是晟矽微电新推出的消费类电子产线的产品,是一款高性能IO+AD型8位MCU,采用RISC内核。该产品的各个IP,延续晟矽产品特色,用户可极速上手。可作为消费类电子、锂电数码产品、智能化产品的首选。

CX2016SA〔消费类电子产品应用/ 车载应用〕晶体谐振器

描述- 该资料介绍了KYOCERA的表面贴装型CX2016SA晶体谐振器,适用于消费类电子产品和车载应用。资料详细描述了产品的特点、型号表示方法、规格参数、应用领域和外形尺寸。

型号- CX2016SA,CX2016SA25000D0GSSHH

巨霖科技亮相2023工业软件生态大会,展出新一代工业软件套件和创新应用实践成果

近期, 2023工业软件生态大会在深圳召开。巨霖科技作为重要参展企业亮相深圳会展中心2号馆A027展位、华为“电路板EDA(pEDA数字化)”区域,展出了新一代工业软件套件和创新应用实践成果,巨霖科技创始人兼总经理孙家鑫先生受邀发表了《精准仿真,赋能未来——巨霖高精度EDA电路仿真软件助力科技革命》的主题演讲。

登录 | 立即注册

提交评论