【应用】如何保障100G光模块传输准确性?选对去抖时钟是关键

【摘要】本文介绍了100G光模块实现不同速率的变换转发对数据误码率的要求,作者推荐了一款RMS抖动低至0.3ps的时钟芯片,采用了业界大名鼎鼎的DSPLL数字环专利技术,有效保证高速传输时时钟对数据的采样准确率。

近年来随着用户对100G光模块传输链路需求的快速增长,100G光模块也随着100G传输系统的大规模商用,正逐步占领光传输网络的制高点,获得了快速发展。

100G光模块通常包括线路侧和客户侧,100G客户侧光模块相对线路侧则较为简单。100G客户侧第一代CFP主要由Gearbox、TIA、DRIVER、Laser等器件组成,其中Gearbox是其中一个重要的部件,它可以实现10*10 Gbps到4*25 Gbps不同速率数据的变速转发。如此高速率的转换通常对数据误码率要求较高,因此需要抖动极小的时钟芯片产生发端参考时钟,并且要求时钟与发送的数据保持完全同步。

不同数据传输速率的参考钟完全不同,100G CFP的两种速率就存在161.1328125MHz和644.53125MHz两种同步时钟。由于是同步转发,需要保证收发端时钟也是全同步的。依据光模块时钟需求,100G CFP既要满足低抖动,又要满足全同步,同时还要实现161MHz时钟到644MHz时钟的倍频输出。因此对于100G CFP来说,需要一款高性能的抖动衰减时钟发生器来满足这些需求,保证数据转换和数据发送的准确性。

这里我们推荐一款满足这种要求的时钟发生器Si5326。Si5326采用了业界大名鼎鼎的DSPLL数字环专利技术,使得其抖动指标可以达到0.3ps RMS,可以有效保证高速传输时时钟对数据的采样准确率。

同时Si5326的内部集成频率合成器,能够实现从2kHz到1.4 GHz 频率范围内的任意频点合成输出,能根据客户的需求配置不同的参考时钟。

另外由于Si5326是单数字环,内部只集成一个DSPLL,能够设计成输入输出时钟完全同步,满足同步数据传输的要求。

除了性能要求满足指标,SILICON LABS公司也为Si5326量身定做了配套设计软件DSPLLsim,方便用户直接通过GUI界面软件配置所需的频率计划。

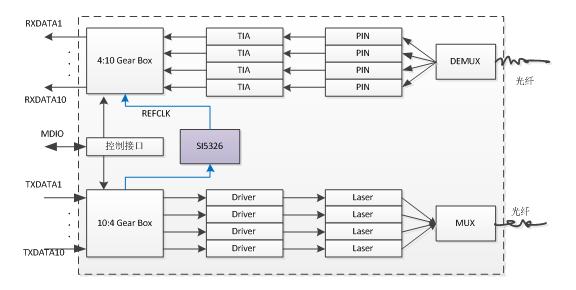

下图是基于Si5326的时钟芯片的100G CFP模块内部结构框图,161M的入口时钟经过Si5326倍频成644M参考钟,为Gearbox提供参考时钟,完美实现Gearbox的速率转换功能。

图1:CFP基于Si5326时钟的CFP内部结构图

- |

- +1 赞 0

- 收藏

- 评论 0

本网站所有内容禁止转载,否则追究法律责任!

相关推荐

【应用】集成14位ADC的小封装MCU助力光模块信号实时监测

EFM8LB1系列MCU是Silicon Labs公司推出的MCU,其具有高精度、可靠性好以及性价比的特性,主要用于光模块信号的实时监测,以便于光通信链路的维护。

【应用】10路差分输出!DSP时钟电路中少不了这款时钟发生器

SI5341最大能支持10路差分输出,低抖动,完全满足DSP所需的时钟性能需求。

12路输出时钟发生器在无线基站上的应用

Si5380是一个高性能的时钟发生器,可以合成多达12路频率输出,输出时钟可以运行在自由模式或同步到4个外部输入之一的时钟,是无线基站时钟应用的理想选择。

【选型】Silicon Labs 时钟和振荡器芯片选型指南

目录- 计时解决方案 晶体振荡器(XO) 压控晶体振荡器(VCXO) 时钟发生器 时钟缓冲器 抖动衰减器 无线时钟 网络同步器

型号- SI56X,SI5382,SI5383,SI5380,SI5381,SI5386,SI5331X,SI5384,SI590,SI5315X,SI591,SI595,SI510,SI598,SI511,SI596,SI597,SI514,SI515,SI512,SI513,SI516,SI52142,SI52143,SI52144,SI51210,SI5394,SI5391,SI5392,SI5397,SI5332X,SI5395,SI569,SI54X,SI567,SI52111,SI52112,SI570,SI571,SI5344H,100G,SI53212,SI5332,SI53208,SI5330X,SI5335,SI53204,SI5334,SI5338,SI547,SI545,SI546,SI549,SL18860,SI5311X,SI5342,SL18861,SI5340,SI52208,SI5341,SI5346,SI52202,SI5347,SI5344,SI52204,SI5345,SI550,SI5348,SI554,SI552,SI5342H,SI5350,SI53306,SI5351,SI53102-AX,SI52212,SI5336X,SI561,SI562,SI560,SI565,SI566,SI564,SI51214,SI51211,SI51218,SI52146,SI52147,SI532,SI533,SI530,SI531,SI534,SI5334X,SI540,SI544,SI541,SI542

【应用】扬杰科技YJA3134KA缓启动MOS在100G光模块上的方案,具备低导通阻抗快速响应特性

本文主要对扬杰的YJA3134KA系列缓启动MOS应用在光模块项目上的优势特性进行了概述.

【经验】如何实现SI534X/SI538X时钟发生器SPI在线编程?

Silicon Labs SI534X、SI538X时钟发生器包括基于模拟PLL的SI5340、SI5341和基于DSPLL技术的SI5342、SI5344 、SI5345、SI5342H、SI5344H、SI5346、SI5347、SI5348以及无线专用时钟SI5380、SI5382、SI5386等时钟芯片产品。目前在光通信、数据中心、服务器、小基站、光模块等产品中有广泛的应用

【产品】抖动率低至0.3ps的去抖时钟芯片Si5326在光模块中的应用

去抖是光模块接收中极其重要的设计之一。Silicon labs的去抖时钟芯片Si5326采用DSPLL专利技术,输出频率抖动最小可以达到0.3ps,因此常被用于光模块接收器当中用来做去抖设计。

【应用】高精度、双通道、小封装运放TP1285T-WS2R-S助力100G光模块产品设计,增益误差小于0.5%

某客户在设计一款100G QSFP28 ER4 NITE光模块时,APD升压电路需设计电流采样电路,用于获取由变压电路输出端输出的电流值,客户需使用高精度、多通道的小封装电流检测运放,结合客户的实际需求本文推荐思瑞浦的TP1285T-WS2R-S。

【经验】无线去抖时钟芯片Si5386相邻输出信号串扰问题解决方法

Si5386是Silicon Labs公司推出的无线去抖时钟芯片,被广泛应用于电信传输网、基站、数据中心等。在实际应用中,通过Clock Builder Pro软件对SI5386输出时钟配置时,如果相邻输出之间带宽小于20MHz,会有警告提示存在输出串扰问题。本文详细介绍这个问题的解决方案。

【经验】Silicon Labs时钟芯片Si5332更改时钟输出频率的方法

Silicon Labs推出的Si5332任意频率的时钟发生器提供最高级别的集成,实现在 10/25/100G 数据中心、通信和工业应用程序中的完整时钟树整合。该芯片输出频率范围为5~ 333.33 MHz,具有 175fs 典型值的抖动性能,根据封装不同有 6路、8路、12路-时钟输出。它既可以工厂预先编程,也可以通过I2C接口,进行系统内编程。

【应用】思瑞浦LDO TPL9032应用于100G光模块,输入电压范围宽,PSRR为81.9dB@1kHz

100G光模块项目需要一款LDO作为电源给CDR供电。推荐3PEAK的TPL9032系列,300mA高PSRR、超低噪声、低压差线性稳压器,具有高输出精度。完全适用于光模块产品。

【应用】SI530在100G相干CFP光模块中用作REF_CLK的参考时钟源,稳定度达到20 ppm且使用方便

100G相干CFP光模块为了数据采集的准确性,特别是保证数据调制后长距离发送而不影响其误码性能,要求有一个稳定的参考时钟源。这里推荐Silicon Labs的经典去抖时钟发生器SI5326,但SI5326在这种情况下的应用不是用来锁定输入源,而是以工作在自由振荡模式下工作,其输出参考源是REF_CLK的时钟。对于该参考源推荐使用晶振SI530,稳定度达到20 ppm,满足光通信的设计需求。

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

【应用】初始精度0.15%的思瑞浦电压基准芯片用于100G光模块,输出噪声低至50μVpp

在100G光模块中,需要一款精度高的基准源芯片。本文推荐思瑞浦的电压基准芯片TPR3325-QF11R-S,输入电压范围VOUT+300mV至5.5V;初始精度高,仅为0.15%,具备低输出噪声50μVpp,非常适合用于光模块产品。

一个使用无线专用去抖时钟芯片Si5386配置JESD204B接口时钟延时的应用案例

Silicon Labs公司的无线专用去抖时钟芯片Si5386集成DSPLL核心技术的JESD204B去抖时钟芯片,广泛用于无线基站设备中,用来消除由于离散的VCXO和环路滤波器组件带来的额外噪声。本案例就是一个实现4对延时调节功能JESD204B的DCLK/SYSREF配置的例子。

电子商城

现货市场

服务

拥有IC烧录机20余款,100余台设备,可以烧录各种封装的IC;可烧录MCU、FLASH、EMMC、NAND FLASH、EPROM等各类型芯片,支持WIFI/BT模组PCBA烧录、测试。

最小起订量: 1 提交需求>

根据用户的蓝牙模块,使用Bluetooth 蓝牙测试装置MT8852B,测试蓝牙1.0至5.1,包括传输速率、功率、频率、调制和接收机灵敏度,生成测试报告。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论