Multi-Core Debug and Trace Tool for R-Car S4

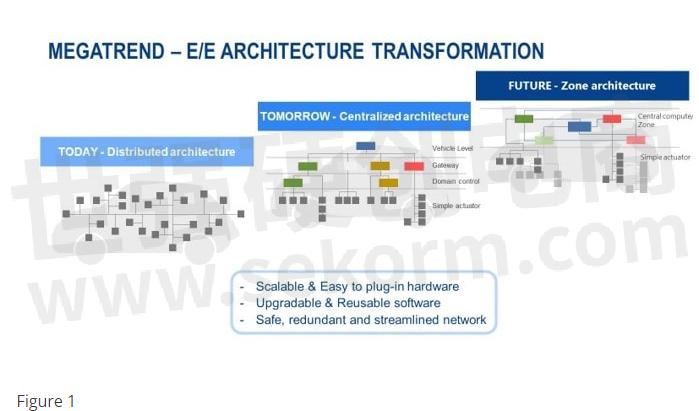

Evolution of E/E Architecture

With the evolution of automated driving, electrification, and connected technology, the electronic and electric control (E/E architecture) of automobiles is becoming increasingly complex and sophisticated. The overall E/E architecture is becoming a very large and complex system, with multiple ECUs working together. It is said that each car has more than several dozen microprocessors and more than 50 million lines of software.

The R-Car S4, announced by RENESAS in October 2021, is the core device of E/E architecture that supports high performance and a variety of high-speed networks. R-Car S4 is equipped with several microprocessors such as Arm® Cortex®-A52, Arm® Cortex®-R55, and G4MH/RH850 microprocessors. The software on these microprocessors works together across processors to enable the advanced applications required by the new E/E architecture, such as gateway functions that securely connect the in-vehicle network to the off-vehicle network.

Multi-Core System Debugging

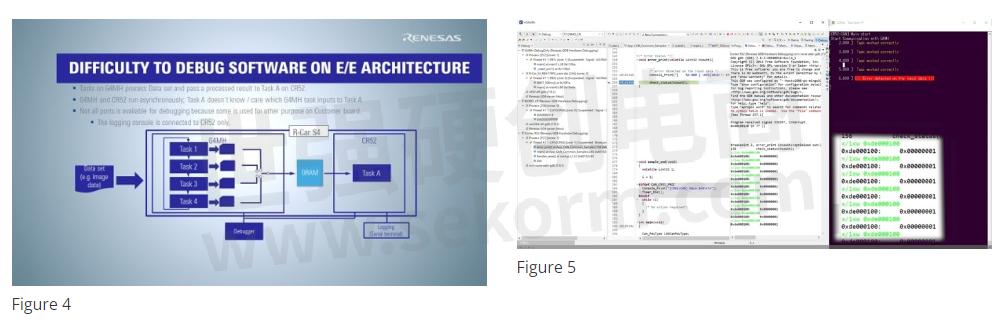

Consider developing software that works together on such multiple microprocessors. For example, suppose that the software on each of the Arm Cortex-A52, Arm Cortex-R55, and G4MH/RH850 microprocessors in R-Car S4 are working together and that some abnormality occurs in the G4MH/RH850 software. (Figure 2)

In conventional debugging methods, the G4MH/RH850 is stopped, and the status of registers, memory, and variables are examined using a debugger. However, even if the G4MH/RH850 is stopped, the Arm Cortex-A52 and Arm Cortex-R55 are still running, so when a problem occurs in the G4MH/RH850 software, the Arm Cortex-A52 and Arm Cortex-R55 software cannot be checked. Even if you try to see what was happening, you may not be able to get to the problem because you have moved on without stopping, or because stopping the G4MH/RH850 software has changed the operating state.

The synchronous debugging function using the multi-core debug and trace tool released this time enables synchronous execution and stops at a certain time, making it possible to check the status of registers, memory, and variables at the time when the abnormality occurred, as well as the software status. As a result, problems can be analyzed, and causes identified efficiently.

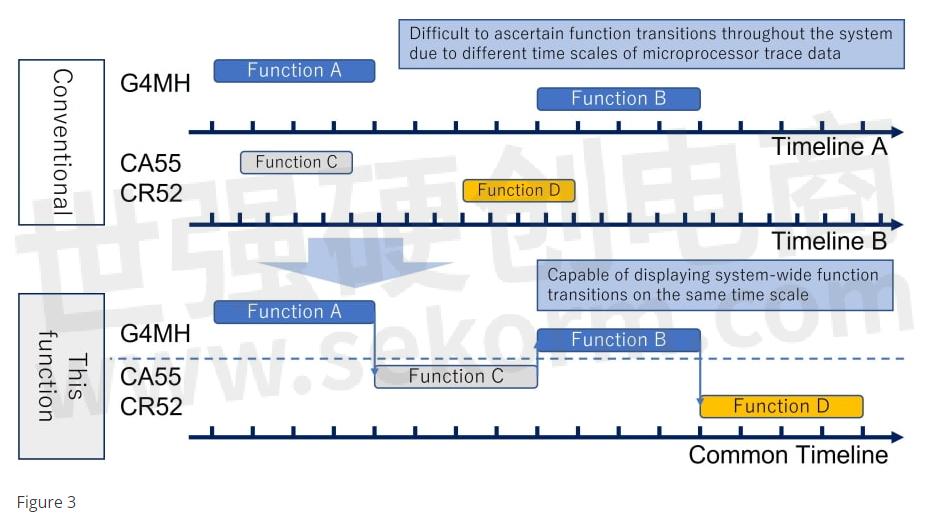

Another function of the multi-core debug and trace tool, synchronous tracing can be used not only for problem analysis but also for performance improvement by clearly checking execution speed bottlenecks at a glance. For example, as shown in Figure 3, the conventional trace function confirms the flow of software operation by checking the transitions of each microprocessor function. However, since the time scale of each trace is different, it is difficult to grasp the flow of software that is working together. With the synchronous trace function, the timeline of trace results for all microprocessors is the same, and the flow of each software operation can be clearly understood immediately. Problem analysis and performance improvement studies can then be carried out very easily.

Future Developments

Multicore debug and trace tools are a powerful ally for analyzing the behavior of software running in complex intertwined E/E architectures. The released tool targets multiple microprocessors implemented in a single SoC, such as the R-Car S4. In the future, Renesas plans to make this tool even more effective for software development at the ECU (Electronic Control Unit) level by adding support for synchronous debugging and tracing of software that operates in conjunction with multiple devices, as well as support for Virtual Turnkey, which was announced at the same time as this release. We also plan to support Virtual Turnkey, which was announced at the same time.

- |

- +1 赞 0

- 收藏

- 评论 0

本文由深蓝的鱼转载自Renesas News,原文标题为:Multi-Core Debug and Trace Tool for R-Car S4,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【经验】SoC R CAR V3H2 端侧推理输出的rcar_output.npy数据查看方法

RENESAS R CAR V3H2 端侧推理输出的数据有cvs格式,总共512个输出,同时把cvs数据转化为npy格式保存为一个rcar_output.npy文件,那我如何查看这些数据呢,本文记录数据查看方法。

【经验】使用瑞萨SoC R CAR V3H2 cnn工具链实现onnx模型转caffe模型的实操

R CAR V3H2 的cnn神经网络模块需要运行int16的定点模型,而onnx模型首先需要通过cnn工具链转成caffe模型,然后再转成端侧的可执行模型,本文使用瑞萨的cnn工具链实现onnx模型转caffe模型。

【经验】SoC R CAR V3H2 cnn模型转换后执行以及benchmark过程实操指南

RENESAS SoC R CAR V3H2 cnn模型转换后的输出文件有bcl和.pb 2类,都是可以在端侧执行的,本文记录.pb的推理输出以及benchmark过程实操及解析。

【产品】瑞萨新一代SOC R-Car V3H,专为自动驾驶前置摄像头应用

瑞萨开发了专门针对前置摄像头应用的SoC——R-Car V3H,集成了专门针对图像处理的功能单元,它比R-Car V3M在视觉处理方面的性能提高了5倍,并只有0.3瓦的超低功耗,更好的适应自动驾驶的需求。

Renesas(瑞萨电子) R-Car M3车载SoC设备概述手册

描述- 本资料概述了Renesas Electronics的R-Car M3系列SoC的初步规格。R-Car M3具备下一代车载导航系统所需的基本功能,包括双核1.5GHz ARM Cortex-A57和四核1.3GHz ARM Cortex-A53核心、LPDDR4内存控制器、多种接口和图形处理单元。资料详细介绍了处理器、内存、显示、视频处理、音频接口、存储和网络等模块的规格和功能。

型号- R-CAR M3

瑞萨公开下一代车用SoC和MCU处理器产品路线图,全新R-Car MCU系列扩展其车辆控制产品阵容

瑞萨电子公开了针对汽车领域所有主要应用的下一代片上系统(SoC)和微控制器(MCU)计划。未来产品阵容包括采用先进小芯片封装(Chiplet)集成技术的R-Car SoC和基于Arm®核的车用MCU。

【选型】车联网V2X车载端产品(V-BOX)推荐:车规级SoC RCAR M3,7核主频1.8ghz、运力30DMIPS

3GPP给出了相关的应用场景,车联网(V2X)分:V2N/V2I/V2P/V2V这几种应用。那么在硬件设计上,现阶段主要是V2X的车载OBU产品和路测的RSU产品。笔者当下接到的项目则是整合传统T-BOX的OBU产品:V-BOX。整个系统功能融合了TBOX和V2I/V2N/V2V的功能。可以使用瑞萨RCAR M2 SoC,内部集成2核A57和4核A53,还有实时内部R7。

【产品】全新开放式平台,加大对ADAS及自动驾驶的支持

新型R-Car V3M SoC符合ISO26262功能安全标准,为视觉处理提供了低功耗硬件加速功能,还配有内置图像信号处理器。

【应用】支持EtherCAT协议的瑞萨单芯片SoC用于伺服系统,实现实时响应,降低20%成本

在伺服系统的应用上,对于主控SoC的选择非常重要,Renesas SoC RZ/T1系列的R7S910025可以实现联网实时响应,采用ARM Coretex-R4F高实时性内核,自带FPU浮点运算单元,最高支持600MHz主频,达到962MIPS的运行速度。

DA16200超低功耗Wi-Fi SoC

型号- DA16200-00000F22,DA16200-00001F22,DA16200-00001A32,DA16200-RRXXXYYZ,DA16200,DA16200-00000A32

【经验】瑞萨RZ/T1 SoC芯片最小系统关于应用ΔΣ的IGBT波动干扰解决

很多客户使用了瑞萨RZ/T1的ΔΣ delta sigma,反馈IGBT波动有干扰。电源的干扰有可能对芯片的工作有影响,因为没有符合电源规范。变频的是MCU,电源可以+-20%呢,而rzt1是要求5%。 CPU没有出现异常,也可能是因为主频是450M,离600M还有很大的余量。本文介绍解决办法。

【经验】SoC R CAR V3H2 CNN工具链转换restnet18 caffe模型为端侧可执行命令过程解析

RENESAS SoC R CAR V3H2 CNN工具链最主要的功能就是把caffe,onnx等模型转换为V3H2 芯片端可执行模型,命令,本文记录并分析此转换过程。

【经验】解决瑞萨RZ/T1 SoC芯片最小系统硬驱IIC断点死循环问题

客户反应问题:设置瑞萨RZ/T1高性能SoC芯片最小系统硬驱IIC断点,执行不下去,进入while死循环。本文介绍如何解决该问题。

【产品】采用业界先进16nm制程,算力高至7TOPS的自动驾驶R-Car SoC,ADAS解决方案 | 视频

在2021年5年28日汽车电子专场|世强硬创新产品研讨会中,瑞萨ADAS技术专家Cross为我们我们做了演讲,视频介绍了R-Car V3X系列ADAS技术方案,重点讲解了R-Car V3M,V3H1.1,V3H2.0的技术指标规格。

【经验】如何实现SoC R CAR S4从网络启动配置操作?

R CAR S4的DEMO板上emmc中的内核以及文件系统烧录,需要先从网络启动系统后,然后通过挂载emmc,才能把内核以及文件系统copy到emmc分区中,本文记录spider board的配置烧录过程。

电子商城

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥8.1764

现货: 102,628

品牌:SILICON LABS

品类:Mighty Gecko Multi-Protocol Wireless SoC

价格:¥27.0929

现货: 90,767

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥10.4994

现货: 50,699

现货市场

登录 | 立即注册

提交评论