【应用】高性能晶振+抖动衰减器,满足小基站时钟树一站式需求

【摘要】在小基站时钟树的应用中,高稳定度晶振Si530可作为整个设备时钟树的时钟源,时钟衰减器Si534x/Si538x可作为多路输出参考时钟源。采用单芯片方案设计,不仅可以节省PCB空间,还可以有效抑制分离器件带来的噪声,是实现小基站时钟设计的上上之选。

公用移动通信基站(简称基站),是无线电台的一种形式,是指在一定的无线电覆盖区中,通过移动通信交换中心,与移动电话终端之间进行信息传递的无线电收发信电台。基站主要设备除了电源单元模块外,还包括远端射频模块(Remote Radio Unit,简称RRU)和室内基带处理单元(Building Baseband Unit,简称BBU)。

BBU集中放置在机房,RRU可安装至楼层,BBU与RRU之间采用光纤传输,RRU再通过同轴电缆及功分器(耦合器)等连接至天线,即主干采用光纤,支路采用同轴电缆。BBU和RRU由于速率较高,会用到高速SERDES芯片或者带SERDES接口的高性能FPGA。

高速信号的处理,对信号相噪特性要求较高,而相噪主要受时钟信号的抖动和偏移参数等的影响。这些参数如果处理不好,可能会使SERDES内部FIFO溢出,导致通信异常。因此,如果充分利用高性能的晶振作为本地参考钟,再配合高性能的抖动衰减器时钟芯片,可以很好地实现BBU和RRU的时钟树结构,保障通信数据的稳定传输。

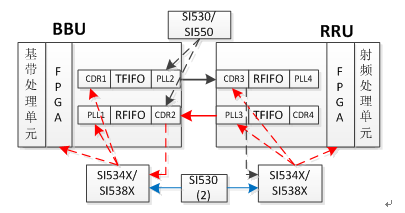

基于SILICON LABS高稳定度晶振和高性能抖动衰减器的时钟链路,可以有效解决抖动和偏移的问题。Si530是Silicon Labs的新一代高性能晶振,最大输出频率可达1.4GHz,采用Silicon Labs独有的DSPLL技术,可以将jitter控制在300fs以内。而Si534x/Si538x是Silicon Labs新推出的高性能抖动衰减器,其功耗小、尺寸低,抖动性能可以达到100fs以内,满足无线基站通信的任何时钟抖动需求,且满足各基站之间的分散传输要求。下图为使用Si530作为时钟源、Si534x/Si538x作为多路输出参考时钟源的BBU和RRU时钟树架构图。

图1:BBU和RRU时钟树架构图

框图中,BBU和RRU通过光纤相连,BBU本身采用高稳定度的晶振作为参考钟,同时也给BBU的SERDES高速锁相环提供参考时钟。待高速锁相环PLL2稳定工作后,即BBU和RRU链路工作稳定后,BBU的SERDES接口CDR2会恢复出稳定的时钟并输出。这个时钟经过抖动衰减器Si534x/Si538x处理后作为锁相环PLL11和CDR1的参考钟。在RRU设备中,同样存在相同的时钟架构,基于同步设计,一般RRU会选择从SERDES侧的CDR3恢复出稳定的时钟,经过抖动衰减器Si534x/Si538x后作为RRU侧PPL3和SERDES与FPGA之间CDR器件的参考时钟,最终实现时钟链路的同步设计。

通过基站BBU和RRU设备上述工作原理的分析可以得出,Silicon Labs的时钟芯片可以满足小基站时钟树一站式的时钟需求。高稳定度晶振Si530作为整个设备时钟树的时钟源,时钟衰减器Si534x/Si538x作为多路输出参考时钟源,给SERDES和CDR提供稳定的参考钟。其中,Si534x/Si538x最大支持10路时钟输出,不仅支持多通道,还支持抖动衰减功能,可以对输入质量较差的时钟去抖,获得更佳抖动指标的时钟输出。此外,采用单芯片方案设计,不仅可以节省PCB空间,还可以有效抑制分离器件带来的噪声,是实现小基站时钟设计的上上之选。

- |

- +1 赞 0

- 收藏

- 评论 0

本网站所有内容禁止转载,否则追究法律责任!

相关推荐

【应用】10路差分输出!DSP时钟电路中少不了这款时钟发生器

SI5341最大能支持10路差分输出,低抖动,完全满足DSP所需的时钟性能需求。

【应用】无线基站专用时钟芯片,可输出最高至712.5MHz任意频率时钟信号

Silicon Labs Si5386时钟芯片均实现XTAL内置,在节省客户PCB空间的同时,有效的消除分离器件带来的噪声影响。

12路输出时钟发生器在无线基站上的应用

Si5380是一个高性能的时钟发生器,可以合成多达12路频率输出,输出时钟可以运行在自由模式或同步到4个外部输入之一的时钟,是无线基站时钟应用的理想选择。

【经验】时钟发生器Si5341型号定制以及输出串扰问题解决方法

Silicon Labs公司推出的时钟发生器Si5341最大能够支持10路差分输出,输出频率范围100Hz~712.5MHz,输出抖动范围均小于100 fs(0.1 ps),并且Si5341内部带有模拟锁相环,配合Silicon Labs的专利MultiSynth技术,能够以0 ppm合成所需的频点,本文将详细介绍Si5341型号定制以及输出串扰问题解决方法。

【经验】如何实现SI534X/SI538X时钟发生器SPI在线编程?

Silicon Labs SI534X、SI538X时钟发生器包括基于模拟PLL的SI5340、SI5341和基于DSPLL技术的SI5342、SI5344 、SI5345、SI5342H、SI5344H、SI5346、SI5347、SI5348以及无线专用时钟SI5380、SI5382、SI5386等时钟芯片产品。目前在光通信、数据中心、服务器、小基站、光模块等产品中有广泛的应用

5G基站晶振:晶科鑫9X系列,体积小巧,频率范围覆盖5-50MHz,是室分基站晶振首选

5G基站晶振是新一代通信技术的核心组件,随着5G技术的蓬勃发展,其重要性日益凸显。晶科鑫,作为晶振领域的佼佼者,推出的9X系列晶振,以其卓越的性能和独特的设计,成为5G基站室分系统中的明星产品。

【经验】无线去抖时钟芯片Si5386相邻输出信号串扰问题解决方法

Si5386是Silicon Labs公司推出的无线去抖时钟芯片,被广泛应用于电信传输网、基站、数据中心等。在实际应用中,通过Clock Builder Pro软件对SI5386输出时钟配置时,如果相邻输出之间带宽小于20MHz,会有警告提示存在输出串扰问题。本文详细介绍这个问题的解决方案。

【经验】Silicon Labs时钟芯片Si5332更改时钟输出频率的方法

Silicon Labs推出的Si5332任意频率的时钟发生器提供最高级别的集成,实现在 10/25/100G 数据中心、通信和工业应用程序中的完整时钟树整合。该芯片输出频率范围为5~ 333.33 MHz,具有 175fs 典型值的抖动性能,根据封装不同有 6路、8路、12路-时钟输出。它既可以工厂预先编程,也可以通过I2C接口,进行系统内编程。

浅谈5G小基站中时钟发生器的应用

随着5G技术的快速发展,5G小基站成为了实现网络密集覆盖的关键技术之一。而在5G小基站中,时钟发生器扮演着至关重要的角色。本文赛思将从时钟发生器在5G小基站中的应用出发,探讨其重要性、应用特点及面临的挑战,并提出相应的解决方案。

【选型】三点关键因素决定5G基站时钟选择SI5386A-E-GM还是LMK04828

Silicon Labs SI5386A-E-GM集成DSPLL核心技术的JESD204B去抖时钟芯片,广泛用于5G基站设备中。SI5386A-E-GM和LMK04828都是目前比较主流的无线时钟发生器,但是相对于SI5386A-E-GM来说,LMK04828部分性能、应用特点是无法媲美的。

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

小基站这么火!扬兴石英可编程晶振YSO690PR和有源晶振YSO110TR怎么选?

在5G技术加持下,小基站取得惊人的进步,快速发展的背后离不开电子元件的使用,晶振在通讯设备中起着关键作用,广泛应用于各种时间显示和时间控制产品中,那么小基站通常用哪些晶振呢?

【经验】Silicon Labs时钟芯片Si5332写入配置寄存后无频率输出解决方法

Si5332是Silicon Labs公司推出的任意频率的时钟发生器,被广泛应用于消费电子、电信传输网、基站、数据中心等。该芯片输出频率范围为5~333.33 MHz,具有175fs典型值的抖动性能,同时该芯片具有任意频点输出、可内置多组频率计划等特点。在应用中,Si5332在写入配置寄存器后,没有频率输出,该如何解决呢?本文将详细讲解。

一个使用无线专用去抖时钟芯片Si5386配置JESD204B接口时钟延时的应用案例

Silicon Labs公司的无线专用去抖时钟芯片Si5386集成DSPLL核心技术的JESD204B去抖时钟芯片,广泛用于无线基站设备中,用来消除由于离散的VCXO和环路滤波器组件带来的额外噪声。本案例就是一个实现4对延时调节功能JESD204B的DCLK/SYSREF配置的例子。

时钟芯片SMST5351优势解读

时钟芯片SMST5351优势解读SMST5351并非传统意义上的“时钟计数芯片”,它本质上是一个信号转换器件,业内又称“时钟发生器”。SMST5351主要应用于:激光测距仪、音视频会议系统、监控图传、激光打印、机器人、商业储能、小基站、网关、服务器等,应用可谓是极为广泛。

电子商城

现货市场

服务

测试范围:扬兴晶振全系列晶体,通过对晶体回路匹配分析,调整频率、驱动功率和起振能力,解决频偏、不起振、干扰、频率错误等问题。技术专家免费分析,测完如有问题,会进一步晶振烧录/修改电路。

实验室地址: 深圳 提交需求>

提供CE测试服务,通过晶体回路匹配分析,给出测试报告。支持EPSON所有MHz无源晶体、32.768KHz晶体。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳/上海 提交需求>

登录 | 立即注册

提交评论