DDR芯片的PCB设计要点

DDR:Double Date Rate双倍速率同步动态随机存储器。

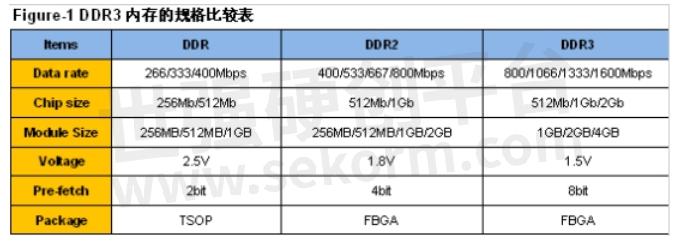

DDR、DDR2、DDR3常用规格:

阻抗控制要求

单端走线控制50欧姆,差分走线控制100欧姆

1. 地址线(Address Line)阻抗控制要求:为了减小地址线上的反射和信号干扰,通常要求地址线的阻抗匹配,并确保阻抗的稳定性和一致性。

2. 数据线(Data Line)阻抗控制要求:为了减小数据线上的反射和信号干扰,通常要求数据线的阻抗匹配,并确保阻抗的稳定性和一致性。

3. 时钟线(Clock Line)阻抗控制要求:时钟线的阻抗匹配对于DDR总线的稳定性和数据传输速率至关重要,通常要求时钟线的阻抗匹配,并确保阻抗的稳定性和一致性。

4. 总线终端阻抗控制要求:为了减小总线的反射和信号干扰,常常使用总线终端阻抗匹配技术,确保总线的阻抗和信号匹配,提高信号的完整性和传输质量。

5. PCB(Printed Circuit Board)设计要求:DDR阻抗控制还包括对PCB布线的要求,包括准确计算和设置阻抗值、控制阻抗偏差等,以确保信号的传输质量和性能。

总的来说,DDR阻抗控制要求是为了保证DDR总线的信号完整性和稳定性,减小反射和信号干扰,提高数据传输速率和质量。具体的阻抗数值和要求会根据具体的DDR规格和设计要求而有所差异,需要在设计过程中进行详细的分析和优化。

DDR布局要求

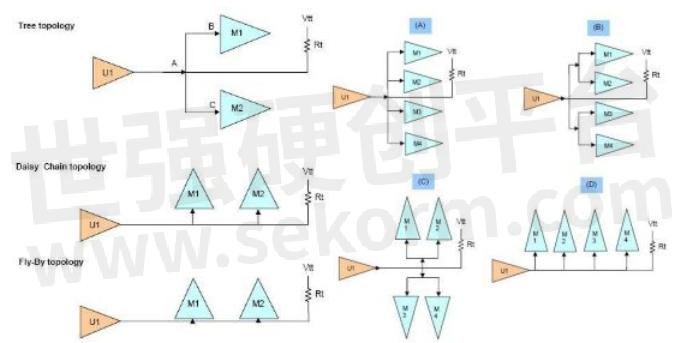

通常,根据器件的摆放方式不同而选择相应的拓扑结构。

在DDR PCB布局设计中,有一些常见的要求和指导原则,以确保总线信号的完整性和稳定性:

1. 分层布局(Layer stackup):使用合适的分层布局,通常采用多层PCB,其中一些层用于信号引线和电源/地平面。分层布局可以有效地减少信号之间的干扰,并提供良好的电源/地参考平面。

2. 地平面(Ground plane):确保足够大块的地平面,作为信号引线之间的隔离层,并提供良好的回流路径,以减少信号的干扰和噪音。

3. 信号引线的走向和长度匹配:为了保持信号传输的完整性,对于关键的时钟和数据线,要求他们的走向和长度匹配,并采用相同的层间穿越方式。

4. 地与电源引线的匹配:为了减少地与电源引线之间的噪声干扰,建议对它们进行匹配,确保它们彼此间的长度和走向相似。

5. 适当的隔离:在布局中,应将关键信号(如时钟线)与其他信号,尤其是高速信号,保持一定的物理距离,以减少干扰。

6. 信号线的屏蔽和阻尼:在布局中,可以考虑使用屏蔽技术和阻尼电阻,以减少信号的串扰和反射。

7. 地和电源的引脚布局:在DDR组件的引脚布局中,要注意地和电源引脚的布局和连接,以确保它们在布局中的位置和连接方式符合DDR设计要求。

8. 差分信号匹配:对于差分信号,如数据和地址线,要求它们的匹配和走线长度一致,以保持信号的平衡和抗干扰能力。

请注意,DDR PCB布局设计需要考虑诸多因素,包括DDR规格、频率、时钟速度等。因此,确保与DDR芯片厂商的规格和设计要求保持良好的沟通和协作,是非常重要的。

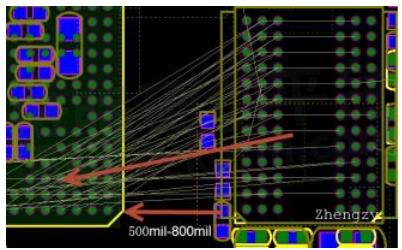

A、DDR*1片,一般采用点对点的布局方式,靠近主控,相对飞线Bank对称。间距可以按照是实际要求进行调整,推荐间距为500-800mil。

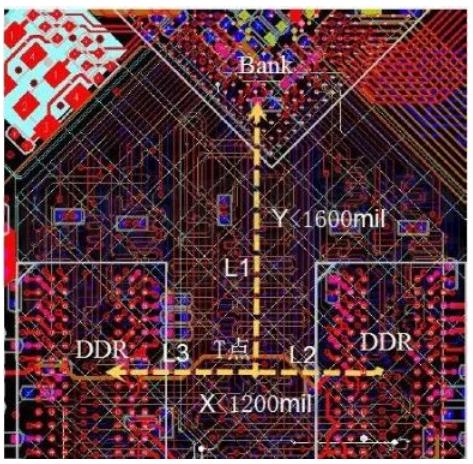

B、DDR*2片,布局相对主控飞线Bank对称,常采用T型拓扑结构,推荐间距如下:

等长要求L1+L2=L1+L3

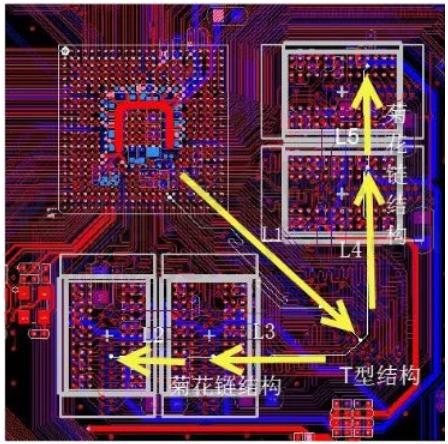

C、DDR*4片,以下列出了常用的4片DDR布局拓扑结构。

针对于DDR2,这些拓扑结构都是能适用的,只是有少许的差别。

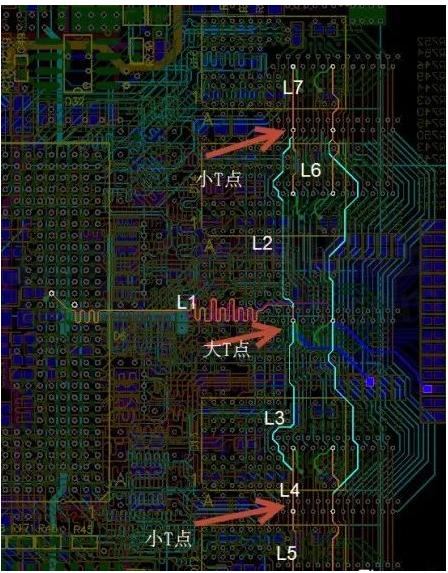

若PCB布线空间允许,Address/Command、Control、CLK,应优先采用单纯的“T”型拓扑结构,并尽可能缩短分支线长度,如上面拓扑结构的B图所示。

等长要求L1+L2+L6=L1+L2+L7=L1+L3+L4=L1+L3+L5

然而,菊花链式拓扑结构被证明在SI方面是具有优势的。对于DDR3的设计,特别是在1600 Mbps时,则一般采用D所示菊花链拓扑结构进行设计。

PCB布线空间有限的,可以采用“T”型拓扑和菊莲拓扑混合的结构,如下图所示:

混合拓扑结构中“T”型拓扑的要求与两片DDR2/3相同。

等长要求L1+L3+L2=L1+L4+L5

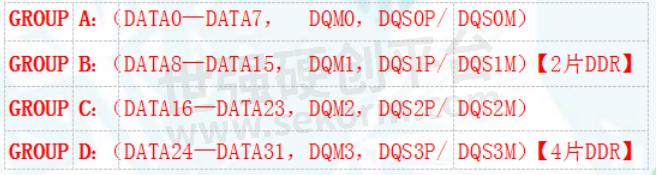

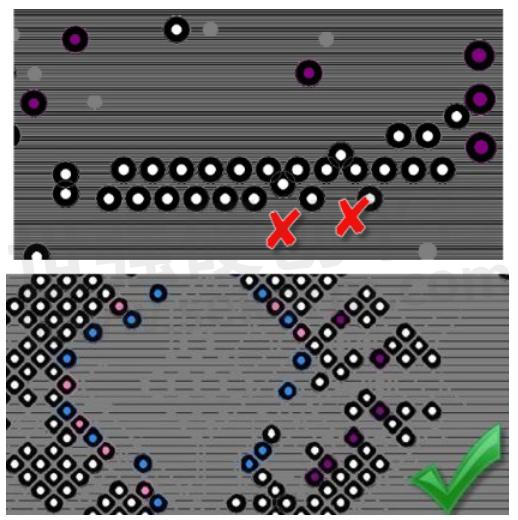

4. 信号分组以及走线要求(以下以4片DDR3设计进行说明)

A、32条数据线(DATA0-DATA31)、4条DATAMASKS(DQM0-DQM3),4对DATASTROBES差分线(DQS0P/DQS0M—DQS3P/DQS3M)

这36条线和4对差分线分为四组:

再将剩下的信号线分为三类:

Address/Command、Control与CLK归为一组,因为它们都是以CLK的下降沿由DDR控制器输出,DDR颗粒由CLK的上升沿锁存Address/Command、Control总线上的状态,所以需要严格控制CLK与Address/Command、Control之间的时序关系,确保DDR颗粒能够获得足够的、最佳的建立/保持时间。

B、误差控制,差分对对内误差尽量控制在5mil以内;数据线组内误差尽量控制在+-25mil以内,组间误差尽量控制在+-50mil以内。

Address/Command、Control全部参照时钟进行等长,误差尽量控制在+-100mil以内。

C、数据线之间间距要满足3W原则,控制线、地址线必要时可稍微放宽到2W~3W,其他走线离时钟线20mil或至少3W以上的间距,以减小信号传输的串扰问题。

D、VERF电容需靠近管脚放置,VREF走线尽量短,且与任何数据线分开,保证其不受干扰(特别注意相邻上下层的串扰),推荐走线宽度>=15mil。

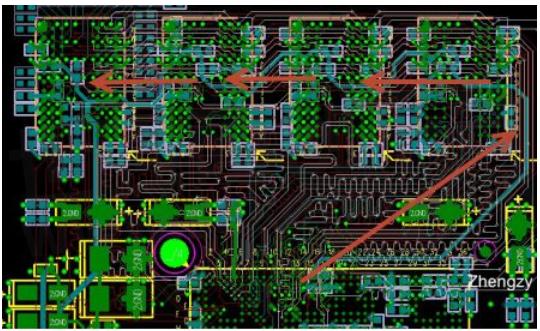

E、DDR设计区域,这个区域请保障完整的参考平面,如下方图片所示:

- |

- +1 赞 0

- 收藏

- 评论 0

本文由咪猫转载自Misenbo(淼森波公众号),原文标题为:DDR 芯片的 PCB 设计要点,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

详解DDR技术内核 及Layout注意事项

这些是一些常见的DDR走线规则,当然,具体的规则可能因DDR版本、芯片厂商和PCB设计要求而有所不同。在进行DDR走线设计时,务必参考相关的DDR规范和芯片厂商的建议,以确保良好的信号完整性和性能。

解析DDR信号完整性测试内容、技巧及注意事项

DDR(双数据速率)信号完整性测试是对DDR系统中信号传输的稳定性和准确性进行验证的过程。那么关于DDR信号完整性测试的内容、技巧及注意事项您有了解吗?本文将为您进行详细介绍。

10G的SFP+_Rx如何测试?干货供收藏

10G的SFP+_Rx测试技术要求及方法介绍,SFP+_Rx测试是确保光纤模块性能的重要环节,通过系统化的测试流程和方法,可以有效验证设备的接收性能,保障通信的可靠性与稳定性。

解析LPDDR4硬件设计及测试注意事项

LPDDR4(Low Power Double Data Rate fourth generation)是一种低功耗的存储器标准,用于移动设备和便携式应用。本文中Misenbo为大家介绍LPDDR4硬件设计及测试注意事项。

DP1.4眼图信号质量差解决方案详解

眼图测试是验证信号质量的基本方法。通过观察信号眼图的眼宽和眼高,以及是否触碰到Eye Mask,可以判断源设备输出的信号是否足以被接收设备识别。此外,数字信号的眼图还包含丰富的信息,能够反映数字信号的整体特性,帮助评估信号质量。因此,眼图分析是数字系统信号完整性分析的关键之一。 想要解决DP1.4眼图质量差的问题,需要从多个方面进行深入分析。

【经验】淼森波实验室DDR测试案例,如何区分DDR1,DDR2,DDR3,DDR4还有DDR5?

DDR1、DDR2、DDR3、DDR4和DDR5都是不同类型的同步动态随机存取存储器,它们提供了不同的性能和带宽,并不断演进和发展。 都是不同类型的内存规格,它们的速度、带宽、工作电压和能耗等方面都有所不同,DDR5 内存规格最高,速度最快,带宽最宽,能耗最低。

SI/PI信号完整性测试

SI/PI信号完整性测试的重要性SI(Signal Integrity)和PI(Power Integrity)信号完整性测试在现代电子设备设计和制造中非常重要。以下是SI PI信号完整性测试的重要性、SI/PI信号完整性测试内容和案例。

LVDS闪屏的原因及解决办法

LVDS(低电压差分信号)闪屏问题通常指的是显示屏在使用过程中出现闪烁或不稳定的现象。本文将为您介绍 LVDS(低电压差分信号)闪屏的原因及解决办法。

HDMI闪屏故障的成因及相应的解决方法

在现代多媒体设备中,HDMI(高清多媒体接口)是连接显示器与电脑、游戏机等设备的主流方式。然而,许多用户在使用HDMI连接时会遇到闪屏现象。本文Misenbo将探讨该问题的成因及相应的解决方法,帮助用户快速排查和修复问题。

【测试那点事儿】信号的过冲咋处理?-Debug 案例1

信号过冲(Overshoot)是指在数字信号传输过程中,信号幅度暂时超过其稳态值的现象。这通常发生在信号快速切换时,如从低电平到高电平或从高电平到低电平的过渡期间。

【经验】解析HDMI Sink一致性测试及眼图测试案例

HDMI测试主要有Source端测试、Sink端测试、单项眼图信号质量测试。Source端测试已介绍、接下来淼森波实验室分享HDMI的Sink端一致测试、Sink端眼图文测试。

MIPI接口闪屏怎么解决?

在现代移动设备中,MIPI(移动行业处理器接口)因其高速串行数据传输能力被广泛应用于显示屏和摄像头模块。然而,用户在使用这些设备时可能会遇到闪屏现象,即图像频繁闪烁或不稳定。本文将深入探讨MIPI接口闪屏的成因及解决方案。

【应用】淼森波MIPI/LVDS/FPDLINK/GMSL/以太网等多种智能座舱信号完整性测试案例分享

Misenbo森波实验室测试了智能座舱的多种信号的完整性,帮客户解决了许多信号完整性的问题,本文将为大家分享淼森波MIPI/LVDS/FPDLINK/GMSL/ 以太网/DP/USB3.0/USB2.0测试案例。

【经验】SATA物理层一致性测试案例分享

本文中Misenbo将与大家分享SATA物理层一致性测试案例。

DDR3信号速率问题详解

MISENBO实验室探讨了DDR3内存速率不足的问题,指出时序、信号质量、串扰、电源噪声和等长匹配是主要原因。建议使用等长设计、差分信号、优化电源和终端电阻来解决这些问题。实验室提供高速信号测试和硬件研发服务,帮助提升DDR性能。

登录 | 立即注册

提交评论