数据互联为什么在人工智能中占据越来越重要的位置?

随着人工智能的火热,在给人工智能大模型提供足够的算力用于训练和部署的核心芯片技术中,数据互联正在占据越来越重要的位置。

井芯微电子作为以交换互连为核心战略方向的创业公司,正积极参与以软件定义互连为核心的Dielet(芯粒)互连接口标准,预计在2023年底的软件定义晶上系统技术与产业联盟大会上发布团体标准草案。通过软件定义,希望可以在规范上兼容UCIe接口标准,还可实现面向领域的特色定义,确保对先进Dielet互连成果开放性的同时,也探索我国发展软件定义晶上系统的自主之路。

在人工智能技术中,目前看来影响力最大的技术将会是大模型技术,其核心特点就是通过使用规模巨大(参数可达百亿到千亿数量级)的模型,并且在海量的数据上训练,来实现人工智能能力的突破,并且赋能新的应用,其中典型的例子就是去年下半年开始获得万众关注的ChatGPT;而在未来,大模型的复杂度预计会进一步提升,以满足应用的需求。

训练和部署大模型需要强而有力的硬件支持,而这也是人工智能时代芯片成为核心技术的原因,因为大模型需要的算力归根到底来自于芯片,同时人工智能市场的发展也极大地推动了芯片行业的市场规模,以及相关芯片技术的演进。

在给人工智能大模型提供足够的算力用于训练和部署的核心芯片技术中,数据互联正在占据越来越重要的位置。芯片互联越来越重要主要出于两个原因:

首先,随着大模型的参数规模和训练数据容量快速提升,训练和部署最新的大模型一定会使用分布式计算,因为单机几乎不可能提供运行大模型的足够算力。在分布式计算中,随着分布式计算节点数量提升,理想情况下计算能力是随着计算节点数量线性提升,但是现实中由于不同计算节点间的数据交互需要额外的开销,因此只能接近而无法真正实现计算能力随着计算节点增加而线性增加。换句话说,随着模型规模越来越大,需要的分布式节点数量越来越多,对于这类分布式计算节点间的数据互联需求(带宽,延迟,成本等)也就越来越高,否则这类分布式计算中的数据互联将会成为整体计算中的效率瓶颈。

其次,从芯片层面考虑,随着摩尔定律越来越接近物理极限,目前以chiplet(芯片粒)为代表的高级封装技术正在成为芯片性能提升的重要方式。使用chiplet可以把单个复杂的大芯片系统分成多个小的芯片粒,每个芯片粒都可以用最合适的工艺去单独制造,因此确保复杂的芯片系统可以以合理的成本和良率来制造。对于人工智能大模型而言,用于训练和部署的芯片的规模都非常大,因此chiplet将会成为支持人工智能芯片的核心技术。而在chiplet方案中,多个chiplet之间的数据通信也需要数据互联技术,换句话说高带宽、高密度的数据互联将会成为使用chiplet搭建的人工智能加速芯片中的核心组件。

如上所述,在人工智能时代,数据互联将会成为核心技术,而其中最关键同时也是未来将会有最多发展的数据互联方案,就是用于分布式计算中的中长距离数据互联,以及用于chiplet场景中的超短距离数据互联。

用于分布式计算的数据互联:硅光子技术成为关键

人工智能大模型的分布式计算,包括训练和部署,通常都在数据中心中完成。我们在数据中心数据互联中看到两个重要趋势,即常规长距离通信的进一步规模化,以及新的短距离应用的崛起。

在常规的长距离数据中心数据互联领域,目前为了满足人工智能等应用的需求,互联速度正在快速提升,从今天主流的100/200/400Gbps光互联技术快速进展到800Gbps光互联技术,而到2026年更是预期会使用上1.6Tbps光数据互联。除了数据率提升之外,在人工智能时代,数据中心中每台服务器上对于数据互联的需求也在提升,因此单台服务器会需要更多的光数据互联模块。与传统的分立式光互联模块相比,基于硅光技术的光互联模块能实现更高的集成度:在硅光技术中,波导器件、光栅和调制器等核心模块都可以集成在同一块芯片上,从而可以大大降低光互联模块的成本,这对于人工智能应用来说是一个重要优势,因为训练大模型中需要大量的高带宽数据互联同时也不能提高太多成本。

随着对于数据互联带宽的要求进一步提升,数据中心中的光互联带宽也需要进一步提升,功耗则需要进一步降低,而从这个角度,硅光子技术搭配共封装光学(co-packaged optics,CPO)也会成为下一代光互联带宽和功耗优化的核心技术。

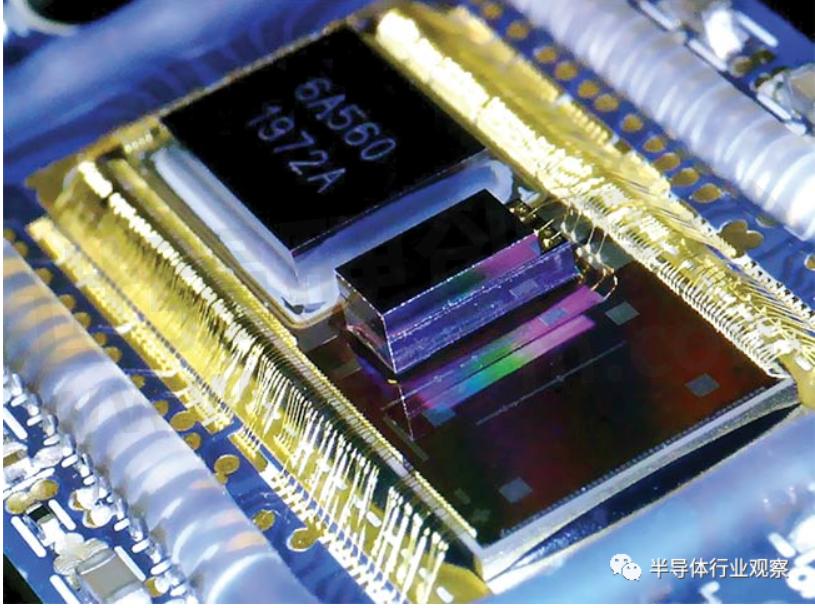

图 1

在共封装光学技术中,使用硅光子技术实现的光互联模块和使用传统CMOS技术实现的数字逻辑(例如光互联模块后接的网络模块)将会使用高级封装技术集成在同一个封装里——而在传统的实现中,光互联模块和其他CMOS芯片并不会集成在同一个封装里。通过使用共封装光学技术,光互联模块和其他芯片之间的互联距离大大缩小,从而减小了光互联模块与电信号接口的信号传输衰减,而这对于超高带宽通信至关重要,因为在这些超高数据率的应用中,真正限制数据率的往往不是光信号,而是光信号在转换成电信号之后的信号衰减(即last-mile问题)。另一方面,通过减小信号衰减,光互联模块的整体功耗可以减小。而共封装光学是基于硅光技术之上的,因为传统的分立式光模块因为体积太大,无法使用共封装光技术和其他芯片集成到同一个封装里。

除了目前已经为人熟知的数据中心中长距离光互联模块之外,在人工智能时代将会崛起的另一个光互联技术将是计算集群中的中短距离光互联。如前所述,在大模型时代,分布式计算将会得到广泛应用,而在具体的大规模分布式计算拓扑结构中,常用的结构就是首先由物理位置相邻的服务器组成一个集群(cluster),在这样的计算集群中执行需要大量数据交换的任务,而计算集群之间再使用长距离数据互联连接在一起以提升计算规模。在这样的计算集群中,目前常规的数据互联是使用铜绞线的互联;但是随着对于数据带宽、延迟和功耗的需求越来越高,使用在计算集群中的光互联正在成为越来越重要的技术路径。

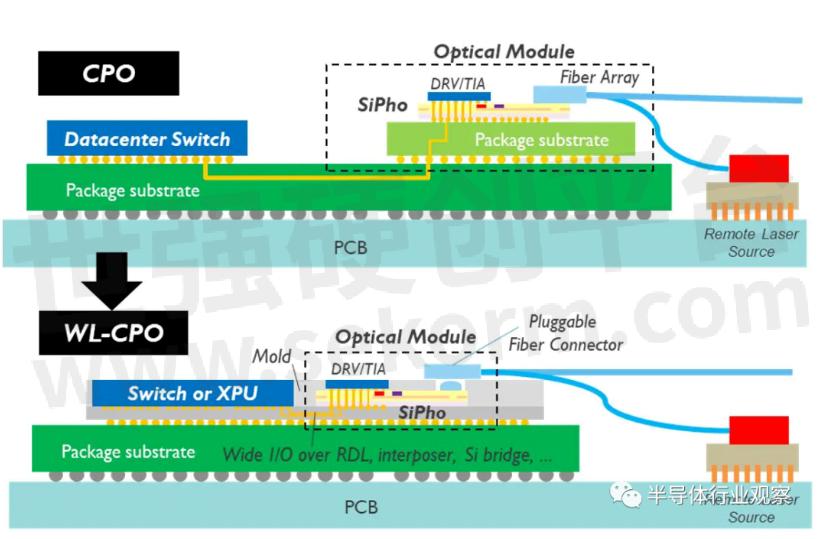

与长距离通信不同,计算集群间的数据互联需要延迟极低、功耗也较低,但是由于互联距离较小(即色散效应较小)因此可以允许更多的波分复用,因此光互联可以考虑多个波分复用信道,每个信道的数据率较小(例如16-64Gbps),这样做可以尽可能减小对于数字矫正技术的依赖(使用数字矫正技术将会提升延迟,同时也增加功耗),以满足对于功耗和延迟的需求。此外,在计算集群中,我们会预期光模块和CMOS芯片(例如GPU或者HBM)更紧密地集成在一起,因此在共封装光学CPO技术之上,我们可能会看到集成度更高的晶圆级共封装光学(WL-CPO)技术,该技术可以为光学互联模块和CMOS芯片之间提供更多互联接口,从而进一步增加通信带宽。

图 2

用于chiplet的超短距离数据互联

除了长距离光互连之外,另一个人工智能时代的重要数据互联技术是用于chiplet之间通信的超短距离数据互联。

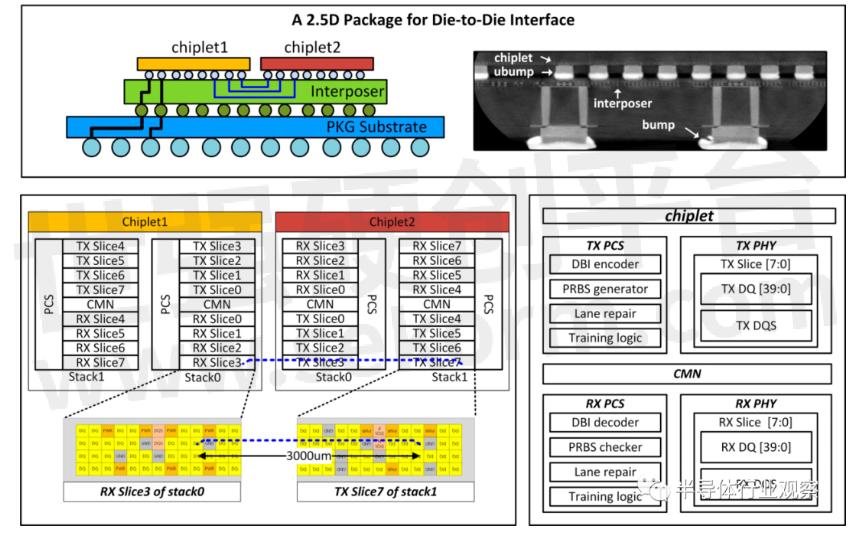

图 3

随着摩尔定律接近物理极限,使用chiplet来实现复杂芯片系统已经是业界共识。在人工智能时代,随着对算力需求的进一步提升,单芯片系统预计会用到越来越多的chiplet,同时chiplet之间的互相通信需求也会越来越大。长距离光通信数据互联的主要演进方向是共封装光学这类的新封装工艺,而与之相对地超短距离chiplet数据互联演进更多是依赖电路设计和系统设计。我们可以看到chiplet对于数据互联需求的两大方向:

1.更高的数据带宽,更长的通信距离(从毫米级别上升到厘米级别),更严格的功耗要求

2.更复杂的通信协议需求

先看第一个方向,这条需求对于chiplet数据互联的电路设计提出了越来越多的需求。随着chiplet数量越来越多,系统越来越复杂,势必chiplet之间的互连距离会越来越长,这也就意味着互联线上的衰减会更大,会需要更强的收发机;另一方面,随着人工智能对于chiplet间数据通信带宽的要求提升,每个chiplet上的数据互联模块数量也会增加,这就意味着单个数据互联模块的功耗不能过大以满足总功耗的限制。另外,随着数据互联需求的快速提升,单个数据互联模块的芯片面积又不能太大,这样才能满足chiplet上总互联接口的需求。因此,chiplet数据互联电路主要有两大指标,一个是能效比(J/bit),用来衡量数据率与功耗之间的关系;另一个指标则是数据率密度(bit/s/mm),用来衡量数据率与芯片面积之间的关系。随着chiplet数据互联需求的提升,未来我们可望会看到越来越高的数据率密度,同时越来越好的能效比。

第二个方向则是通信协议需求,这里涉及了chiplet之间协同工作的方式,例如在处理器系统中,如何确保chiplet之间缓存一致性的问题。未来随着chiplet系统越来越复杂,传输的复杂度也会提升,未来甚至可能会把目前NoC的模式搬到chiplet上。这对于chiplet数据互联IP的设计也是一个新的发展方向。

总体来说,对于chiplet的数据互联来说,随着人工智能相关需求的兴起,未来它可望会成为芯片IP领域一个越来越重要的品类,而具体的技术方向,则会沿着电路设计的优化和系统/传输协议复杂度提升的方向去演进。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由三年不鸣转载自半导体行业观察,原文标题为:互联,成为核心技术,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关研发服务和供应服务

相关推荐

工信部等六部门联合印发《算力基础设施高质量发展行动计划》

工业和信息化部、中央网信办、教育部、国家卫生健康委、中国人民银行、国务院国资委等六部门近日联合印发《算力基础设施高质量发展行动计划》,提出到2025年,计算力方面,算力规模超过300 EFLOPS,智能算力占比达到35%,东西部算力平衡协调发展。运载力方面,国家枢纽节点数据中心集群间基本实现不高于理论时延1.5倍的直连网络传输,重点应用场所光传送网(OTN)覆盖率达到80%。

网络芯片哪家强?原来这个领域要比你想的更复杂!

随着大规模AI训练的兴起,在AIGC迅猛前进的道路上,智能算力作为AI网络的基石,是支持AI大模型训练和推理的关键;高性能超高带宽、超低延迟和超高可靠性的网络则是AI网络基础设施的纽带,推动更高性能的网络互联成为业界重要的探讨方向。

一文读懂 | 2023中国半导体IP行业研究报告

九层之台,起于累土。半导体IP作为半导体产业精细化的结果,其以可复用的模式形成风险共担、利益共享的生态圈,使得用户能专注自身优势价值的创新性,令低成本创新成为可能。近年来半导体国产化的迫切性已是老生常谈,而半导体IP作为半导体产业链上游的关键一环,其自主可控的重要性更是不言自明。本文将介绍中国半导体IP行业发展概况、剖析细分领域特点、推断未来趋势。

【产品】井芯微国内首款基于RapidIO GEN2协议开发、国产自主研发的NRS1800交换芯片解决方案

NRS1800 是符合RapidlO第二代规范的交换芯片,提供了240Gbps的无阻塞交换能力,最多支持18个端口和48路通道。基于NRS1800的RapidlO互连交换方案,适用于板内芯片到芯片互连、板间互连以及机柜间互连等应用。

【经验】PCIe能不能使用光纤连接?

PCIe在高速交换机领域也有很广泛的应用。交换机的软件通常运行在CPU芯片上,硬件运行在交换芯片或者FPGA上。上位机软件通过PCIe总线配置交换机的相关寄存器,也可以配置交换机的上行或者下行DMA读写操作,并进行CPU与交换芯片的数据交互,非常灵活。软件定义互联交换芯片SDI3210,就是采用PCIe(Gen2 x1)作为芯片的配置、维护、管理的主要通路,同时也是协议数据的传输通道。

【IC】井芯微SDI3210交换芯片,支持端口之间的无阻塞交换,最大交换带宽为320Gbps

SDI3210是一款可软件定义接口协议的交换芯片,每个端口协议类型可以定义为RapidIO协议,FIberiaChanneI(FC)协议,以太网协议,最大支持32个高速通道,支持异构协议的互连互通,支持端口之间的无阻塞交换,最大交换带宽为320Gbps,SDI3210可与以上三种协议的端点设备及交换设备对接。

【经验】RapidIO交换芯片NRS1800国产化替换及兼容性设计方案介绍

NRS1800芯片是井芯微推出的国内首款基于RapidIO Gen2协议开发、自主可控;与某公司的CPS1848芯片管脚兼容且功能相同,可用于原位替代(Pin to Pin)CPS1848。本文我们就具体差异给出说明,并提供相应的参考设计方案。

RapidlO系统可靠性增强解决方案:NRS1800交换芯片支持客制化事件检测,可选择多种上报方式

井芯微电子交换芯片NRS1800支持用户按应用场景和需求客制化事件检测,可以根据主控系统设计和业务应用综合确定;当检测到事件时,也可选择多种上报方式,包括Port-write、中断和主控定期轮询等借助RapidIO互连技术自身定义的高性能、高可靠传输特性,基于专门的网络管理软件,引入RapidIO的错误检测与业务恢复机制,及时发现错误并进行处理,可以极大提升系统的稳定性和可靠性。

【经验】井芯微RapidlO交换芯片NRS1800芯片百问百答——调试篇

为了快速了解和使用1800芯片,井芯微电子通过整理和工程师们现场问题的收集,现推出《NRS1800芯片百问百答》。《NRS1800芯片百问百答》包含了性能篇、工具篇、应用篇、设计篇、调试篇五大分类的100条常见问题解答,涵盖了从产品选型到应用落地的全流程问题覆盖。即可作为您快速了解产品的参考手册,也可作为遇到问题时的现场查询工具使用。本文介绍调试篇常见问题及解答。

【产品】井芯微电子PRB0400型PCIe转SRIO桥接芯片,用于满足高可靠低延时计算处理系统内部各组件之间的互连需求

2022年10月,在经过一年半的攻坚克难之后,井芯微电子技术(天津)有限公司继发布240G网络DPU芯片SDI2820后,再度向市场推出国产替代新产品—— PRB0400型PCIe转SRIO (Serial RapidIO) 桥接芯片。

【经验】UVM学习笔记——TLM 1.0通信技术应用指南

本文对UVM中常用的端口类型做了介绍,并着重介绍了使用FIFO通信。好的验证平台是成功流片的坚实保障。其实,UVM中的端口应用和通信方式远不止这些,每种方法都有其利弊。在实际的验证工作中,能熟练的应用一种方法,并在不同的情况下灵活运用其他方法才是搭建一个可靠验证平台的关键。井芯微电子有丰富的设计和验证经验,至今已有多项科研成果已成功转化,在未来的通信基础设施的“芯”变革中迈出了坚实的一步。

【经验】井芯微RapidIO交换芯片NRS1800外围应用电路硬件设计PCB Layout参考

RapidIO是世界公认的嵌入式系统互连的最佳选择之一,具有超低延迟、高带宽、高可靠、支持任意网络拓扑架构、QoS、支持多播等特性。井芯微推出的NRS1800是符合RapidIO第二代规范的交换芯片,提供了240Gbps的无阻塞交换能力,最多可支持18个端口和48路通道 。本文介绍NRS1800外围应用电路硬件设计PCB Layout参考及检查标准。

电子商城

现货市场

服务

根据用户的蓝牙模块,使用Bluetooth 蓝牙测试装置MT8852B,测试蓝牙1.0至5.1,包括传输速率、功率、频率、调制和接收机灵敏度,生成测试报告。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

根据用户的接口模块,使用是德示波器及夹具查看实时眼图演示,测试USB/MIPI/DDR/SATA/HDMI协议,支持最高到1.2GHz的实时眼图协议测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论