How to Build Together a Safe and Efficient AD & ADAS Central Computing Solution

Autonomous & even partially automated driving face many more challenges than what was anticipated at times, this is not breaking news or new. Today, there are still many obstacles between a fully working prototype and a ready-to-ship solution for the mass market: road infrastructure, reliability, safety, acceptance, human behavior, legislation…

That said, progress is constantly made, sometimes with breakthroughs, while other times with small incremental improvements as attested today with the multitude of fully automated ride-sharing fleets and shuttles operating in dozens of cities as well as the increasing number of car models equipped with L2+ & L3 automated driving assistance systems.

How to accelerate that progress? History shows that collaboration & cross-fertilization of ideas fuels inventions, discoveries, and innovation.

Let's then explore a couple of implementation challenges engineers are facing and how collaborating together would help:

Properly detect and sense the surroundings:

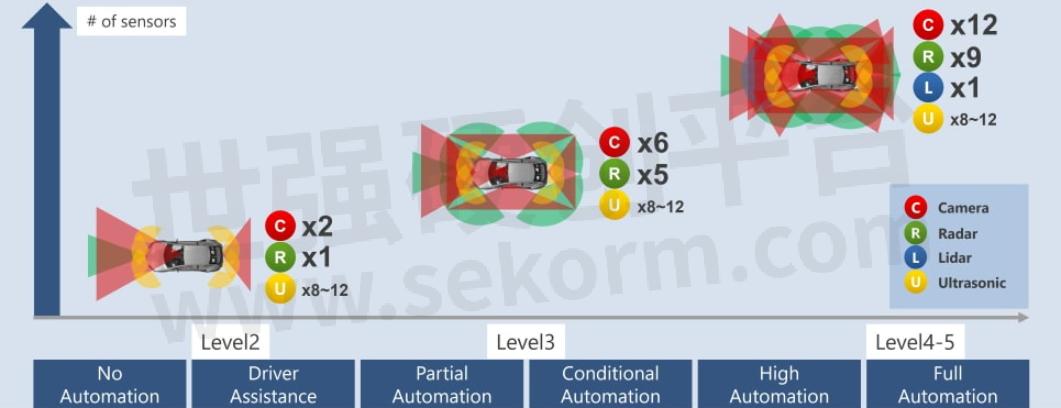

Using multiple sensors helps in mitigating risks like missing to detect or wrongfully identifying an object. Even better: combining sensors with different technologies can also compensate for weaknesses during certain operating conditions: low light, bad weather, obstructed sensors, etc.

Such an approach makes sense and more than one ADAS technology pioneer reverted back from dependence on a single sensor technology to today integrating different sensor technologies (i.e. video camera & radar, video camera & lidar, etc.). But addressing a challenge creates another: an issue impacting simultaneously two of these sensors is a “common fault”, basically their processing has to be independent and reliably redundant. How to make sure no “common fault” impacts what was supposed to be a redundant + independent sensor?

Correctly process all that data and make the correct decision:

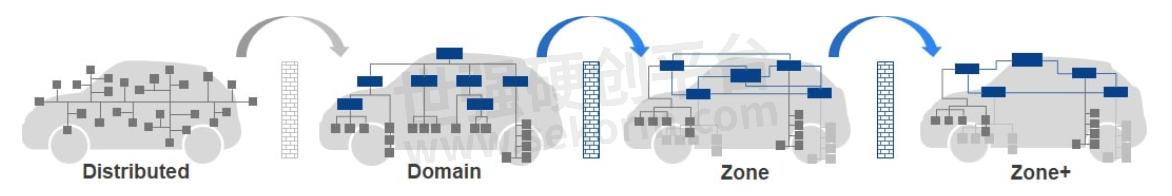

The easiest answer is to simply use different computing systems simultaneously and have enough redundancies. Such an approach works during early development phases with a generous budget, or in specific applications where a fallback is impossible with a relatively low number of produced units like aerospace applications for example. But in a mass-production context, as in automotive, such an approach is obviously counter-productive and even incompatible with the E/E trend of centralized processing:

A similar challenge is faced when different software (SW) processing that are meant to be redundant and complementary interfere with one another resulting in system failure or misbehavior (i.e. one SW task corrupting another’s task data stored in memory, a SW task monopolizing a resource needed by another more critical task, etc.).

To tackle these challenges, as well as any potential common fault, freedom from interference mechanisms is needed. But what should not interfere with what? What should be used with what? To answer such questions, one needs to follow closely the implementation and determine these “rules”.

Ok, but how would it be possible to have a system that safeguards these rules and is already available for developers? We could try to anticipate as much as possible, but logically we achieve better by collaborating closely and making sure these constraints we just called “rules” become a requirement for the system from its specification phase.

With its automotive SoC experience spanning multiple generations, RENESAS was able to build on years of collaboration and developed on-chip mechanisms that ensure software tasks with different safety levels operate in parallel on the SoC without interfering with each other, thereby bolstering functional safety for ASIL D control. First presented at the International Solid-State Circuits Conference 2021, they continue to be upgraded R-Car generation after R-Car generation as today with R-Car gen4 and the recently unveiled R-Car gen5.

Operating efficiency:

Unlike when experimenting on a powerful PC, an automotive central computing solution needs to be efficient and operate in harsh conditions for as long as the vehicle is being used: this means for example that it needs to dissipate generated heat successfully without an overcomplicated colling mechanism (life would be much easier if we can afford a data center’s pinpoint climate control in every car), and this directly depends on consuming power as less as possible.

Renesas has a proven track record in providing the most efficient solutions on the market, whether:

in processing: 16 TOPS/Watt (that’s tera operation per second) in worst operating conditions

or in overall chip power consumption: the front camera used in achieving 5* NCAP within less than a handful of Watts, also in worst-case conditions.

But that’s the easy part! Real efficiency is achieved when the chip design considers the use case and how it would be implemented on the chip. Thanks to our open platform & ecosystem, we at Renesas continuously improve, deepen, and sometimes correct our understanding of how AD & ADAS implementation is done thanks to our constant collaboration with leading OEMs, Tier1s, and Tier2s. Why is that helpful? Here are a few examples:

Understanding the use cases allows Renesas to propose the best-suited safety mechanisms instead of simply implementing everything redundantly.

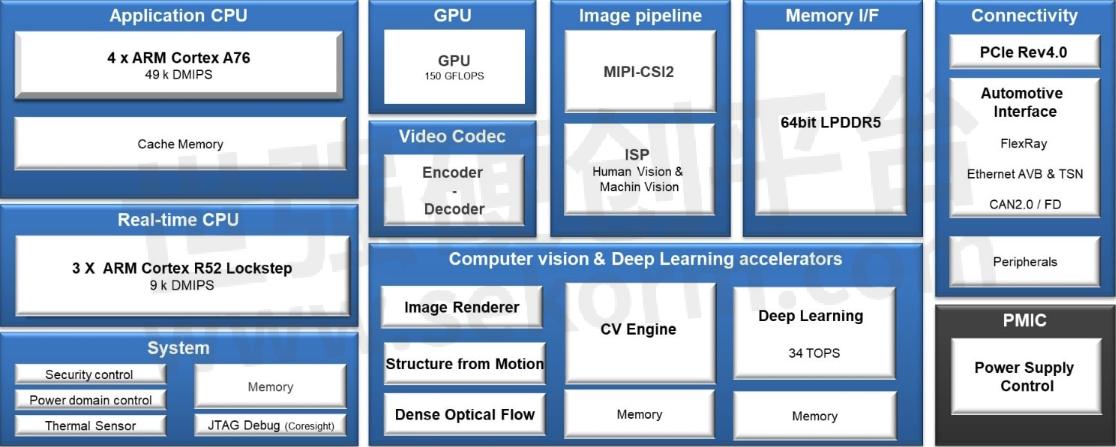

Understanding the different algorithms to be implemented (=used on R-Car) allows us to identify the best-suited processing units in terms of implementation, performance, and efficiency and offer them within R-Car

Further, identifying and distinguishing the commonly used algorithms & functions allows us to develop hard-wired processing units that are uniquely addressed to them, this provides the best performance + efficiency for functions constantly used and frees the general-purpose CPUs for other tasks. Video IPs in R-Car V3H and V4H are an embodiment of that.

Looking from a different angle, such deep dives allow also to quantify the potential usage, this allows us to estimate the data bandwidth required and properly dimension the communication buses, internal memories, compression mechanisms & external memory interfaces: there are a lot of chips out there which boast good processing power but that are choked with a bottleneck here and there.

Collaboration cannot work in a one-way direction: that’s why the feedback from Renesas on these algorithms could be very useful for R-Car users, here are some examples:

Understand which processing unit(s) is(are) best suited for a given case.

Point out where a different approach or change in implementation can be very advantageous and where there could be a potential tradeoff. A recurring example is switching some processing from floating point to integers: in a prototype, this might not seem important but optimizing implementation where precision loss is small or manageable could result in a much simpler, smaller, cheaper solution and a handful of Watts saved.

Introducing new solutions or ideas, like “free” operations that could be made thanks to available functionalities in the system while the data is “available there & now”. This improves unloads data bandwidth because otherwise, these operations could require to later go fetch the same data again.

Progress does not only introduce challenges! RENESAS collaboration can today start much earlier thanks to Renesas’ virtual software development environment: R-Car users can now start designing and testing SW earlier than before which could only start once silicon was available. Their feedback & Renesas’ guidance discussed above now start from day 1.

Should RENESAS stop here and call it a success? Clearly no! Progress has no limits and by working together we ensure to constantly update our understanding of how autonomous systems of tomorrow will be and anticipate that by providing state-of-the-art processing solutions that would bring them successfully to the mass market.

- |

- +1 赞 0

- 收藏

- 评论 0

本文由翊翊所思转载自RENESAS Blogs,原文标题为:How to Build Together a Safe and Efficient AD & ADAS Central Computing Solution,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【技术】传感器融合SoC,ADAS加速迈向高度自动驾驶之路

先进驾驶辅助系统已经广泛地搭载在各类中阶车款上,相信在不久的将来,高度自动驾驶也能实现,不过如何实现自动驾驶这里面可大有玄机。

ROHM Partners with Nanjing SemiDrive Technology Ltd., China’s SoC Manufacturer of Next-Generation Cockpits, to Develop Automotive Solutions

ROHM and SemiDrive have been engaged in technology exchange since 2019, mainly on the development of applications for vehicle cockpits. As the first fruits of this effort, SemiDrive’s automotive SoC (X9 series) solution board equipped with ROHM’s PMIC is now available as a solution.

【产品】瑞萨新一代SOC R-Car V3H,专为自动驾驶前置摄像头应用

瑞萨开发了专门针对前置摄像头应用的SoC——R-Car V3H,集成了专门针对图像处理的功能单元,它比R-Car V3M在视觉处理方面的性能提高了5倍,并只有0.3瓦的超低功耗,更好的适应自动驾驶的需求。

Renesas(瑞萨电子) R-Car M3车载SoC设备概述手册

描述- 本资料概述了Renesas Electronics的R-Car M3系列SoC的初步规格。R-Car M3具备下一代车载导航系统所需的基本功能,包括双核1.5GHz ARM Cortex-A57和四核1.3GHz ARM Cortex-A53核心、LPDDR4内存控制器、多种接口和图形处理单元。资料详细介绍了处理器、内存、显示、视频处理、音频接口、存储和网络等模块的规格和功能。

型号- R-CAR M3

瑞萨公开下一代车用SoC和MCU处理器产品路线图,全新R-Car MCU系列扩展其车辆控制产品阵容

瑞萨电子公开了针对汽车领域所有主要应用的下一代片上系统(SoC)和微控制器(MCU)计划。未来产品阵容包括采用先进小芯片封装(Chiplet)集成技术的R-Car SoC和基于Arm®核的车用MCU。

【选型】车联网V2X车载端产品(V-BOX)推荐:车规级SoC RCAR M3,7核主频1.8ghz、运力30DMIPS

3GPP给出了相关的应用场景,车联网(V2X)分:V2N/V2I/V2P/V2V这几种应用。那么在硬件设计上,现阶段主要是V2X的车载OBU产品和路测的RSU产品。笔者当下接到的项目则是整合传统T-BOX的OBU产品:V-BOX。整个系统功能融合了TBOX和V2I/V2N/V2V的功能。可以使用瑞萨RCAR M2 SoC,内部集成2核A57和4核A53,还有实时内部R7。

【产品】全新开放式平台,加大对ADAS及自动驾驶的支持

新型R-Car V3M SoC符合ISO26262功能安全标准,为视觉处理提供了低功耗硬件加速功能,还配有内置图像信号处理器。

【经验】SoC R CAR V3H2 cnn模型转换后执行以及benchmark过程实操指南

RENESAS SoC R CAR V3H2 cnn模型转换后的输出文件有bcl和.pb 2类,都是可以在端侧执行的,本文记录.pb的推理输出以及benchmark过程实操及解析。

【应用】支持EtherCAT协议的瑞萨单芯片SoC用于伺服系统,实现实时响应,降低20%成本

在伺服系统的应用上,对于主控SoC的选择非常重要,Renesas SoC RZ/T1系列的R7S910025可以实现联网实时响应,采用ARM Coretex-R4F高实时性内核,自带FPU浮点运算单元,最高支持600MHz主频,达到962MIPS的运行速度。

【经验】瑞萨RZ/T1 SoC芯片最小系统关于应用ΔΣ的IGBT波动干扰解决

很多客户使用了瑞萨RZ/T1的ΔΣ delta sigma,反馈IGBT波动有干扰。电源的干扰有可能对芯片的工作有影响,因为没有符合电源规范。变频的是MCU,电源可以+-20%呢,而rzt1是要求5%。 CPU没有出现异常,也可能是因为主频是450M,离600M还有很大的余量。本文介绍解决办法。

【经验】SoC R CAR V3H2 CNN工具链转换restnet18 caffe模型为端侧可执行命令过程解析

RENESAS SoC R CAR V3H2 CNN工具链最主要的功能就是把caffe,onnx等模型转换为V3H2 芯片端可执行模型,命令,本文记录并分析此转换过程。

Renesa Introduced Its Next Generation ASIL-D SoC and New Automotive-Qualified Position Sensor

Renesas participated in this year‘s digital Embedded World, which took place from 1-5 March and had demonstrations in ADAS, EV, Vehicle Computer, SoC, MCU, Analog and Power, covering the full range of the latest in Renesas Automotive solutions.

【经验】解决瑞萨RZ/T1 SoC芯片最小系统硬驱IIC断点死循环问题

客户反应问题:设置瑞萨RZ/T1高性能SoC芯片最小系统硬驱IIC断点,执行不下去,进入while死循环。本文介绍如何解决该问题。

【经验】如何实现SoC R CAR S4从网络启动配置操作?

R CAR S4的DEMO板上emmc中的内核以及文件系统烧录,需要先从网络启动系统后,然后通过挂载emmc,才能把内核以及文件系统copy到emmc分区中,本文记录spider board的配置烧录过程。

【产品】采用业界先进16nm制程,算力高至7TOPS的自动驾驶R-Car SoC,ADAS解决方案 | 视频

在2021年5年28日汽车电子专场|世强硬创新产品研讨会中,瑞萨ADAS技术专家Cross为我们我们做了演讲,视频介绍了R-Car V3X系列ADAS技术方案,重点讲解了R-Car V3M,V3H1.1,V3H2.0的技术指标规格。

电子商城

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥8.1764

现货: 102,628

品牌:SILICON LABS

品类:Mighty Gecko Multi-Protocol Wireless SoC

价格:¥27.0929

现货: 90,767

品牌:SILICON LABS

品类:Wireless Gecko SoC

价格:¥10.4994

现货: 50,699

现货市场

登录 | 立即注册

提交评论