“摩尔定律”的过去、现在和未来

尽管由于经济、技术和物理因素,摩尔定律的局限性被一再强调,但摩尔定律仍然持续存在。

摩尔定律是半个多世纪以来驱动半导体行业发展的经验法则。半导体由于符合摩尔定律的更高集成度和更低成本(安装在集成电路中的每个晶体管的成本更低)而取得了显著的进步,配备半导体的电子设备以及它们的应用变得越来越流行,已经发生了显著的变化。摩尔定律已成为半导体制造设备、材料、器件、电子设备制造商和服务提供商等行业的“绝对基础” 。

尽管由于经济、技术和物理因素,摩尔定律的局限性被一再强调,但摩尔定律仍然持续存在。最近,人们一直在说“摩尔定律终结了吗?”随着被称为极紫外光刻技术的EUV光刻技术投入实际应用,摩尔定律的寿命也进一步延长。尽管如此,原子仍无法变得更小,因此二维微型化最终将达到其极限,但一些集成电路继续通过三维化来增加其密度。未来,3D技术将达到其极限,就像摩天大楼一样。

了解摩尔定律的原始来源

首先,让我们通过查看原始资料来了解什么是摩尔定律。

1965年,戈登·摩尔,英特尔的创始人,时任仙童半导体公司的研发总监,在《电子》杂志三十周年纪念日上,针对“预测未来会发生什么”的邀请,回应了“让集成电路填满更多的元件”这篇短文,他写道,“集成电路的元件数量大约每年涨一倍,并将持续增长下去,至少十年的时间,到1975年,在一个四分之一平方英寸的半导体中将可能包含多达65,000个元件”。

摩尔先生在本文中附上了两张图表,试图说明即将发布的集成电路是一种很有前景的电子器件,未来其元件数量将急剧增加。

图 1 来源:英特尔

集成度每年持续翻倍

集成电路的复杂性,即最大限度地降低集成电路中每个元件的制造成本,每年以大约两倍的速度增加。在短期内,这种增长率不会增加。长期来看 ,虽然增长率有些不确定,但至少在未来10年里很可能保持大致恒定。到1975年,他预测使用晶圆可以生产的集成电路的最低成本数量将达到65,000 个元件。

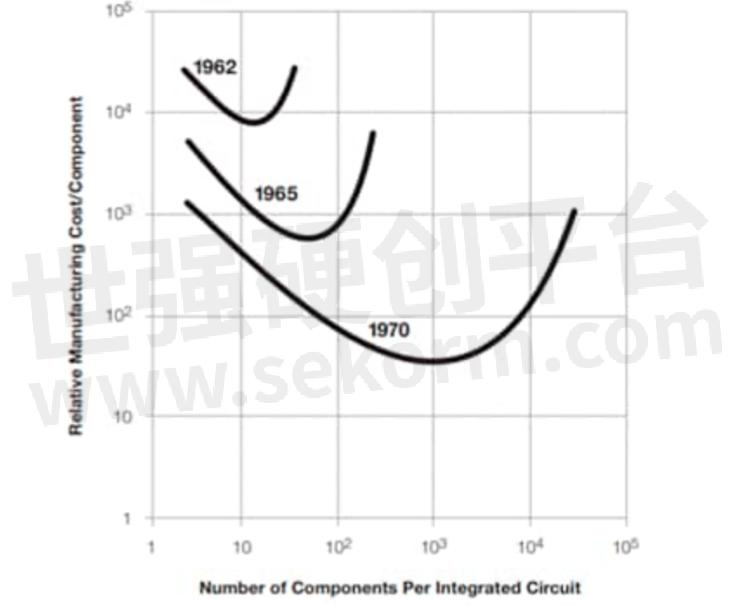

图 2 每年安装在集成电路中的电子元件的每个制造成本(纵轴:相对值)与安装在集成电路中的电子元件的数量(横轴)之间的关系的双对数图。来源:英特尔。

摩尔预测,集成电路中有一个最佳的元件数量,可以最大限度地降低每个电子元件的制造成本,并且随着技术的进步,这个数字将每年增加。封装过多的电子元件并提高集成度会增加缺陷数量,降低制造良率(良品率)并增加每个电子元件的成本。相反,如果电子元件的数量太少,单位成本就会增加。他最想说的是,集成电路上的元件数量会随着技术的进步,也就是随着时间的推移而迅速增加,从而最大限度地降低集成电路的制造成本。

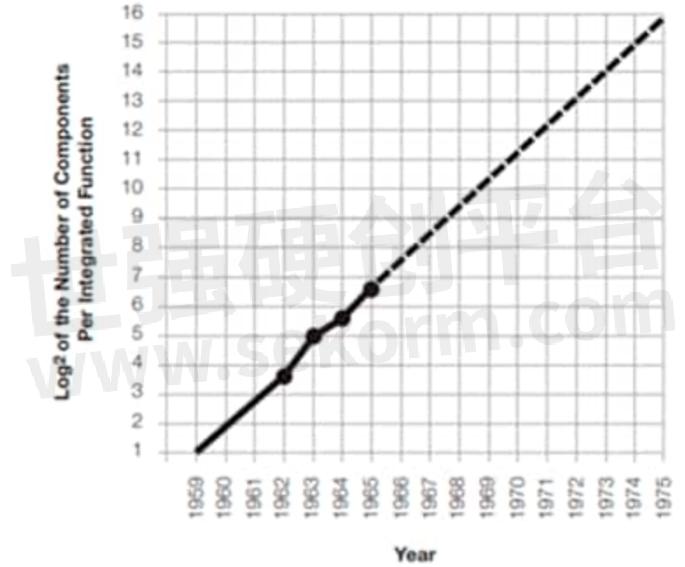

图 3 每年安装在集成电路中的电子元件数量(虚线为预测值)。来源:英特尔

上图是著名的半对数图,它是提出“摩尔定律”的基础。摩尔绘制了Fairchild Semiconductor于1965 年制造和发布的四种IC中的元件数量。两者都是配备了图3中描述的最少数量电子元件的商用集成电路。

摩尔先生大胆地将仅用四个点得到的半对数图的直线推算到10年后的1975年。这条直线意味着集成电路中安装的元件数量每年都会增加一倍。这是后来被称为“摩尔定律”的经验法则。这没有任何理论依据,只是集成电路问世以来短短三年内根据经验做出的预测。

关于未来,他为何做出如此大胆的预测?

当时,分立晶体管还处于鼎盛时期,任何电子电路都可以只用分立晶体管来构建,而不需要使用昂贵的集成电路,因此出现了一种普遍的趋势,即消费者不需要使用高成本的集成电路。电路仅用于有限数量的应用,例如军事应用,在这些应用中成本不是问题。

在文章的最后,他扩展了他的预测,指出随着集成度的提高,每个电子元件的成本下降,电子设备的成本将大幅下降,并且“它们将在整个社会中变得无处不在。”他还引用了具体的集成电路应用,例如“家用计算机,或者至少是连接到中央计算机的终端、汽车自动控制以及个人移动通信设备”。

1975年底,即写完这篇文章10年后,摩尔重新审视了过去10年集成电路集成密度的趋势,并得出结论:“从现在开始,半导体的密度将每两年翻一番。” 此后,大家把这个预测称为“摩尔定律”,它不仅成为半导体行业的绝对参考,也成为电子行业的绝对参考。这个法则通常被称为“半导体的密度每18到24 个月(1.5到2年)就会翻一番” 。这可能与英特尔的MPU性能相混淆,英特尔的 MPU 性能在18 个月内翻了一番。

摩尔定律已存在50多年

2015 年,摩尔定律迎来了50周年纪念。在过去的50年里,半导体在符合摩尔定律的小型化、更高集成度和更低成本方面取得了显著的进步。正如摩尔所预言的那样,利用半导体的电子设备使生活变得更加舒适和高效。

摩尔定律提出时,集成度被定义为所有电子元件的零件数量,包括安装在集成电路上的电阻器,但随着集成度的提高,晶体管占据了电子元件的大部分。最初的40年左右,集成电路的集成度是通过MOS晶体管的栅极宽度和电路线宽的小型化来提高的。随着小型化变得越来越困难,人们反复说“摩尔定律已经失败”和“摩尔定律已经结束” 。

以下是晶体管结构和材料变化的一些例子,这些变化延长了摩尔定律的寿命。自集成电路发明以来一直使用的平面结构被FinFET结构取代,抑制了源极和漏极之间的漏电流并提高了电流驱动能力。绝缘膜/栅极材料也从传统的SiO2/SiN(氮化硅绝缘膜)/poly Si(多晶硅)栅极改为High-k(高介电常数绝缘膜)/金属栅极,抑制了栅极漏电流。

传统的布线材料Al已被具有高导电率的Cu所取代,未来还将使用Co和Ru 。光刻作为微细加工技术的基石,通过缩短所用光源的波长来提高其分辨率:G线(436nm)→ I线(365nm)→ KrF(248nm)→ ArF(193nm ) 。此外,随着ArF浸没式光刻技术的引入,分辨率也得到了提高,该光刻技术使用ArF准分子激光器作为光源,并使用水作为透镜和晶圆之间的浸没液体。后来,原本被认为不可能实现的EUV(极紫外,3.5nm)光刻变得实用,为7nm以上逻辑器件小型化开辟了道路,摩尔定律也成了现实。

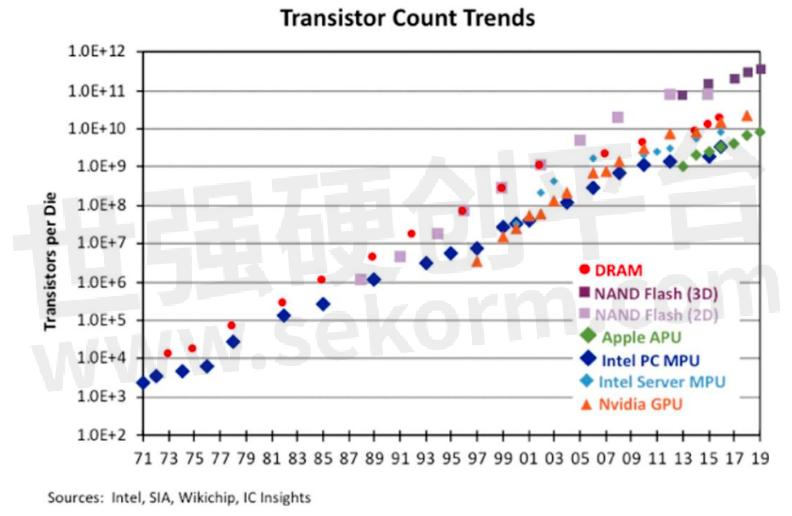

我们来看看过去50年半导体器件是如何按照摩尔定律增加晶体管数量的。根据美国半导体市场研究公司IC Insights的调查显示,虽然某些产品类别的增长速度有所放缓,但正如稍后将解释的, 3D化已经在某些设备中开始。

图 4 半导体芯片上安装的晶体管数量随半导体器件类型的变化。来源:IC Insights

直到2012年左右, NAND闪存容量的年增长率为每年55-60 % ,但此后已下降至每年30%-35 %左右。二维结构的小型化停止在20纳米或略低于该水平,正如稍后将解释的,NAND通过领先于其他设备的三维化而恢复了容量增加的势头,已经从128层增加到300层。

直到2010年,英特尔PC微处理器(MPU )中安装的晶体管数量一直以年均约40%的速度增长。从那时起,这一比例已经减少了一半。尽管英特尔服务器MPU中晶体管数量的增长在2000年代中后期暂时停止,但此后又开始以每年约25%的速度增长。顺便说一句,英特尔在10纳米以上的小型化发展上屡屡受挫,并决定将部分先进CPU的制造外包给台积电。该公司专注于安装技术,通过 3D技术提高集成密度。

苹果公司iPhone和iPad中使用的A系列应用处理器(APU)中的晶体管数量自2013年以上亿个晶体管,在小型化方面处于世界领先地位。

英伟达的高端GPU配备了比其他公司处理器更多的晶体管,已经超过500亿个,并且正在按照摩尔定律增加其密度。根据这一分析结果,IC Insights表示,摩尔定律作为半导体行业的驱动力,其目标是超越技术障碍进行创新,这一点不容低估。

只有三家公司在小型化竞赛中幸存下来

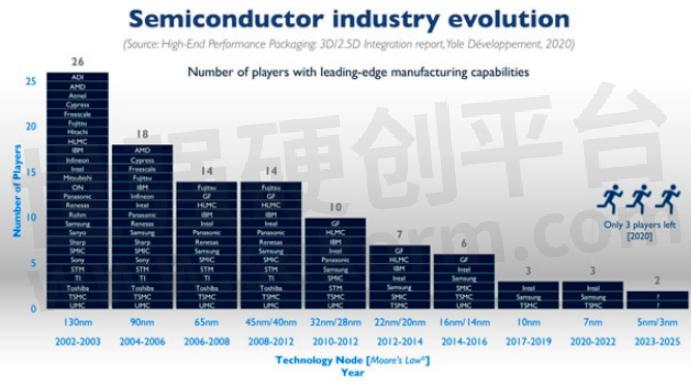

我们从小型化的角度来看看半导体公司的趋势。随着电路图案变得越来越精细,工艺开发成本和资本投资成本飙升,导致许多半导体公司退出小型化竞争。2002/2003年左右,全球有26家半导体公司可以制造130纳米器件,但90纳米器件有18家公司,45纳米器件有14家公司,依此类推,继续竞争中,公司数量逐渐减少,而10nm之后,名单缩小到三家公司:英特尔、三星(韩国)和台积电。大多数日本公司在45/40nm处停止了小型化。

图 5 每一代半导体小型化中幸存下来的公司的变化。来源:Yole Développement

未来晶体管结构将继续从FinFET向Gate-All-Around发展,即沟道区被栅极包围,抑制漏电流并提高栅极的电流驱动能力。沟道部分使用在硅上选择性外延生长的Ge或III-V族化合物,而不是硅或应变硅。

随着高NA EUV和2D材料的出现,摩尔定律将延续至1nm以上

比利时先进半导体研究机构Imec表示,石墨烯和过渡金属二硫化物等二维(2D)材料有望推动摩尔定律在1 nm以后延续。

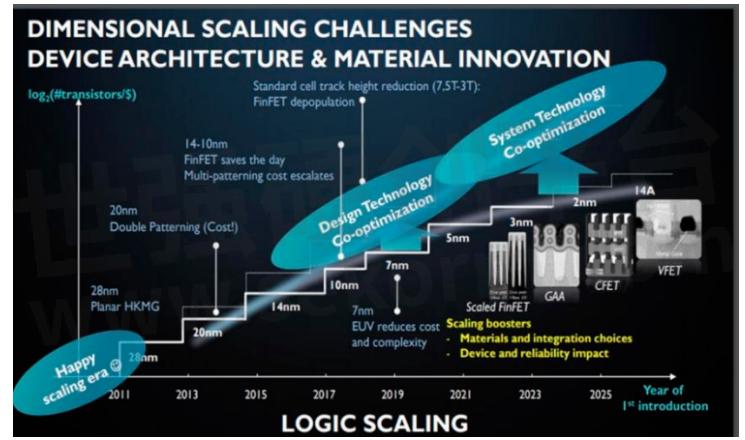

图 6 imec的半导体逻辑器件小型化路线图。来源:imec

纵轴是每美元制造成本的晶体管数量,横轴是年份。直到28纳米左右,仅通过按比例缩小传统结构就可以按照摩尔定律实现集成,但为了在28纳米之后继续扩展摩尔定律,需要同时优化IC设计和工艺技术。甚至有人认为必须开发其他方法以实现技术、IC设计和系统设计的同步优化。Imec和其他半导体制造商正在尝试使用这些同步优化方法来延长摩尔定律的寿命。

然而,一旦我们达到了所谓“原子无法进一步缩小”的阶段,最终就会达到物理极限。

“摩尔定律2.0”从2D微型化到3D堆叠

很多人将摩尔定律误解为与小型化相关的定律,但它实际上是与集成度相关的定律。当然,小型化提高了单位体积的集成度,因此毫无疑问这是提高集成度的有效方法。摩尔定律并不会仅仅因为平面小型化变得不可能而结束。如果它们在三个维度上堆叠,单位面积的密度将会增加,摩尔定律将持续更长时间。未来,整合程度将纵向提升。有些人将这种通过3D实现的集成度提高称为“摩尔定律2.0 ” 。

在3D实现方面,存储器比逻辑更早进入实用阶段。NAND闪存率先迈向3D 。随着目前量产的20-15nm工艺,所有公司都放弃了小型化,转而转向存储单元的三维堆叠,以提高每芯片面积的位密度。它被称为“ 3D(三维)NAND ” 。

东芝于2007年成为业界第一家提出3D NAND概念的公司。使用从顶部到底部穿透多层薄膜的蚀刻工艺,可以一次性形成多个存储单元。与一次一级形成存储单元的方法相比,可以显著降低成本。

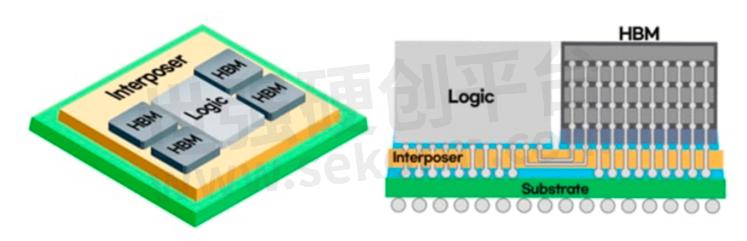

除了闪存之外,各家公司也在研究3D DRAM ,但尚未投入实际应用。相反,三维封装(其中多个已完成的DRAM芯片堆叠并使用硅通孔(TSV)互连)已投入实际应用。多个DRAM芯片和控制器芯片堆叠并通过多个TSV连接的DRAM模块正在实际用于高端网络设备和超级计算机。

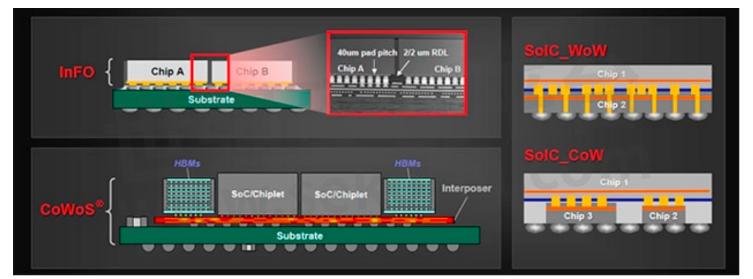

图 7 作为传统“芯片集成”的替代方案,将多个芯片安装在板上的“系统集成”示例。来源:台积电

关于逻辑器件,我们正在从所谓的芯片集成(提高单个芯片内的集成度)转向小芯片(Intel称之为tile ),小芯片是封装基板上按功能划分的多个半导体芯片或传统SoC芯片。系统集成正在成为主流。通过将芯片紧密排列在安装在基板上的硅中介层上来配置系统称为2.5D安装。

图 8 来源:三星电子

在这里,我们将介绍台积电采用的标准系统集成方法,台积电在全球拥有众多的fabless和IDM客户。第一个是InFO 。特点是封装的输入/输出端子面积扩展至硅芯片之外,可以处理超过1000 个输入/输出引脚,并允许多芯片安装。将输入/输出信号从硅芯片的输入/输出焊盘重新定位到封装的输入/输出端子的高密度重新分布层称为重新分布层( RDL ) ,并使用薄膜工艺形成。

第二种CoWoS是在树脂制封装基板上形成多层布线、被称为内插器的中间硅基板,在其上排列多个硅芯片,相互靠近排列。

并且,台积电已经开发出更困难的SoIC(集成芯片系统),它使用芯片堆叠和晶圆堆叠构建系统。SoIC进一步细分为CoW(Chip on Wafer)和WoW(Wafer on Wafer )。SoIC结构允许多个半导体芯片(或晶圆)通过无凸块互连进行堆叠,从而允许信号从一个芯片以最短的距离传输到另一个芯片。

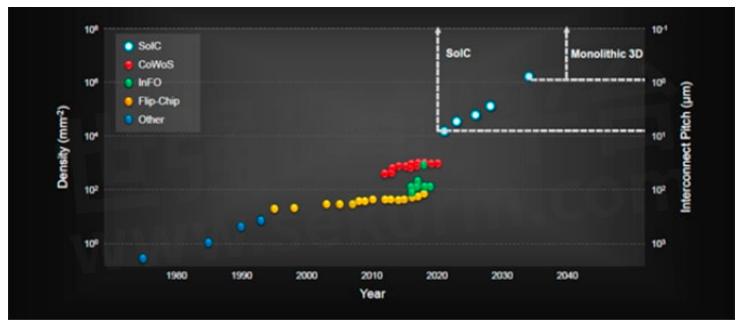

图 9 各种安装技术的器件I/O(输入/输出)密度和互连间距的变化和预测。来源:台积电

如图显示了台积电各种封装技术的器件I/O (输入/输出)密度和互连间距的演变和预测。

文章来源:半导体行业观察

- |

- +1 赞 0

- 收藏

- 评论 0

本文由三年不鸣转载自芯长征科技公众号,原文标题为:“摩尔定律”的过去、现在和未来,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

什么是逆变器,为什么它在新能源汽车产业中如此重要?

逆变器是把直流电(如由电池、蓄电瓶产生)转变成交流电(如220V,50Hz正弦波),且频率可调的一种器件。本文介绍逆变器的原理和应用。

技术探讨 发布时间 : 2024-03-23

GaN的致命弱点

随着世界在半导体领域寻找新的机遇,氮化镓作为未来电源和射频应用的潜在候选者继续脱颖而出。然而,尽管它提供了所有好处,但它仍然面临着重大挑战;没有P型(P-type)产品。为什么GaN被誉为下一个主要半导体材料,为什么缺乏P型GaN器件是一个主要缺点,这对未来的设计意味着什么?本文中芯长征科技就来为大家解析一二。

技术探讨 发布时间 : 2024-03-31

碳化硅单晶衬底的常用检测技术何如保证功率半导体器件的性能?

在半导体产业链中,衬底材料作为晶圆制造的基础,不仅提供物理支撑,还负责导热和导电。特别是在SiC功率半导体器件中,由于采用了同质外延技术,衬底的质量直接影响外延材料的品质,进而决定了功率半导体器件的性能。鉴于SiC衬底在半导体器件制造中的重要性,其质量检测是确保器件性能的关键环节。本文简要介绍下SiC单晶衬底常用的检测技术。

技术探讨 发布时间 : 2024-03-26

国际领先的功率半导体器件标杆品牌——芯长征科技(Marching Power)

芯长征(Marching Power)集团是国内领先的先进功率芯片产业生态公司,创始团队由中科院、国内外行业资深专家及高级管理人才共同组成,在功率器件领域深耕20年以上。经过多年高速发展,已经形成芯片设计、模组封装、检测设备自主可控的Virtual-IDM企业,主要面向新能源(汽车、光伏、储能、电能质量)、工控类、消费类三大领域。

品牌简介 发布时间 : 2023-11-09

芯长征科技IGBT选型表

芯长征科技提供以下参数的IGBT单管、IGBT模块、PIM模块:VCE(V):650~1700;Ic@100℃ max(A):6~950;Vcesat@25℃ typ(V) :1.14~2.89;Eon(mJ):0.129~153.1;Eoff(mJ):0.129~179;Package:TO-247、TO-220、TO-263、TO-220F/TO-220/TO-263、TO-247 plus等多种封装

|

产品型号

|

品类

|

VCE(V)

|

Ic@100℃ max(A)

|

Vcesat@25℃ typ(V)

|

Eon(mJ)

|

Eoff(mJ)

|

Package

|

|

MPBX6N65ESF

|

IGBT单管

|

650

|

6

|

1.4

|

0.129

|

0.129

|

TO-252

|

选型表 - 芯长征科技 立即选型

对2023年半导体销量排名和市值的思考

2023年的半导体市场由于内存不景气,整体以负增长告终。在半导体制造商的销售排名中,英伟达占据了第一位。另一家研究公司Gartner表示,在2023年的速报排名中,英特尔时隔三年重返榜首,而英伟达则从第12名跃升至第5名。不过,考虑到英伟达最近的势头,在排名中,英伟达很可能成为威胁英特尔和三星的存在。本文,芯长征科技想比较半导体销售额排名前十的公司的市值,并讨论每家公司的现状和期望。

行业资讯 发布时间 : 2024-03-30

氮化镓功率器件外延技术的发展

氮化镓(GaN)功率器件的优点包括低寄生电容和特定的导通电阻,从而大大改善了功率转换应用中的关键导通和开关损耗品质因数,以及能够在更高的频率下运行,从而缩小了系统尺寸和成本。在本文中,芯长征科技将总结一些与氮化镓功率器件外延相关的重要专利申请,这些专利申请可能会将这些优势扩展到更广泛的应用领域。

技术探讨 发布时间 : 2024-03-28

igbt芯片、igbt单管、igbt模块、igbt器件等这些的区别是什么?

IGBT(Insulated Gate Bipolar Transistor)是一种高压、高电流功率半导体器件,常被用于大功率应用中,如电动汽车、工业电机驱动、UPS等。在理解IGBT芯片、IGBT单管、IGBT模块和IGBT器件之前,本文中芯长征科技先来介绍一下IGBT的基本工作原理和应用特点。

技术探讨 发布时间 : 2024-03-27

一文解析IGBT的“膝电压“

本文中,芯长征科技来为大家解析IGBT的“膝电压“,希望对各位工程师朋友有所帮助。本文中主要聊了什么是IGBT的膝电压,同时也可以说明另一个小问题,“为什么IGBT的传输特性曲线不是从0V开始,而MOSFET的是从0V开始”。

技术探讨 发布时间 : 2024-03-29

特斯拉的自动驾驶技术优势分析

特斯拉采用全摄像头自动驾驶策略,并拥有数百万辆实车实时收集数据,通过海量数据训练神经网络,使得他们是唯一一个可供消费者购买的可扩展自动驾驶解决方案。特斯拉的FSDBeta技术已经表现出比人类监督更安全的规模优势,且其独特的生产方式和垂直整合带来了巨大的竞争优势。该公司是非常特别的,员工们热情地为了拯救世界而工作,这使得他们能够比其他公司更快地实现目标。

行业资讯 发布时间 : 2024-01-17

碳化硅外延生长炉的技术路线有哪些不同?

碳化硅衬底有诸多缺陷无法直接加工,需要在其上经过外延工艺生长出特定单晶薄膜才能制作芯片晶圆,这层薄膜便是外延层。几乎所有的碳化硅器件均在外延材料上实现,高质量的碳化硅同质外延材料是碳化硅器件研制的基础,外延材料的性能直接决定了碳化硅器件性能的实现。

技术探讨 发布时间 : 2024-03-03

三电平逆变器基本介绍,不同的拓扑对UPS具有不同的影响

对于不同功率等级的UPS而言,选取哪一种拓扑结构同样取决于设计者的指导思想,即若希望提高机器效率,降低损耗,则选取T字型拓扑是比较好的选择;若希望降低开关管应力,采用耐压低的开关管,那么I字型电路是比较好的选择(当然,I字型电路当中会增加两个二极管,这会使得需要更大的空间以及更大的散热器面积,这一点在选择I字型拓扑时应加以权衡)

技术探讨 发布时间 : 2024-03-29

详解IGBT工作原理,看这一篇就够了!

IGBT是变频器的核心部件,自然要分外关注。你可以把IGBT看作BJT和MOS管的融合体,IGBT具有BJT的输入特性和MOS管的输出特性。与BJT或MOS管相比,绝缘栅双极型晶体管IGBT优势在于它提供了比标准双极型晶体管更大的功率增益,以及更高工作电压和更低MOS管输入损耗。

技术探讨 发布时间 : 2024-03-27

碳化硅晶片为什么存在C面和Si面?

SiC是一种Si元素和C元素以1:1比例形成的二元化合物,即百分之五十的硅(Si)和百分之五十的碳(C),其基本结构单元为Si-C四面体。本文就介绍碳化硅晶片为什么存在C面和Si面。

技术探讨 发布时间 : 2024-01-23

一文看懂MOSFET数据表,快速找到核心数据为己所用

我们将试着破解FET数据表,这样的话,读者就能够很轻松地找到和辨别那些对于他们的应用来说,是最常见的数据,而不会被不同的生产商为了使他们的产品看起来更吸引人而玩儿的文字游戏所糊弄。

设计经验 发布时间 : 2024-03-29

登录 | 立即注册

提交评论