如何进行高速信号完整性测试?

一、什么是高速信号完整性:

对于大多数电子产品而言,高速信号完整性关注时钟频率高于100MHz或者上升下降沿时间小于1ns的信号,主要指高速信号在信号传输线上的质量,当信号能按照相应规范要求的时序,电压幅度,抖动,跳变沿斜率等规格到达芯片管脚时,就说信号完整性好。

影响信号完整性的因素是多方面,一般来自四个方面:1.信号本身,如反射,失真;2.周边信号的影响,如串扰;3.电源分配系统PDS的轨道塌陷;4.来自周边其他组件或系统的电磁干扰EMI。

二、高速信号完整性测试的目的:

验证产品设计是否达到信号完整性的要求,如果产品的信号完整性不好,信号发生畸变,信号接收端无法正确接收信号,导致电路无法正常工作。信号完整性测试对产品研发调试很重要,有助于到有的放矢,提高效率。

三、高速信号完整性应用范围:

只要产品中存在高速信号,都有必要做高速信号完整性测试。高速信号完整性量测内容包括:

从信号参数上分类有:

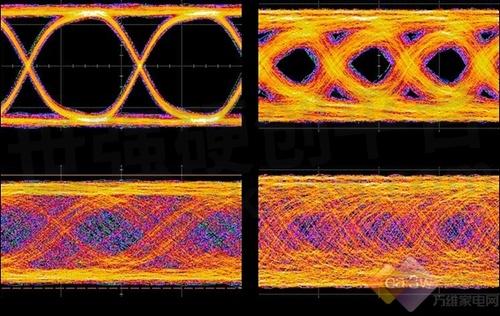

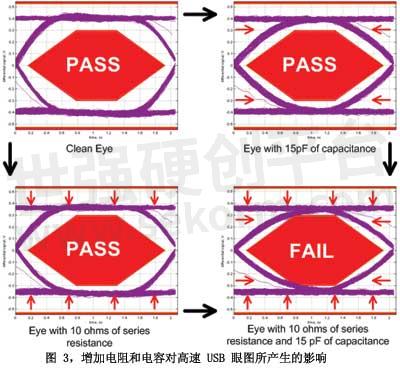

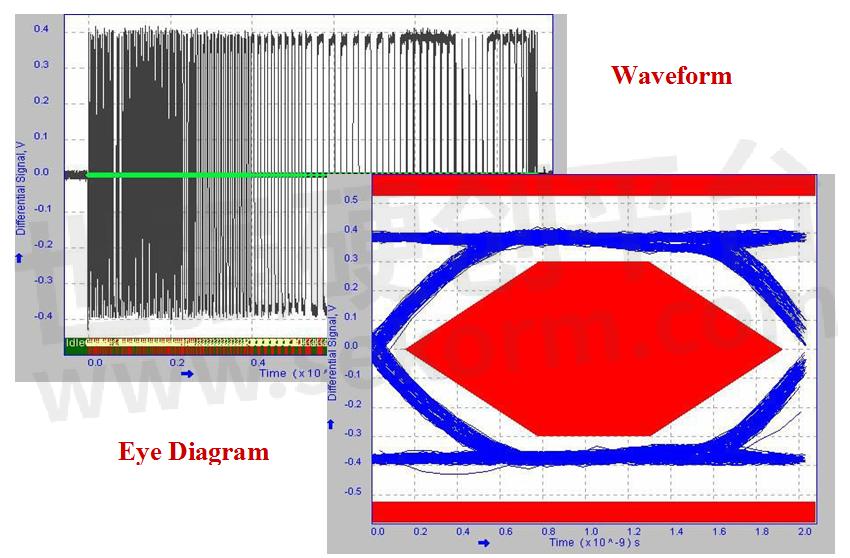

眼图测试,抖动测试,误码率测试等,其中眼图测试是应用最广泛的,在信号速率发展越来越快的今天,几乎所有高速信号都在朝着高速串行总线发展,在高速串行总线中,眼图测试是很基本的测试,几乎所有的高速串行总线都在利用考察眼图来评估信号完整性传输。通过仿真和测量“眼图”来判断信号是否符合产品设计要求。

从信号名称上分类有:

DDR, PCIe,SATA, SAS, USB, HDMI, DisplayPort,DVI, LVDS, V-by-One,SFP, Ethernet。

四、高速信号按照产品的接口分为:

❖ 接口类信号量测

USB (USB2.0 (Host & Device) • USB3.0/ 3.1 • Type A & Type C)接口;

HDMI (HDMI 1.4/ 2.0 Source)接口;

DP (DP1.2/ 1.4 • Source • Type A 接口) 接口;

DVI&VGA。

❖ 传输类信号量测

PCIe ( PCIe2.0/3.0/ 4.0 • X1/ X4/ X8/ X16 • M.2 PCIe • TX & RX)接口;

MIPI (D_PHY)接口;

SATA/SAS(SATA 2.0/ 3.0• SAS 2.0/ 3.0);

ESATA;

TX&RX。

❖ Memory信号量测

SD/EMMC(Embedded Multi Media Card)接口;

DDR(DDR2/ 3/ 4)接口。

高速信号完整性测试常用设备:

高带宽示波器,误码仪,信号发生器等

数字存储示波器

数据定时发生器

更多信号完整性量测,高速信号完整性,详询启威测实验室。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由雪飘梦飞转载自启威测 微信公众号,原文标题为:高速信号完整性测试,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

USB 2.0信号完整性测试常见问题及解决方案

在现代电子产品中非常常见,包括高速(480 Mbps)、全速(12 Mbps)和低速(1.5 Mbps)三种传输模式。针对这些不同的速率,信号完整性(Signal Integrity, SI)是确保数据正确传输的关键。以下是一些在进行USB 2.0信号完整性测试时可能遇到的常见问题及其解决方案。

设计经验 发布时间 : 2024-07-12

如何进行线材高频参数测试?

对于高速线材来说,很重要的一点就是要保证信号传输的完整性,从而避免信号产生大的反射和衰减。线材的高频参数不好对信号的影响很大,可能会导致产品功能不正常,或者完全不工作;为保证信号传输的完整性,需验证Cable的高频参数,从而分析问题原因,更好地定位问题,所以对线材的高频参数测试很有必要。

设计经验 发布时间 : 2024-05-24

【高速信号测试】MIPI-DSI/ MIPI-D PHY 信号完整性如何测试?MIPI-DSI 测试项目及测试案例

进行MIPI-DSI信号完整性测试时,细节和精确性是至关重要的。确保遵循MIPI联盟的标准和指南,以及设备制造商提供的具体要求。本文由启威测实验室小编整理有关MIPI-DSI测试项目、测试设备及软件,测试过程设置、及测试实测案例,方便你快速了解MIPI-DSI信号完整性测试。

设计经验 发布时间 : 2024-10-25

USB 3.2 Gen1&Gen2性能评估及如何进行高速信号完整性测试?

在如今的数据密集型应用中,USB接口的性能显得尤为重要。USB 3.2 Gen1&Gen2作为最新的高速传输标准,为设备提供了更高的传输速率。然而,确保这种高速传输的稳定性和准确性,信号完整性测试成为关键。本文将深入讲解如何对USB 3.2接口进行性能评估,并重点介绍信号完整性测试的具体方法和步骤。

技术探讨 发布时间 : 2024-07-09

史密斯英特康DaVinci 112高速测试插座亮相全球电子成就奖颁奖典礼,荣获年度最佳测试测量奖

近日,全球电子成就奖颁奖典礼晚宴在深圳四季酒店举行。Smiths Interconnect的DaVinci 112高速测试插座凭借优异的商业和产品性能表现荣获年度最佳测试测量奖。该产品设计应用于最大可130x130mm,超过30000个输入/输出且共面性公差高达0.65mm的芯片测试应用,大尺寸芯片在测试过程中会由于共面性差导致无法连接,I/O断开,或出现比较差的信号完整性性能。

原厂动态 发布时间 : 2024-11-13

遇到MIPI-DSI信号测试问题?来看这份故障排除指南

MIPI-DSI是广泛应用于移动设备显示模块的高速串行接口。在研发过程中,确保信号完整性对于提升设备性能和可靠性至关重要。本指南将从研发技术人员的角度出发,为您详细介绍如何在遇到MIPI-DSI信号测试不合格时进行问题诊断和整改。

技术探讨 发布时间 : 2024-07-09

PCI-SIG对PCIe TX眼图的规范要求及其重要性

在高速数据传输中,信号完整性是确保设备性能和稳定性的关键。PCI-SIG为PCI Express(PCIe)接口规定了一系列电气规范,其中之一就是发送端(TX)的眼图要求。眼图是评估高速信号质量的重要工具,通过分析眼图,可以确定信号在传输过程中的失真程度和质量。本文将详细介绍PCI-SIG对PCIe TX眼图的规范要求及其重要性。

技术探讨 发布时间 : 2024-08-22

提升USB 3.2 Gen1&Gen2信号完整性的实战技巧

USB 3.2 Gen1&Gen2已经成为高速传输的主流接口标准,为了确保其信号完整性,工程师需要在设计和实际应用中采取一系列优化措施。本文将分享通过优化设计和实践来提升USB 3.2接口信号完整性的实战技巧,包括PCB设计、布线等方面的建议。

设计经验 发布时间 : 2024-07-12

一文读懂高速信号测试!

随着电子技术的飞速发展,信息交换的速度不断提高,高速信号的频率和复杂度也不断增加,如何准确测试和测量高速信号是确保各类系统正常运行的关键。信号完整性测试包含的内容十分广泛,使用到的测试仪器也多种多样,本文鼎阳科技将介绍几种常见的测试方法来帮助工程师快速定位和解决问题。

技术探讨 发布时间 : 2024-10-17

探讨信号一致性测试与信号完整性测试之间的关系

在高速通信领域,尤其是在使用PCI Express (PCIe) 3.0/4.0/5.0这类先进接口技术的设备与系统中,信号一致性测试和信号完整性测试是保证设备可靠性和互操作性的重要环节。通过本文,我们将深入探讨信号一致性测试与信号完整性测试之间的关系,包括它们的概念、测试内容以及共同点和不同点。

技术探讨 发布时间 : 2024-07-12

PCIe 3.0信号一致性测试与PCIe 3.0信号完整性的关系

在讨论PCI Express(PCIe)3.0接口技术时,信号一致性测试和信号完整性是两个经常被提及的重要概念。虽然它们密切相关,但指向的侧重点有所不同。理解这两个概念之间的关系对于确保PCIe 3.0设备在高速数据传输中的性能和可靠性至关重要。

技术探讨 发布时间 : 2024-07-12

高速信号完整性测试之抖动分析和眼图

优利德MS07000X-JITTER提供了一套针对TIE测量的算法体系, 并包含了文章中提到的所有测量工具,其示波器平台搭载了Windows 10操作系统,并配备15.6英寸电容触摸屏,使算法处理能力及波形展示能力迈上了一个新的台阶。

技术探讨 发布时间 : 2024-09-27

TDR信号完整性测试案例

Misenbo淼森波硬件共享实验室分享TDR信号完整性测试案例。

应用方案 发布时间 : 2024-06-11

PCIe TX/RX 物理层信号完整性测试方法详解

PCI Express (PCIe) 是一种高性能通用I/O互连协议,广泛用于各种计算产品和通信产品。由于时延低、带宽明显要更高,因此业界正在融合到PCIe,作为高速串行总线标准。PCIe在NVM Express SSD应用中尤其流行。

设计经验 发布时间 : 2024-05-28

PCI-SIG对PCIe Link EQ Response测试的规范要求及其重要性

PCI-SIG对PCIe Link EQ Response测试的规范要求是确保高速数据传输质量和系统性能的关键。通过严格控制链路训练、均衡参数和信号完整性,PCI-SIG保障了PCIe设备的高性能和互操作性。希望本文能帮助你更好地理解PCIe Link EQ Response测试的要求及其重要性。

技术探讨 发布时间 : 2024-09-07

服务

深圳市启威测实验室,面向所有企业提供信号完整性测试服务,主要包括USB、HDMI 、DP、MIPI、PCIe 、SD/EMMC、DDR接口信号测试。测试手段有波形测试、眼图测试、抖动测试等。

提交需求>

支持 3Hz ~ 26.5GHz射频信号中心频率测试;9kHz ~ 3GHz频率范围内Wi-SUN、lora、zigbee、ble和Sub-G 灵敏度测量与测试,天线阻抗测量与匹配电路调试服务。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳/苏州 提交需求>

登录 | 立即注册

提交评论