PCIe Retimer TX和RX电气测试

随着PCIe速率越来越高,信号衰减和抖动问题开始突出,为了确保长距离、复杂环境或高数据速率下,PCIe链路仍能保持稳定可靠的通信,出现了PCIe Retimer。那么,对于高速的PCIe Retimer如何进行高效的电气测试呢?PCIe Base协议设计了两个测试状态机:环回测试(Loopback)和一致性测试(Compliance)。接下来,我们一起了解这两种测试状态机。

一、Loopback测试

Loopback主要应用于接收端(RX)能力测试和误码故障隔离测试。对于Loopback测试有很多种类型,本文仅针对BASE规范规定的逻辑层的loopback进行解读。Loopback测试的进入方式主要有两种:

Training结束之后从Recovery状态机进入;

GEN1 Link Up之前从Configuration状态机进入。

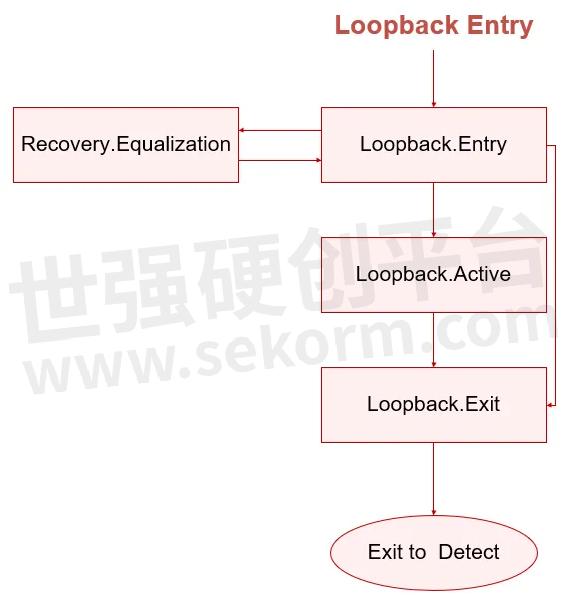

Loopback既可以在单lane上进行,也可以按整link进行。下图是Loopback状态机进入退出示意图:

图1 PCIe Loopback子状态跳转示意图

(图片来源于PCI Express® Base Specification Revision 5.0 Version 1.0)

Retimer loopback协议里有两种描述:Forwarding loopback和Slaveloopback。

在了解loopback组网之前,我们先介绍下两个名词定义:

● Loopback Lead:引导进入Loopback的设备。

● Loopback Follower:环回收到数据的设备。

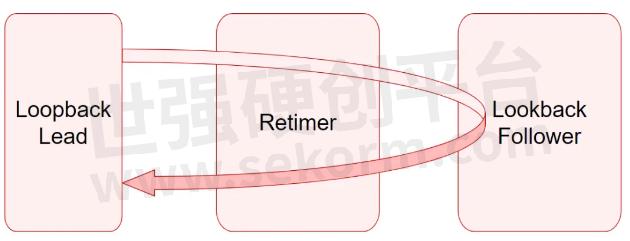

在大多数场景,PCIe Retimer转发收到的数据/码流,Forwarding loopback状态Retimer也属于转发数据/码流状态,该状态用于整个系统链路误码测试分析,分析对象为RC/EP/SW,不在此重点描述。

图2 Retimer进行FWD Loopback组网示意图

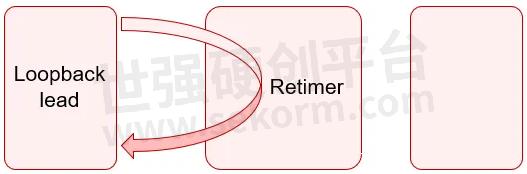

本文主要分析对象为Retimer, 下面我们来看下 Retimer Slave loopback的定义:

根据Intel补充规范定义的寄存器配置 ,Retimer将自身作为Loopback follower执行协议规定的相关握手操作,Retimer将RX LANE收到的数据或者码流环回后用对应TX LANE发出给Loopback lead设备即Slave Loopback。

图3 Retimer进行Slave Loopback组网示意图

Retimer在Slave Loopback下的相关行为主要有如下两种:

01 Recovery状态进入Loopback

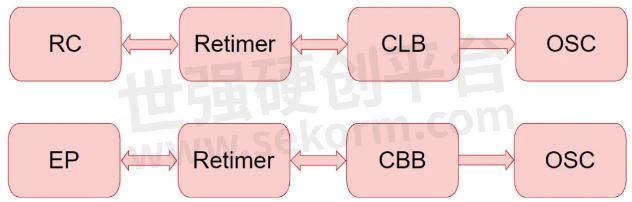

一般电气性能测试RX时通过此方式进入,测试组网如图3所示,通常是误码率测试仪(BERT)+36dB Channel+示波器(OSC)校准误码仪输出,使得BERT TX经过36dB Channel后,到达示波器的眼睛为协议规定的最小压力眼要求。将示波器换成DUT后,BERT和DUT(Design Under Test)进行建链协商,待Gen5 EQ协商完成后进入Gen5 Recovery.Idle,BERT发起Loopback码流,引导DUT进入Slave Loopback模式(Retimer)。

图4 RX测试组网示意图

02 Configuration状态进入Loopback

该场景为协议定义的另一种进入Loopback状态的方式,一般测试不采用此种方式,仅测试规范里会对此场景进行测试。由于Configuration状态进入可能此时链路并没有训练,所以分为以下三种情况。

①声明当前速率进入Loopback:

该场景与Recovery状态进入Loopback行为类似,一般为上电或者Hot Reset之后直接从configuration状态进入Loopback(Gen1)。值得注意的是要避免Training后先进入Recovery状态,在切换Configuration状态进入,因为可能导致Loopback Lead从Configuration状态,Loopback Follower在Recovery状态被引导进入Loopback状态,行为可能会出现错误。

②声明非当前速率进入Loopback

该场景为上电或者Hot Reset之后直接从Configuration状态进入Loopback, 在TS1码流里声明要测试的速率,接着切到指定速率进行Loopback测试。

③声明速率为Gen5且做EQ进入Loopback

该场景为上电或Hot Reset之后直接从Configuration状态进入测试Gen5的Loopback,此时如果Loopback Lead想先做EQ,在Gen1下的Loopback.entry状态下发送的TS1码流会修改ELBC域段。与Retimer正常training状态下的EQ行为不同,此时Retimer的行为与RC/EP的行为类似。需要注意的是,协议规定在做均衡的状态下,任何超时也都会进入到Loopback.entry状态。

二、Compliance测试

Compliance主要应用于发送侧(TX)电气性能测试。Compliance从LTSSM角度只是Polling状态的一个分支,其进入方式分为了三种,

● CLB(Compliance Load Board)CLB组网引导方便,切速简单高效。

● Compliance Receive需要PCIE模拟器或者修改引导设备的寄存器通过码流引导被测设备进入。

● Enter Compliance 修改被测设备寄存器后发起hot reset进入。

对于retimer来说,在CLB模式下会进入执行模式,其他两个方式进入时仍会处于转发状态。为简化Retimer组网引导和切速,一般Retimer TX电气测试用CLB模式引导进入。

01 CLB状态机

一般测试TX的电气性能需要使用CLB/CBB板,本文描述CLB均代表逻辑层的CLB状态机。测试组网示意图如图4所示,Retimer被测TX LANE接到示波器,其余TX LANE用50ohm端接,被测RX LANE 接到按键控制的100MHz时钟上, Retimer进入CLB模式需要RC/EP协助引导。

图5 DUT为Retimer的CLB测试组网示意图

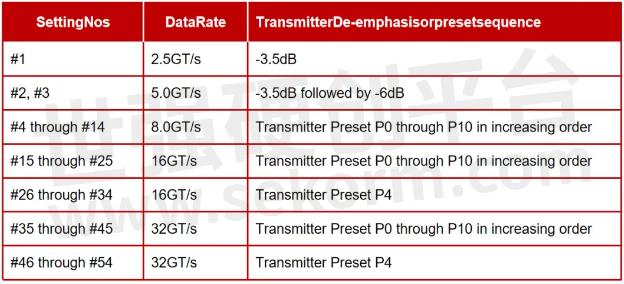

上电之后,Retimer在RC/EP引导下进入CLB模式,并且发送Gen1的Compliance Pattern。按控制时钟按键,会使得Retimer退出CLB模式进入到转发Polling.Active,再由RC/EP引导进入CLB模式,此时Retimer进入的次数变为两次,Retimer发送Pattern切换成Gen2 -3.5dB的Compliance Pattern。Retimer发送Compliance Pattern与进入次数的规则如下表1所示。当切换到第55次时,会重新进入发送Gen1的Compliance Pattern,以此类推。

表1 关于Compliance pattern的设定

(表格来源于PCI Express® Base Specification Revision 5.0 Version 1.0)

注:

● 对于#1到#25,#35到#45:所有的lane都发送Compliance Pattern。

● 对于#26,#46, 所有lane发送Jitter Measurement Pattern。

● 对于#27,#47,lane 0/8发送Jitter Measurement Pattern,其他lane仍发Compliance Pattern。

● 对于#28,#48,lane 1/9发送Jitter Measurement Pattern,其他lane仍发Compliance Pattern。

● 对于#29,#49,lane 2/10发送Jitter Measurement Pattern,其他lane仍发Compliance Pattern。

● 对于#30,#50,lane 3/11发送Jitter Measurement Pattern,其他lane仍发Compliance Pattern。

● 对于#31,#51,lane 4/12发送Jitter Measurement Pattern,其他lane仍发Compliance Pattern。

● 对于#32,#52,lane 5/13发送Jitter Measurement Pattern,其他lane仍发Compliance Pattern。

● 对于#33,#53,lane 6/14发送Jitter Measurement Pattern,其他lane仍发Compliance Pattern。

● 对于#34,#54,lane 7/15发送Jitter Measurement Pattern,其他lane仍发Compliance Pattern。

02 Enter Compliance和Compliance Receive

这两个进入Compliance的方式只会进入指定的速率和并且指定的发送侧系数,并不能像CLB一样去切Pattern,属于逻辑功能测试,一般测试电气特性不会使用这种方式。并且这两种方式并不会引导Retimer进入执行模式,只是单纯转发两侧发送的Compliance Pattern。

环回测试(Loopback)可以在不需要其他设备或网络连接的情况下对设备进行测试。这种简单有效的方法常被用于网络设备、通信设备、服务器、数据存储设备、软件开发、自动化等系统或设备的测试和诊断,提高设备的可靠性和稳定性。

一致性测试(Compliance)可以确保PCIe设备符合PCIe Base规范的标准,从而提高设备与其他设备的兼容性。这对于降低研发和生产成本、确保设备能够在不同供应商的系统中正常运行至关重要。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由walkonair转载自电科星拓 微信公众号,原文标题为:PCIe Retimer TX和RX电气测试,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【经验】电科星拓时钟Buffer芯片TBUF1510在客户服务器上的应用案例详解

本文电科星拓将为您介绍其时钟Buffer芯片TBUF1510的相关规格参数和优势,并详细介绍TBUF1510在大客户的应用经验,帮助大家深入理解时钟Buffer的应用。

PCIe Retimer参与链路训练行为总览

我们将聚焦PCIe Retimer的通信介质角色,和您一起详细了解PCIe Retimer是如何通过参与链路训练行为实现链路状态管理,以提高数据传输稳定性、一致性。

认识PCIe Retimer,如何提高PCIe信号传输距离以及其应用

PCIe Retimer是什么?PCIe Retimer是PCIe规范定义的PCIe专用驱动器,主要作用是补偿链路损耗,以满足PCIe链路的SI(Signal Integrity,信号完整性)需求。

【IC】电科星拓成功量产PCIe 5.0 Retimer芯片,为服务器、存储设备等提供PCIe互联解决方案

电科星拓已成功量产PCIe 5.0 Retimer芯片,具备超低延时、强大损耗补偿能力,支持数字原图,并配备易用GUI量化分析工具,有效延长高速信号传输距离,保障信号完整性,完美适配32Gbps的PCIe 5.0应用。

电科星拓Retimer芯片XRET5032兼容PCIe 1.0至5.0,支持x16通道,是服务器和AI加速卡的理想选择

XRET5032以其高性能、低功耗和卓越的信号完整性,成为服务器和AI加速卡应用的理想选择。它不仅能够提升系统的性能,还能降低能耗,为数据中心和高性能计算提供可靠的支持。

电科星拓PCIe 5.0 Retimer系列芯片XRET5032/XRET5016应用案例

Retimer的应用范围将会更加广泛,为更多领域的高速数据传输提供强有力的支持。无论是通用服务器AIC卡,还是高性能计算GPU,Retimer都将是连接未来技术的重要桥梁。电科星拓凭借在高速互联芯片领域的过硬技术实力和应用经验积累,推出PCIe 5.0 Retimer系列芯片——XRET5032/XRET5016。

【技术】I2C上拉电阻详细设计指南与案例分析介绍

本文重点对I2C上拉电阻的应用进行详细介绍与案例分析。I2C碰到的各种问题,多半是上拉电阻或者控制器时钟的问题。没上拉电阻或者上拉电阻过大,都会导致不稳定而出现寻址不到的问题。本质上来讲,I2C总线电容决定上拉电阻的最大值,I2C器件open-drain接口导通电阻决定上拉电阻的最小值。

浅谈USB协议(一)

USB(通用串行总线)协议是现代电子设备中最广泛使用的接口标准之一。为了满足了市场对高性能接口转换的需求,电科星拓推出XUSB系列PCIe转USB桥片。本文电科星拓将详细探讨USB协议的基本原理,旨在为读者提供深入了解和技术参考。

【技术】解析时钟Buffer芯片及关键参数

时钟芯片是高性能通讯系统中必不可少的核心芯片,其性能及可靠性直接影响着通讯系统的主要性能和系统稳定性。本文中电科星拓将为大家详细讲解下时钟Buffer的分类和关键参数等。

电科星拓发布PCIE转USB产品,将PCIe2.0通道转换为USB3.0接口,广泛应用于服务器、个人PC及工业设备等产品

电科星拓自主研发的PCIe转USB芯片(XUSB系列)已成功实现规模化量产。该系列芯片是一种用于将PCIe2.0通道转换为USB3.0接口的芯片,实现PCIe设备与USB3.0设备之间的数据传输。最多支持1x 5Gb/s PCIe2.0通道、4x5Gb/s USB3.0接口,USB可以协商支持480Mb/s、12Mb/s和1.5Mb/s,芯片支持从外部flash、系统BIOS或者系统软件加载固件。

电科星拓推出I²C双向转换开关芯片INTL9548/46/45,支持0至400kHz总线频率

INTL9548/9546/9545是带复位功能的8通道/4通道I²C和SMBus转换开关,INTL9545同时支持中断功能,支持低电平有效复位(RESET)输入,将RESET下拉为低电平会使I²C状态机复位,并且使所有通道取消选中,这一功能与内部上电复位功能的作用一样。

深入探讨RCD的发展与应用

本期,电科星拓将重点对DDR5技术的重要应用领域之一——RCD,探究和交流RCD的发展与应用。

成都电科星拓科技有限公司(Silicon Innovation)成立于2019年12月,总部位于成都,在深圳、北京、上海、杭州设有研发中心,是一家业界领先的互联芯片解决方案提供商。

【IC】电科星拓I2C热插拔缓冲芯片INTL9511,支持I2C总线标准模式和快速模式双向数据传输

INTL9511是一款I2C总线热插拔缓冲器,支持将I/O卡插入带电背板中,而不会损坏数据和破坏时钟线路。目前,电科星拓已量产了多款I2C接口系列芯片,实现了电平转换、GPIO扩展、双向转换开关和热插拔缓冲的四大功能全覆盖。电科星拓的I2C接口系列芯片凭借其卓越的性能、可靠的品质,已经被广泛应用在服务器、存储阵列、交换机和工业设备中,实现平稳可靠的数据传输。

电子商城

服务

深圳市启威测实验室,面向所有企业提供信号完整性测试服务,主要包括USB、HDMI 、DP、MIPI、PCIe 、SD/EMMC、DDR接口信号测试。测试手段有波形测试、眼图测试、抖动测试等。

提交需求>

Ignion可支持多协议、宽频段的物联网天线方案设计,协议:Wi-Fi、Bluetooth、UWB、Lora、Zigbee、2G、3G、4G、5G、CBRS、GNSS、GSM、LTE-M、NB-IoT等,频段范围:400MHz~10600MHz。

最小起订量: 2500 提交需求>

登录 | 立即注册

提交评论