智多晶SA5T-100系列FPGA DP IP简介

1、DP(DisplayPort)接口介绍

DisplayPort是由美国视频电子协会(VESA)在2006年5月提出的一种新型的数字显示接口规范,旨在支持内部和外部数字显示器连接。

Display Port图像显示接口不仅传输率高,而且可靠稳定,其接口传输的信号由传输图像的数据通道信号以及传输图像相关的状态、控制信息的辅助通道信号组成,具体包含DisplayPort数据传输主要通道(Main Link)、辅助通道(AUX Channel)与连接(Link Training)。

DisplayPort 的外部应用包括 PC、显示器和投影仪之间的显示连接,还适用于高清内容应用程序(如光驱播放器、移动设备、个人录像机和电视)之间的连接。

2.1、SA5T-100 FPGA概述

西安智多晶微电子有限公司的SA5T-100 FPGA属于Seal(海豹)5000系列器件,本系列器件建立在一个优化、高性能28nm工艺基础之上。通过使用低成本设计,并将新架构与多个优化功能的嵌入式模块融合来实现高速FPGA,使系统设计师在降低成本的同时又能够满足不断增长的高性能应用要求。对无线和有线通信、工业控制,图像处理,人工智能,数据处理中心及云信息等行业中的低功耗,高性能的大小型应用,本系列FPGA无疑是最理想的选择。

2.2 SA5T-100 FPGA特性

超大的逻辑资源

⚫ 101,978等效逻辑单元

⚫ 多达300个用户I / O

高性能可编程逻辑单元

⚫ 采用6输入查找表(6-LUTs)

⚫ 双5-LUTs选项

低功耗器件

⚫ 先进28nm高性能铜CMOS工艺

⚫ 核电压1.0V

嵌入式和分布式存储

⚫ Fmax = 500 MHz

⚫ 嵌入块存储容量为18Kbit/36Kbit, 总容量高达5,616Kbits

⚫ 高达2,040Kbit的分布式存储

增强的乘法器块

⚫ Fmax = 500 MHz

⚫ 内置多个9x9/18x18/25x18具备预加法的串行乘法器, 算数逻辑单元(ALU),两层叠加实现DSP处理密集型应用

灵活的片内时钟

⚫ 最多32个全局时钟

⚫ 高达24个延时锁相环(DLL)用于高速I/O接口

⚫ 高达7个内置通用PLL、提供倍频、分频、相位转移、展频等系统时钟

⚫ 精度为±5%的片上振荡器

集成高速串行接口(SerDes)

⚫ 集成2个4通道高速SerDes

⚫ 数据速率6.6 /10.3 Gbps

3、智多晶DP IP规格介绍

⚫ 支持TX/RX controller

⚫ 支持VESA DisplayPort Standard V1.1a and V1.2a.

⚫ 支持1、2、4 lanes

⚫ 支持每lane线速率1.62、2.7、5.4Gb/s.

⚫ 支持1、2、4像素宽度接口

⚫ 支持RGB、YCrCb像素格式,色彩量化位宽最高支持16bit

⚫ 支持1 Mb/s AUX通信

⚫ 支持eDP与DP接口

⚫ 支持自定义EDID

⚫ 支持最高4K@60Hz显示

⚫ 支持APB控制接口与Native图像接

4、DP DEMO介绍

4.1 DP DEMO程序结构

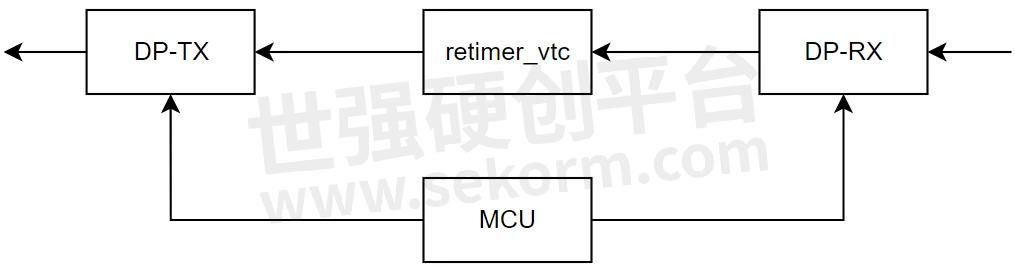

DEMO逻辑部分由DP TX/RX Controller、retimer_vtc与MCU构成。

retimer_vtc:缓存一行RX Controller输出的图像数据,保证TX Controller输入的每一行图像数据都是完整的。

MCU:实现对DP TX/RX Controller的初始化配置,同时也负责控制整个DEMO的工作流程与调试信息的打印。

图2-1 DEMO程序结构示意图

4.2 DP DEMO硬件结构

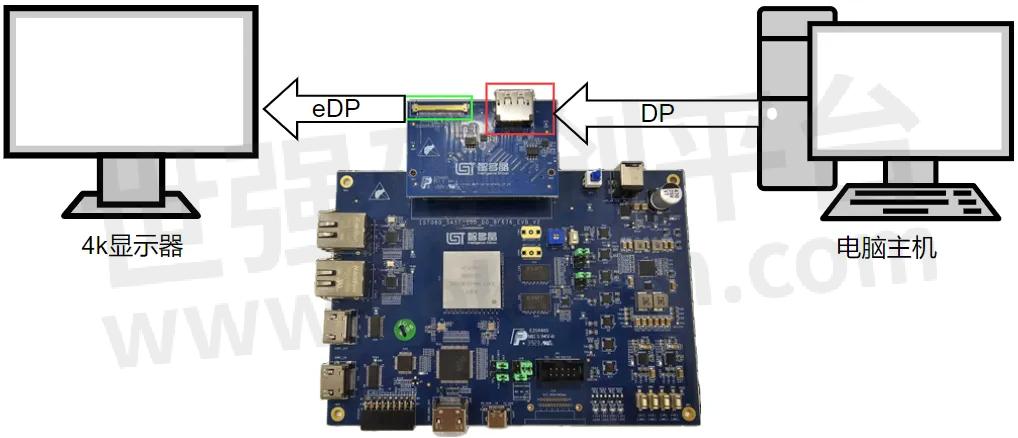

DP DEMO使用智多晶IST060_SA5Z_100_D0_8F676_EVB_V2开发板作为底板,经过FMC接口外接IST060_SA5Z_100_D0_8F676_DP_V3子板,子板搭载了DP与EDP接口。

显示屏使用京东方(BOE) MV270QUMNM1 4K@60Hz显示屏。

图2-2 DEMO硬件结构示意图

- |

- +1 赞 0

- 收藏

- 评论 0

本文由ll转载自智多晶公众号,原文标题为:“芯”技术分享 | 智多晶DP IP简介,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【经验】如何在FPGA上实现低成本开根号运算?

开根号运算是科学计算和工程应用中基本而重要的运算之一,在QuartusII和ISE开发软件中,都集成了开根号的ip核,这些底层源码对于用户来说是不可见的,那么如何在西安智多晶的FPGA中实现开根号运算,是本文要探讨的课题。

【经验】西安智多晶5000系列FPGA内嵌MCU调试测试指南

西安智多晶推出的Seal 5000 FPGA SA5Z-30系列内部合封Cortex M3硬核,最高主频可达200Mhz,32KB数据RAM和128KB指令RAM。本文针对FPGA内嵌M3硬核的使用做简洁的开发过程。

【经验】MCU通过SPI接口实现升级FPGA的方法

西安智多晶Sealion2000系列SL2E-5E是集成了Flash的FPGA,可用于替换XO2、XO3器件,及MAX II、MAX V等国外性价比不高的CPLD。本文介绍一种MCU通过SPI接口实现FPGA程序升级的方法,已经成功应用于客户的实际项目中。

SA5Z-50 FPGA 时钟资源用户指南

本指南详细介绍了SA5Z-50 FPGA的时钟资源,包括全局时钟、时钟输入引脚、时钟相关原语、时钟管理和PLL(锁相环)等。指南涵盖了时钟资源分布、输入选择、切换、分频、同步以及PLL的配置和使用方法,旨在帮助用户理解和利用SA5Z-50 FPGA的时钟系统,实现时钟优化和功耗管理。

智多晶 - 现场可编程门阵列,FPGA,SA5Z-50,时钟资源管理

【经验】解析智多晶合封系列FPGA中DDR2的应用

合封系列FPGA可以应用在需要大量缓存数据的场合,比如工业数据采集卡、视频处理应用以及无线通信中的数据采集板,如果各位读者朋友们有需要用到FPGA+DDR2架构的,可以联系智多晶,智多晶会提供完整的DDR2 Control IP,甚至亲手为用户写好应用层部分的程序,并为用户调试好。

智多晶HDMI传输Demo,用FPGA实现4K高清图像秒传

FPGA在图像传输领域扮演着非常重要的角色,FPGA的SerDes在图像传输领域是实现高速串行通信的核心技术,尤其在处理高分辨率、大带宽图像数据时发挥了关键作用,SerDes可提供高达3Gbps、6Gbps、10Gbps等的线速率通信。

【IC】智多晶28nm FPGA家族SEAL5000系列新发SA5Z-100,采用低功耗28nm@LUT6工艺

2022年的下半年,西安智多晶28nm SEAL5000家族系列喜迎重量级新成员SA5Z-100,采用先进低功耗的28nm@LUT6工艺,集成高达8个通道13.1Gbps的高速SerDes,支持PCIe2.0 x4以及HDMI2.1等接口协议。

SA5T-100 FPGA 开发板用户指南

本指南详细介绍了西安智多晶微电子有限公司的SA5T-100 FPGA开发板。该开发板基于28nm CMOS铜工艺的SA5T-100 FPGA芯片,适用于工业控制、视频接口处理等领域的前期评估。开发板具备丰富的硬件资源和外围接口,包括电源、时钟、ADC、QSPI、I2C、DDR3、以太网、HDMI、摄像头模组、微矩形连接器、USB-UART、按键、LED指示灯和FMC接口等。指南详细描述了各接口的原理图、引脚描述和功能,为用户提供了全面的使用指导。

智多晶 - 高性能 28NM 100K 逻辑规模 FPGA 芯片,开发板,FPGA 开发板,SA5T_100_D0_8F676C,SA5T-100,工业控制,视频接口处理

解析PLL技术在FPGA中的动态调频与展频功能应用

随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术在FPGA中的动态调频与展频功能应用。

“2024年智多晶FPGA技术研讨会.深圳站”圆满结束,智多晶展示多款FPGA芯片新产品、多项新应用方案

8月28日,“2024年智多晶FPGA技术研讨会.深圳站”圆满收官。智多晶的产品团队对公司的最新产品进行了全面介绍,且首次公开其最新研SA5T-366、SA5T-200、SA5T-100、SA5Z-30等FPGA产品,以及产品在通信、汽车电子、消费电子等多个领域的创新应用解决方案,展示了智多晶在微电子领域的研发实力和产品优势。

Seal(海豹)SA5Z-30 FPGA 产品手册

西安智多晶微电子有限公司发布的SA5Z-30 FPGA产品手册详细介绍了该系列FPGA的特性、资源、结构和封装。该系列基于28nm工艺,具备丰富的逻辑资源和高性能可编程逻辑单元,适用于无线通信、工业控制、图像处理等领域。

智多晶 - 现场可编程门阵列,FPGA,海豹5000系列,SA5Z-30-D2,SA5Z-30-ES,SA5Z-30-D0-UBGA324,SA5Z-30-D0,SA5Z-30-D1,SA5Z-30-D1-UBGA213,SA5Z-30-D2-8U213C5,SA5Z-30,SA5Z-30-D1-8U213C4,SA5Z-30-D2-8U213C6,SA5Z-30-D2-UBGA213,SEAL 5000系列,SA5Z-100-D1-8U324C,SA5Z-30-D0-8U324C6,SA5Z-30 系列,SA5Z-30-D1-8U213C,SA5Z-30-D2-8U213C

SL2-25E FPGA(车规级)数据手册

本资料为西安智多晶微电子有限公司的SL2-25E FPGA车规级器件数据手册,详细介绍了该器件的特性、资源、架构、逻辑单元、存储器模块、时钟网络、I/O特性、配置模式、电气特性等。SL2-25E FPGA采用55nm工艺,具有低功耗、高性能、丰富的逻辑资源、内置DSP、支持多种存储器和时钟资源等特点,适用于汽车电子、工业控制等领域。

智多晶 - 现场可编程门阵列,FPGA,SL2-25E,车规级应用

【经验】智多晶FPGA差分IO设置方法

客户使用西安智多晶FPGA时需要使用差分IO,但不知道怎么设置使用。客户之前使用xilinx的FPGA,跟智多晶的使用方式不一样,因此本文针对智多晶差分IO的使用做详细说明。

【产品】西安智多晶新推Sealion系列FPGA SL2E-7E/V,具有低成本、低功耗优势

西安智多晶微电子有限公司的Sealion(海狮)系列SL2E-7E/V FPGA ,建立在一个优化的低功耗工艺基础之上,并提供最低的功耗,通过最低的成本实现较高的功能性。规模为6,864 逻辑单元(LUTs) ,规模为55nm,采用多逻辑单元以及布线资源。

SA5Z-50 FPGA 配置用户指南

本指南详细介绍了SA5Z-50 FPGA的配置过程,包括配置模式、接口、流程、重配置方法以及多片配置方式。指南涵盖了SCM、SSPI、SCPU、MSPI和JTAG等配置模式,以及EFUSE的使用、CRC校验、数据压缩和加密等功能。此外,还介绍了PLL动态配置、Daisy-chain和Ganged多片配置方法。

智多晶 - 现场可编程门阵列,FPGA,SA5Z-50,配置

电子商城

现货市场

登录 | 立即注册

提交评论