DDR信号完整性测试如何测试?

DDR测试前需要提供的资料:

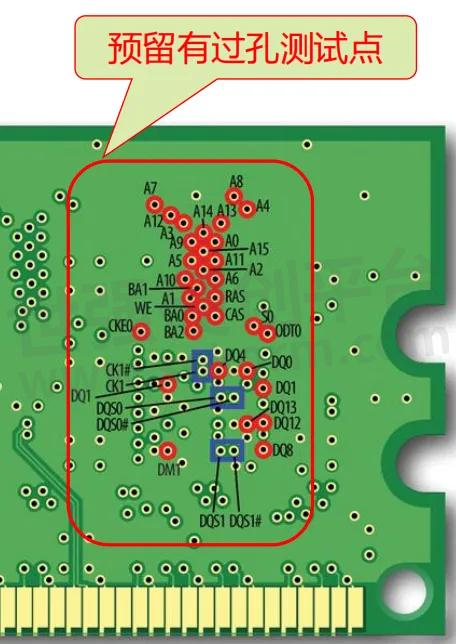

1、可以正常工作的样机,并标出测试位置;(如图1)

2、提供DDR部分的线路图,layout,DDR颗粒datasheet

图1 DDR测试位置

当进行DDR(包括DDR3)信号完整性测试时,以下是一般的测试步骤以及需要注意的事项:

01 测试步骤:

1. 确定测试目的和参数:

确定要测试的DDR信号完整性参数,如时序、眼图、串扰等。

确定测试的频率范围和测试条件。

2. 设备准备:

确保测试仪器(示波器、时序分析仪器等)已校准并正常运行。

准备好必要的信号发生器、负载板等设备。

3. 信号线路连接和准备:

将被测试的DDR信号线路正确连接到测试仪器。

检查信号线路的布局和设计,确保符合DDR规范要求。

4. 进行测试:

开始进行时序分析,测量和分析信号的延迟和时序关系。

进行眼图分析,评估信号的稳定性和波形情况。

进行串扰分析,检测信号之间的串扰情况。

5. 结果分析和报告:

分析测试结果,对比标准要求,评估信号完整性。

编制测试报告,记录测试数据和结论。

02 注意事项:

1.确保测试环境稳定,避免外部干扰对测试结果的影响。

2.样品准备时,注意保护芯片及接口,避免损坏。

3.注意设备和信号线路的校准和调节,确保测试准确性。

4.在测试过程中,注意观察并记录异常情况,及时处理。

5.测试结束后,对结果进行仔细分析,确保数据准确性和可靠性。

通过遵循以上测试步骤和注意事项,您可以有效地进行DDR信号完整性测试,并确保系统的稳定性和性能。如果遇到问题或需要进一步的技术支持,建议咨询专业工程师或测试机构,以获得更准确的测试结果和解决方案。希望这些信息能帮助您顺利完成DDR信号完整性测试!

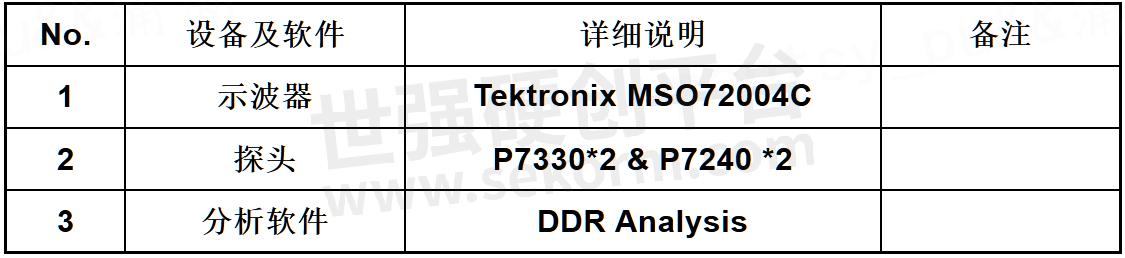

3 DDR3测试需要的设备及软件:

DDR测试项目:

4 DDR接口的基本原理

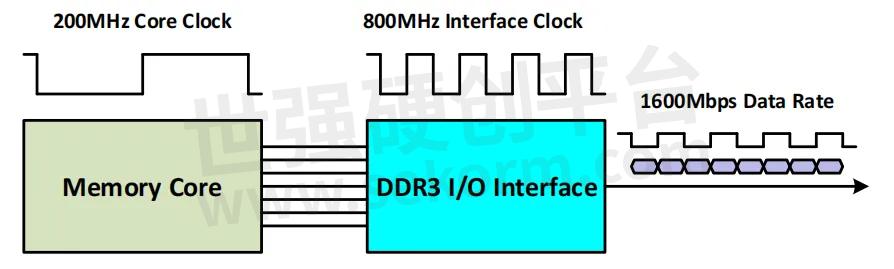

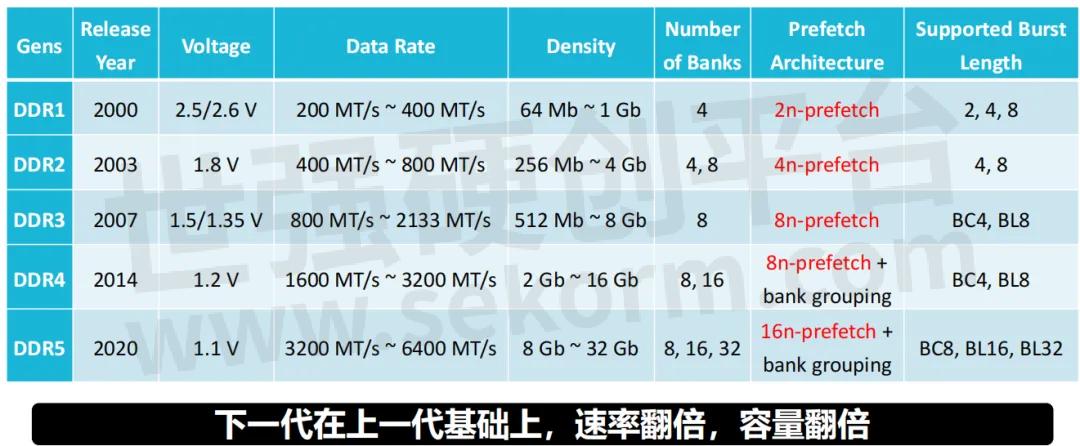

• 内核的频率:100MHz~266MHz,从SDR时代到DDR,再到最新的DDR5;

• 数据速率的提升是通过I/O接口的架构设计实现的,主要有三个技术:

1) 双边沿传输数据:这是DDR名称的来源;

2) 预取技术(Prefetch): 2bit for DDR, 4bit for DDR2, 8bit for DDR3, 8bit for DDR4, 16bit for DDR5…本质上是一个串并转换技术;

3) SSTL/POD Signaling: 克服在高速传输时的信号完整性的问题。

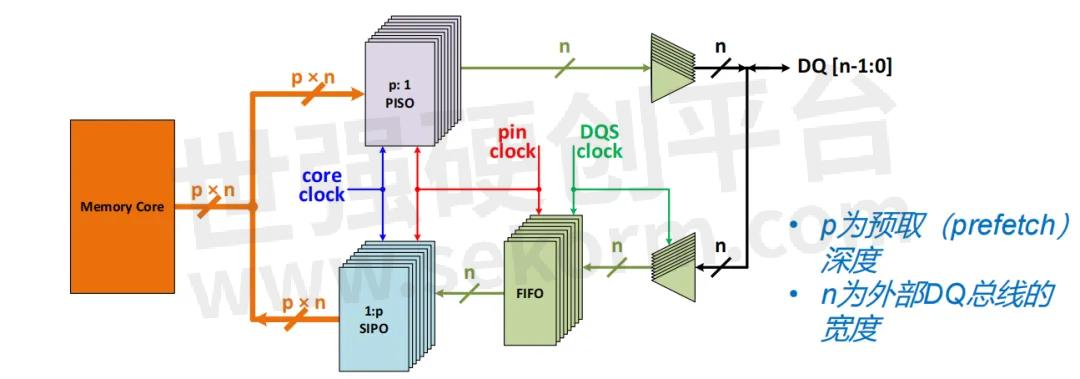

芯片内部的一般架构:保证数据能够高速从芯片引脚输出

在上述这样一种芯片架构中,为了最大程度的降低DRAM芯片的成本,最省成本的方法为:

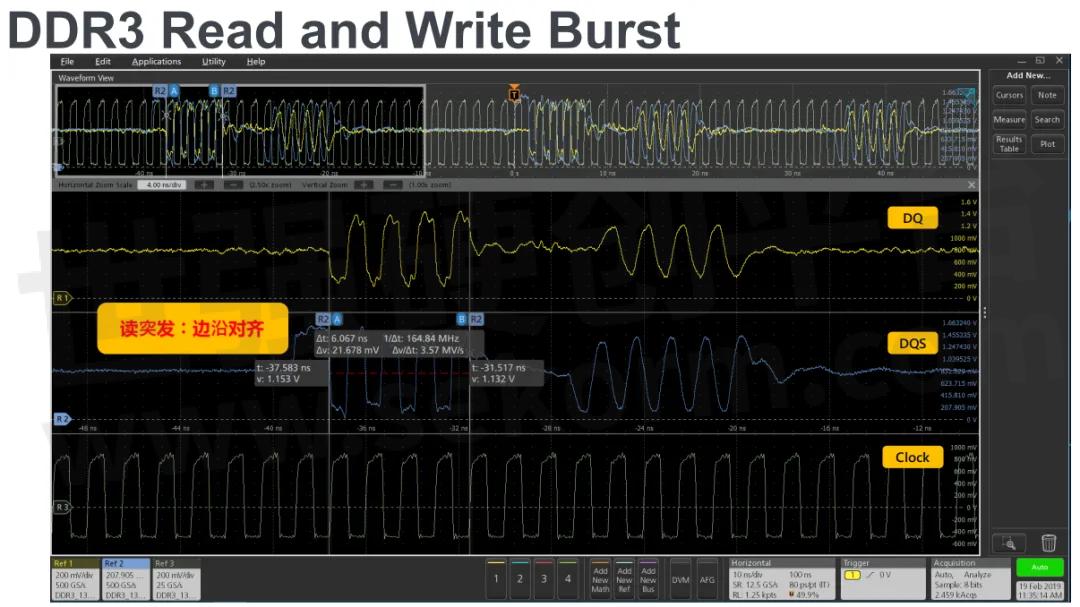

• 对于读操作,DQS与DQ为边沿对齐;

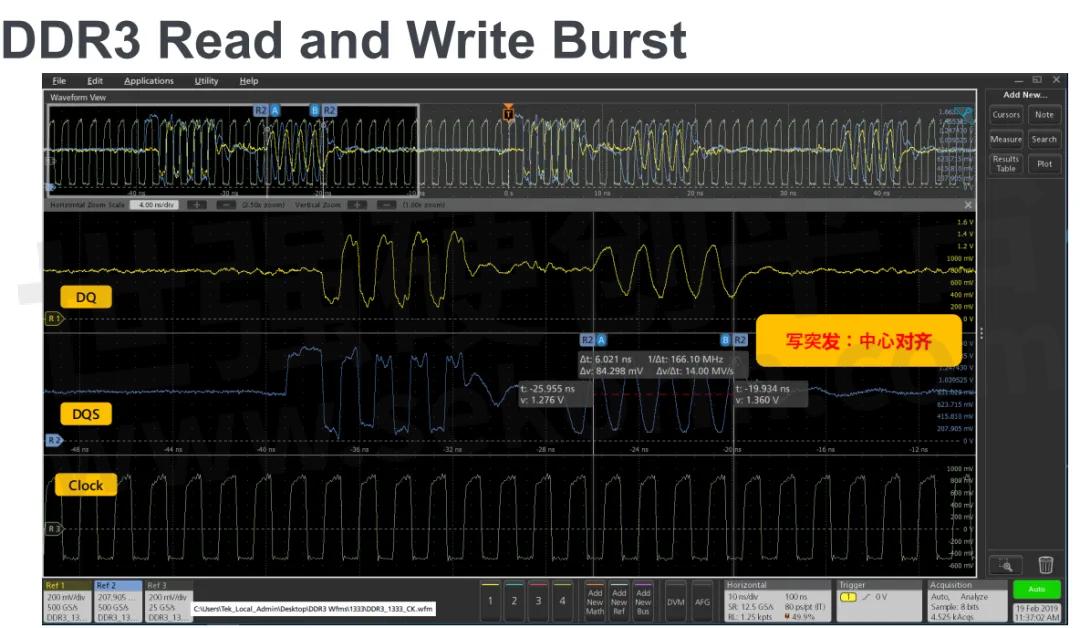

• 对于写操作,DQS与DQ为中心对齐。

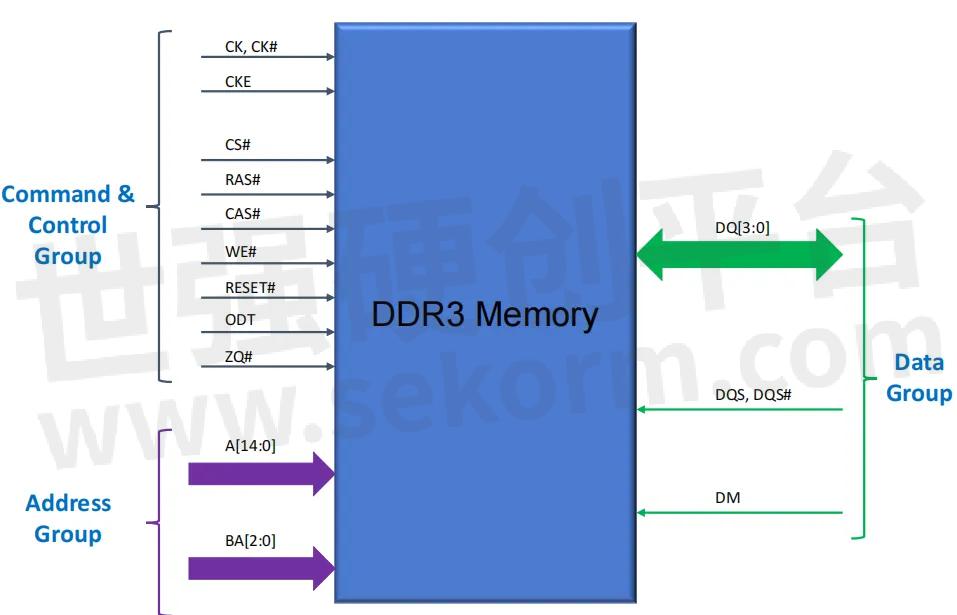

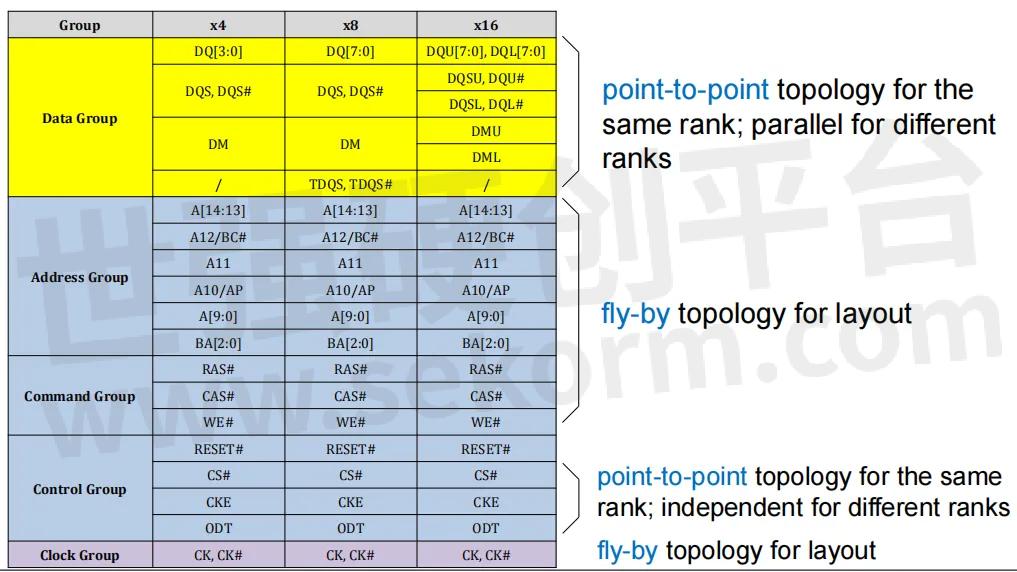

5 DDR接口信号分类

6 信号分类及其拓扑连接方式

不同类的信号,它的拓扑连接方式不一样。

7 DDR接口举例说明:DDR3 DIMM Layout

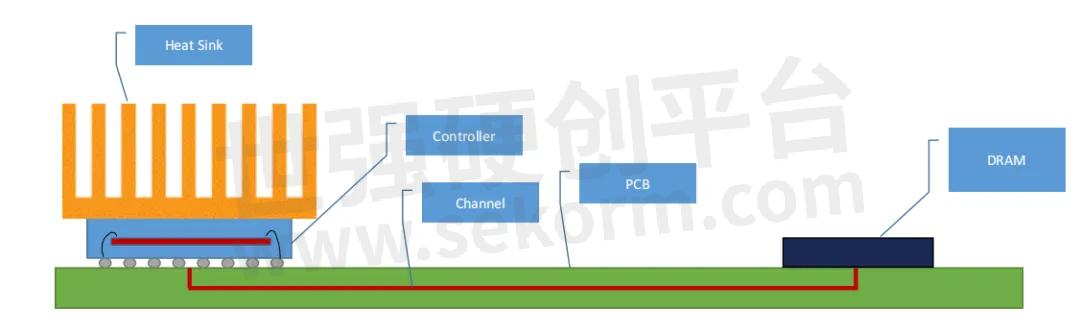

8 DDR内存的组织方式:嵌入式系统

• 内存控制器芯片与DRAM颗粒芯片在同一块PCB上;

• 内存通道的总线宽度根据所选择的内存控制器芯片的不同而不同;

• CPU Core并不是直接和内存发生作用,而是通过缓存来和内存发生作用;

• Cache Line的大小为64 Byte;也就是说缓存与内存相互作用的最小单位为64 Byte。

• 计算机系统采用标准化的DIMM,可以使用多种探测解决方案进行探测。

• 嵌入式设计中的通常直接把DRAM芯片焊接在PCB上,而所有的DDR3颗粒均采用BGA封装。

JEDEC的规格定义的测试点为BGA的焊球处。

• 在PCB layout时,就通过过孔在背面预留有测试 点,这样可以直接点测完全信号的探测;也就是DfT(Design for Test)。

• 当使用直接探测时,可以得到很好的信号保真度。

• 但对于PCB正反面都贴有DRAM颗粒,这种方法无能为力。

DDR测试方案一:直接探测

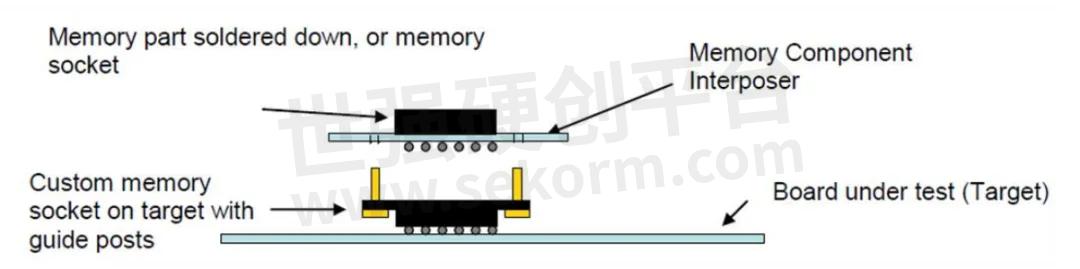

DDR测试方案二:BGA Interposer

10 突发识别的方法

• 在分析时,需要自动将读突发和写突发分离开来独自进行分析

• 对于读写分离,有若干种方法:

1) DQ/DQS phase alignment:基于读操作和写操作的DQ/DQS相位对齐关系的不同,读操作为边沿对齐,写操作为中心对齐。这种最常用。

2) Visual Trigger:可视触发,用户自定义可视触发条件,灵活度非常高;

3)CS, Latency + DQ/DQS phase alignment:当有多个rank时,需要通过CS信号来区分是哪一个rank进行读写;

4) Logic State + Burst Latency:通过解析命令信号群组(RAS#-CAS#-WE#)来确定读操作和写操作。

启威测实验室提供DDR2/3/4/5信号完整性测试及一致性验证,更多关于DDR测试解决方案,请联系启威测实验室。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由Ray转载自启威测 微信公众号,原文标题为:DDR信号完整性测试如何测试?,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

内存DDR4信号一致性眼图测试的案例分享

在 DDR4 规范 JESD79‐4 中,对物理层信号测试要求有:DQ眼图模板测试、抖动分析、电气特性测试,时序测试。相比 DDR3,DDR4 对眼图测试和抖动测试提出了新的要求。启威测实验室提供DDR2/3/4/5以及LPDDR4信号完整性测试及一致性验证。

什么是汽车以太网100M BASE-T1?启威测实测案例带你了解100M BASE-T1信号测试!

100M BASE-T1的开发是为了满足汽车系统的需求,尽管以太网是商业和工业应用中长期流行的通信协议,但直到100BASE-T1的出现,它才被广泛应用于汽车工业。

什么是SDIO?启威测实验室SDIO信号测试

SDIO作为一种普遍应用于各种便携式设备的接口标准,SDIO不仅仅局限于数据存储,它还可以扩展设备的功能。启威测实验室是一家专业的电子产品和通信设备测试实验室,拥有先进的测试设备和丰富的行业经验。深入理解SDIO技术的标准和要求,并且提供一系列针对SDIO接口的信号质量测试服务。

遇到DDR信号完整性测试问题?来看这份故障排除指南

DDR测试环境图DDR芯片(Double Data Rate )的信号完整性测试在设计和验证DDR存储系统时非常重要。当在进行DDR(包括DDR3/4/5)信号完整性测试时遇到问题时,本文介绍DDR信号完整性测试问题故障排除指南。

SiC-MOSFET让汽车及工业设备更小更高效,宽耐压,开关损耗降低50%

世强硬创联合瑶芯微,爱仕特,派恩杰,瞻芯电子,中电国基南方,带来让汽车及工业设备更小更高效的SiC MOSFET系列产品,最高1700V宽耐压,开关损耗降低50%。

启威测实验室提供材料的物理性能检测服务,塑料的物理性能测试项目标准及送样要求一网打尽

启威测实验室提供塑料材料的物理性能和热学性能测试服务,涵盖聚乙烯、聚丙烯、聚对苯二甲酸乙二醇酯、聚氯乙烯、聚苯乙烯、聚碳酸酯和ABS等材料。服务包括硬度、拉伸强度、冲击强度等多种测试项目,满足不同塑料材料的检测需求。

【视频】瑶芯微SiC MOSFET让汽车及工业设备更小更高效

型号- AKCK2M040WAM,AK1CK2M040WAM,AKCK2M050WAMH,AKCL0M040YAMH,AK2CK2M040WAMH,AKCL3M040YAMH,AKCK2M1K0DBMH,AKCK2M016WAMH

60V霍尔效应双极传感器SLSS41F,工作电流7mA,专为汽车和工业应用而设计

SLKOR SLSS41F霍尔效应双极传感器是一款专为汽车和工业应用而设计的高性能传感器。该传感器采用了高压双极技术,能够在广泛的工作电源电压范围内正常运行,从3.8V到60V,适应不同应用场景的需求。SLSS41F提供SOT23和TO-92S两种封装。

罗姆即将亮相2024慕尼黑电子展,并展示其在“电动交通”、“汽车”和“工业”主题下的最新解决方案

罗姆即将亮相2024慕尼黑电子展,展示其先进的功率和模拟技术,旨在提高汽车和工业应用中的功率密度、效率和可靠性。这些先进技术对于满足现代电子系统日益增长的需求至关重要,特别是在可持续性和创新的背景下。

启威测与世强硬创达成合作,提供信号完整性及失效分析等测试服务

合作双方共同为用户提供开封测试、超声波扫描、接口类信号量测、传输类信号量测、Memory信号量测、低速总线信号量测等服务。

聚焦慕尼黑印度电子展,捷捷微电展现汽车、消费电子及工业应用领域技术新突破

2024年9月11日至13日,捷捷微电将亮相慕尼黑印度电子展(electronica India),展会地点位于印度新德里大诺伊达的印度博览中心。作为中国功率半导体行业的领先企业之一,捷捷微电将在10号馆F45展位展示多样化的半导体产品,涵盖汽车、消费电子及工业应用。

启威测带您了解DisplayPort AUX的秘密及其测试服务

在这个视觉体验日益重要的时代,DisplayPort技术作为连接高清显示器和计算机的重要桥梁,已成为众多高性能系统的首选。然而,许多人可能不知道,DisplayPort技术中一个关键但经常被忽视的组成部分——DisplayPort AUX通道(辅助通道)。

固态硬盘SSD的M.2、U.2、SATA和PCIe接口类型解析及启威测实验室提供完整SSD检测服务

启威测实验室提供全方位的SSD检测服务,涵盖信号完整性、可靠性及失效分析、性能测试、耐久性评估验证等多个方面。技术专长:凭借先进的测试技术和丰富的行业经验,启威测实验室能准确分析SSD在不同接口类型下的信号一致性,帮助您做出最佳选择。

基于RFID技术的汽车制造工业系统解决方案

RFID(无线射频识别)是近年来迅速发展的一种快速识别技术,通过对被识别物体的无接触识别获取资料信息,与传统条形码技术相比,具有数据容量大、无接触识别、保存时间长、耐污适应恶劣环境等特点,被广泛应用于各行业。

服务

深圳市启威测实验室,面向所有企业提供信号完整性测试服务,主要包括USB、HDMI 、DP、MIPI、PCIe 、SD/EMMC、DDR接口信号测试。测试手段有波形测试、眼图测试、抖动测试等。

提交需求>

根据用户的接口模块,使用是德示波器及夹具查看实时眼图演示,测试USB/MIPI/DDR/SATA/HDMI协议,支持最高到1.2GHz的实时眼图协议测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论