PCIe信号完整性测试送样前的准备工作及异常整改解析

在进行PCI Express (PCIe) 信号完整性测试前的准备工作以及遇到异常时的整改措施,对于确保测试效率和产品质量具有至关重要的意义。以下是送样前的详细准备步骤和异常整改策略。

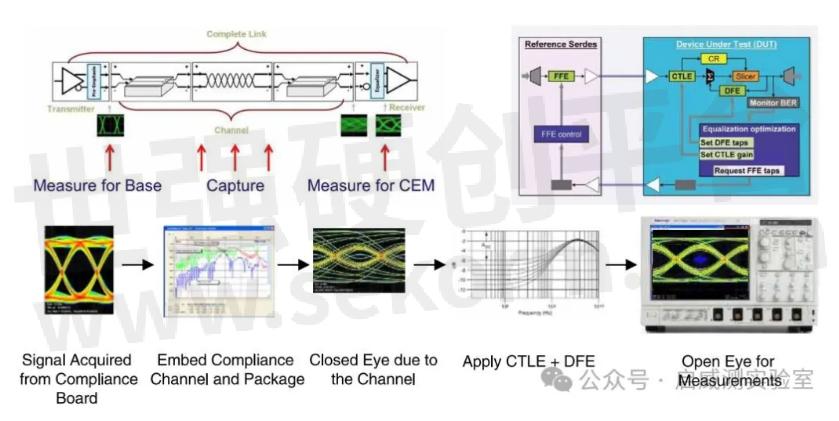

图1 PCIe典型链路测试示意图

送样前的准备工作

1.详细检查设计和布局:

确保高速信号的走线遵循最佳设计实践,如短路径、避免交叉和正确的阻抗匹配。

检查是否有足够的地和电源层,以减少信号干扰和提供稳定的电源。

2.模拟和仿真:

在进行物理测试之前,使用专业的EDA工具执行信号完整性和电磁兼容性仿真。

调整设计中发现的任何潜在问题,如反射、串扰或信号衰减。

3.原型制作:

制作初步原型板,并确保使用的材料和工艺符合设计规范。

对原型板进行初步的功能测试,确保没有基本的电气或功能错误。

4.预测试:

在送样进行正式的信号完整性测试前,先在内部或第三方实验室进行预测试。

利用眼图测试、TDR分析和误码率测试等工具,初步评估信号完整性。

5.文档准备:

准备完整的设计文件、测试说明书和预期的测试结果。

包括任何特殊测试要求或已知的潜在问题点。

异常整改解析

在PCIe信号完整性测试中,如果发现异常,如信号完整性不符合预期,需要采取以下步骤进行整改:

1.详细分析测试报告:

仔细阅读测试报告中的所有细节,特别关注未通过的测试项和边缘条件。

分析异常可能的原因,如设计缺陷、制造问题或测试设置错误。

2.针对性的设计修改:

根据分析结果,对PCB设计进行针对性修改,可能涉及走线优化、阻抗调整或屏蔽增强。

重新进行仿真测试,验证改进措施的效果。

3.原型板再制作:

修改设计后,制作新的原型板。

进行快速的预测试,确保修改达到预期效果。

4.二次正式测试:

将修改后的样品送回测试实验室进行再次测试。

仔细比较两次测试结果,确保所有问题已经得到解决。

5.测试结果评审和文档更新:

对测试结果进行详尽的评审,确保产品完全符合PCIe标准和性能要求。

更新所有相关的设计和测试文档,记录所做的改变和测试结果。

6.反馈循环:

将测试和整改过程中得到的经验反馈到设计和制造流程中,以优化未来的产品开发。

通过这样的流程,可以系统地解决在PCIe信号完整性测试中遇到的问题,提高产品的质量和可靠性。这不仅有助于满足技术标准,也为最终用户提供了更好的产品体验。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由犀牛先生转载自启威测实验室公众号,原文标题为:PCIe信号完整性测试送样前的准备工作及异常整改解析,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

PCIe 3.0信号完整性测试的基本步骤和方法

PCIe 3.0信号完整性测试是确保PCI Express 3.0接口设备能够在最大传输速率下稳定工作的关键步骤。PCIe 3.0标准支持每秒最多8 GT/s的传输速度,这要求高频信号在传输过程中保持较高的完整性。本文将介绍PCIe 3.0信号完整性测试的基本步骤和方法。

设计经验 发布时间 : 2024-07-12

PCIe TX/RX 物理层信号完整性测试方法详解

PCI Express (PCIe) 是一种高性能通用I/O互连协议,广泛用于各种计算产品和通信产品。由于时延低、带宽明显要更高,因此业界正在融合到PCIe,作为高速串行总线标准。PCIe在NVM Express SSD应用中尤其流行。

设计经验 发布时间 : 2024-05-28

【高速信号测试】MIPI-DSI/ MIPI-D PHY 信号完整性如何测试?MIPI-DSI 测试项目及测试案例

进行MIPI-DSI信号完整性测试时,细节和精确性是至关重要的。确保遵循MIPI联盟的标准和指南,以及设备制造商提供的具体要求。本文由启威测实验室小编整理有关MIPI-DSI测试项目、测试设备及软件,测试过程设置、及测试实测案例,方便你快速了解MIPI-DSI信号完整性测试。

设计经验 发布时间 : 2024-10-25

PCI-SIG对PCIe Link EQ Response测试的规范要求及其重要性

PCI-SIG对PCIe Link EQ Response测试的规范要求是确保高速数据传输质量和系统性能的关键。通过严格控制链路训练、均衡参数和信号完整性,PCI-SIG保障了PCIe设备的高性能和互操作性。希望本文能帮助你更好地理解PCIe Link EQ Response测试的要求及其重要性。

技术探讨 发布时间 : 2024-09-07

解析PCIe 4.0与PCIe 3.0信号完整性测试项目及测试的必要性

PCIe 4.0标准在速度、带宽和性能上都有显著的改进,但这些提升也带来关于信号完整性的额外挑战。这就要求在设计和生产过程中进行更严格和全面的信号完整性测试。本文将介绍PCIe 4.0与PCIe 3.0信号完整性测试项目及测试的必要性。

技术探讨 发布时间 : 2024-08-19

固态硬盘SSD的M.2、U.2、SATA和PCIe接口类型解析及启威测实验室提供完整SSD检测服务

启威测实验室提供全方位的SSD检测服务,涵盖信号完整性、可靠性及失效分析、性能测试、耐久性评估验证等多个方面。技术专长:凭借先进的测试技术和丰富的行业经验,启威测实验室能准确分析SSD在不同接口类型下的信号一致性,帮助您做出最佳选择。

技术探讨 发布时间 : 2024-05-31

PCI-SIG对PCIe TX眼图的规范要求及其重要性

在高速数据传输中,信号完整性是确保设备性能和稳定性的关键。PCI-SIG为PCI Express(PCIe)接口规定了一系列电气规范,其中之一就是发送端(TX)的眼图要求。眼图是评估高速信号质量的重要工具,通过分析眼图,可以确定信号在传输过程中的失真程度和质量。本文将详细介绍PCI-SIG对PCIe TX眼图的规范要求及其重要性。

技术探讨 发布时间 : 2024-08-22

探讨信号一致性测试与信号完整性测试之间的关系

在高速通信领域,尤其是在使用PCI Express (PCIe) 3.0/4.0/5.0这类先进接口技术的设备与系统中,信号一致性测试和信号完整性测试是保证设备可靠性和互操作性的重要环节。通过本文,我们将深入探讨信号一致性测试与信号完整性测试之间的关系,包括它们的概念、测试内容以及共同点和不同点。

技术探讨 发布时间 : 2024-07-12

PCIe 3.0信号一致性测试与PCIe 3.0信号完整性的关系

在讨论PCI Express(PCIe)3.0接口技术时,信号一致性测试和信号完整性是两个经常被提及的重要概念。虽然它们密切相关,但指向的侧重点有所不同。理解这两个概念之间的关系对于确保PCIe 3.0设备在高速数据传输中的性能和可靠性至关重要。

技术探讨 发布时间 : 2024-07-12

PCIe 3.0信号完整性测试样品准备步骤和考虑事项

为了进行PCIe 3.0信号完整性测试,样品的准备是一个关键步骤,它直接影响到测试的准确性和有效性。本文将为您介绍一些重要的准备步骤和考虑事项。

技术探讨 发布时间 : 2024-05-16

USB 3.2 Gen 1和 Gen 2的区别(附Gen 1和 Gen 2技术参数对比表)

USB 3.2 Gen 1和Gen 2是USB 3.2标准中的两个不同规格,彼此之间在传输速率和技术实现上有所不同,本文由启威测实验室整理USB 3.2 Gen 1和Gen 2相关参数。

技术探讨 发布时间 : 2024-08-16

一文介绍USB接口的传输速率及不同颜色的USB接口代表的含义

说起USB,现如今没有人不知道,毕竟这是现在世界上最成功、最普遍、最流行的接口。基本上只要是电子产品就和USB有关系,就算某台设备上没有USB,那它的充电装置往往用的也是USB线。总而言之,几乎每个人都用过USB。那么你是否注意到USB每一代之间速率的区别以及端口颜色的不同呢,今天启威测小编就和大家聊聊与USB相关的知识。

技术探讨 发布时间 : 2023-11-17

遇到HDMI接口问题?来看这份故障排除指南

本文将为您提供一份HDMI接口故障排除指南,帮助您快速识别问题并找到解决方案。同时,我们也将介绍启威测实验室在HDMI接口信号测试服务方面的专业能力,让您的设备免受HDMI接口问题的困扰。

设计经验 发布时间 : 2024-06-25

USB 3.2 Gen1&Gen2性能评估及如何进行高速信号完整性测试?

在如今的数据密集型应用中,USB接口的性能显得尤为重要。USB 3.2 Gen1&Gen2作为最新的高速传输标准,为设备提供了更高的传输速率。然而,确保这种高速传输的稳定性和准确性,信号完整性测试成为关键。本文将深入讲解如何对USB 3.2接口进行性能评估,并重点介绍信号完整性测试的具体方法和步骤。

技术探讨 发布时间 : 2024-07-09

服务

深圳市启威测实验室,面向所有企业提供信号完整性测试服务,主要包括USB、HDMI 、DP、MIPI、PCIe 、SD/EMMC、DDR接口信号测试。测试手段有波形测试、眼图测试、抖动测试等。

提交需求>

支持 3Hz ~ 26.5GHz射频信号中心频率测试;9kHz ~ 3GHz频率范围内Wi-SUN、lora、zigbee、ble和Sub-G 灵敏度测量与测试,天线阻抗测量与匹配电路调试服务。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳/苏州 提交需求>

登录 | 立即注册

提交评论