PCI-SIG对PCIe TX眼图的规范要求及其重要性

在高速数据传输中,信号完整性是确保设备性能和稳定性的关键。PCI-SIG为PCI Express(PCIe)接口规定了一系列电气规范,其中之一就是发送端(TX)的眼图要求。眼图是评估高速信号质量的重要工具,通过分析眼图,可以确定信号在传输过程中的失真程度和质量。本文将详细介绍PCI-SIG对PCIe TX眼图的规范要求及其重要性。

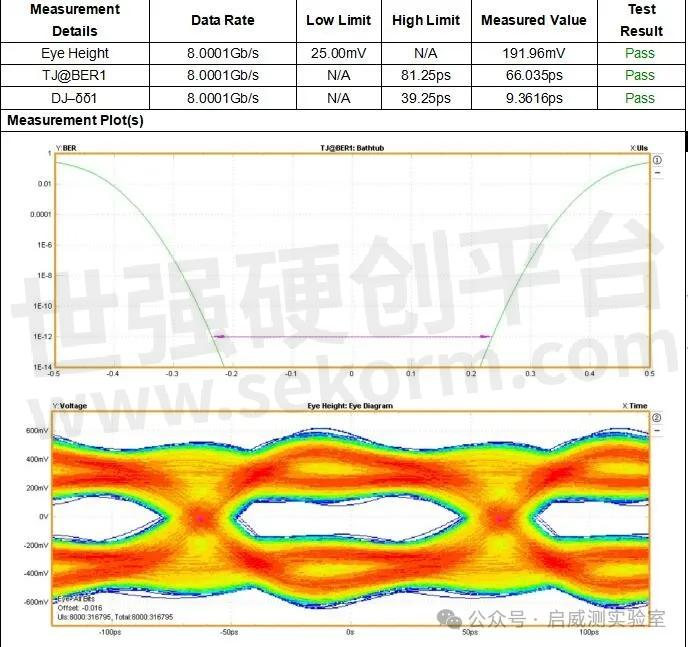

图1 PCI e 3.0眼图

什么是眼图?

眼图(Eye Diagram)是通过示波器将高速信号的多个周期叠加在一起形成的图形。它被称为“眼图”是因为其形状类似于人眼。眼图的关键参数包括眼开度(eye opening)、上升时间、下降时间、抖动(jitter)和噪声(noise)。一个理想的眼图应该有一个清晰的开口,表明信号具有良好的时间和电压裕度。

PCIe TX眼图要求

1. 眼开度(Eye Opening)

眼开度是衡量信号质量的一个重要指标。PCIe标准对眼开度有严格的要求,以确保信号在接收端能够被正确解码。眼开度由水平开度(时间裕度)和垂直开度(电压裕度)组成:

水平开度:表示信号的时间裕度,确保信号在一定的时间范围内稳定。

垂直开度:表示信号的电压裕度,确保信号在一定的电压范围内稳定。

2. 抖动(Jitter)

抖动是信号到达时间的随机或系统性偏移,会导致数据误码。PCIe规范对抖动有严格的限制:

随机抖动(Random Jitter, RJ):由噪声和热噪声引起。

确定性抖动(Deterministic Jitter, DJ):由串扰和其他系统性因素引起。

3. 上升时间和下降时间

上升时间和下降时间是指信号从低电平到高电平(上升)或从高电平到低电平(下降)所需的时间。PCIe规范要求:

上升时间:必须足够快以减少信号失真,但不能过快以免产生过多的高频噪声。

下降时间:与上升时间要求类似,确保信号的对称性和稳定性。

4. 眼图测试环境

PCIe眼图测试需要在标准的测试环境中进行,以保证测试结果的准确性。测试环境包括:

测试设置:标准规定的电压和时间范围,以及特定的测试模式。

为什么眼图测非常重要?

1. 确保信号完整性

眼图要求确保了PCIe信号在高频传输中的完整性。良好的信号完整性意味着低误码率和高数据传输可靠性。

2. 提高设备兼容性

严格的眼图要求使得不同厂商生产的设备能够在相同的电气环境中正常工作,保证了设备的互操作性。

3. 优化系统性能

符合眼图要求的设备能够最大限度地发挥PCIe的性能优势,提高整体系统的效率和速度。

结论

PCI-SIG对PCIe TX眼图的规范要求是确保高速数据传输质量的关键。通过严格控制眼开度、抖动、上升和下降时间等参数,PCI-SIG保障了PCIe设备的信号完整性和系统性能。对于制造商和用户来说,了解并遵守这些规范至关重要,不仅可以提高产品质量,还能增强市场竞争力。希望本文能帮助你更好地理解PCIe TX眼图的要求及其重要性。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由ll转载自启威测实验室公众号,原文标题为:PCIe TX信号测试│PCI-SIG规范关于PCIe TX眼图的要求,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

如何购买PCIe3.0/4.0/5.0协会治具?PCIe3.0/4.0/5.0协会治具多少钱?

PCI-SIG(PCI Special Interest Group)制定了PCIe的各种规范,并提供了相应的测试治具。本文将介绍如何采购PCIe协会治具,包括采购渠道、注意事项和使用建议。

解析PCIe 4.0与PCIe 3.0信号完整性测试项目及测试的必要性

PCIe 4.0标准在速度、带宽和性能上都有显著的改进,但这些提升也带来关于信号完整性的额外挑战。这就要求在设计和生产过程中进行更严格和全面的信号完整性测试。本文将介绍PCIe 4.0与PCIe 3.0信号完整性测试项目及测试的必要性。

PCI-SIG对PCIe PLL带宽测试的规范要求及其重要性

PCI-SIG制定了多项电气规范,以确保PCI Express(PCIe)设备的互操作性和性能稳定性。PCIe PLL带宽测试是其中一个关键测试项目。PLL在时钟信号生成和同步中起着至关重要的作用。本文将详细介绍PCI-SIG对PCIe PLL带宽测试的规范要求及其重要性。

德普福 RF Switch 系统规格书

描述- 德普福RF Switch系统是一款多端口多通道射频微波开关矩阵系统,适用于微波测试系统中待测设备(DUT)和仪器之间的信号选通。该系统具有多种配置选项,支持自动化测试,广泛应用于设计研发、品质验证和生产测试等多种场景。

型号- DRS04110-00A,DRS04108-00C,DRS04116-A0F,DRS04116-A0E,DRS04116-A0D,DRS08106-00F,DRS08106-00E,DRS04210-A0C

帮助企业实现高速电路测试无阻无忧——Misenbo(淼森波)

Misenbo(淼森波)是一家技术服务型公司,主要致力于智能硬件共享实验室服务、物联网产品研发、硬件测试服务、仪器设备租赁服务、硬件工程师培训等。公司基于实验室,构建硬件开发配套和硬件测试解决方案集成基地,为国家重点企事业单位和中小型企业提供一站式服务。

淼森波测试共享实验室接受板外接口一致性测试和板内信号质量测量,主要适用于仪器设备、无人机等场景

宁波淼森波信息技术有限公司棣属于北京淼森波信息技术有限公司,是一家技术服务型公司,即为中小型、初创型企业提供硬件开发配套服务和硬件测试服务。秉承“为中小型企业降低成本,提高工作效率”的服务宗旨。主要提供开放实验室测试、硬件单板测试、实验室的信息化管理、仪器租赁等业务。

为什么要从M8020A迁移到M8040A?

描述- 随着计算和数据中心标准的演进,测试设备需要更新以支持新一代标准和更高速度。从Keysight M8020A J-BERT过渡到M8040A高精度BERT,可以实现最新一代标准的功能验证、特性化和合规性测试。M8040A模块可生成高达64 Gbaud NRZ/PAM4的模式并分析高达64 Gbaud NRZ/58 Gbaud PAM4的错误。该产品适用于NRZ(PCIe、USB、TBT)和PAM4(200 GbE、400 GbE)编码,可通过相同的硬件模块实现,并通过Keysight M8070B用户界面和远程命令控制。此外,M8040A提供了一套全面的生态系统,包括BERT硬件、UXR系列示波器、自动化软件、ISI、干扰源、附件以及其他多种仪器。

型号- M8040A,M8051A,M8062A,M8046A,M8045A,M8020A,M8041A

MAX4888B评估套件

描述- 该资料介绍了MAX4888B评估套件(EV套件),用于评估MAX4888B双双刀双掷(2 x DPDT)开关。该设备适用于在两个可能的目的地之间切换PCI Express(PCIe)数据,支持高达8.0Gbps的数据速率(Gen III PCIe)。EV套件用于关键测试,如眼图和s参数测量(如插入损耗、反射损耗和隔离度)。套件包含MAX4888BETI+组件,采用无铅28引脚(3.5mm x 5.5mm)TQFN封装,并带有暴露的焊盘。

型号- GRM155R60J105K,GRM155R61A224K,GRM21BR61C106K,AWG7122B,GRM155R61C102K,MAX4888B,MAX4888BEVKIT#,MAX4888BETI+,DSA72004B

什么是汽车以太网100M BASE-T1?启威测实测案例带你了解100M BASE-T1信号测试!

100M BASE-T1的开发是为了满足汽车系统的需求,尽管以太网是商业和工业应用中长期流行的通信协议,但直到100BASE-T1的出现,它才被广泛应用于汽车工业。

什么是SDIO?启威测实验室SDIO信号测试

SDIO作为一种普遍应用于各种便携式设备的接口标准,SDIO不仅仅局限于数据存储,它还可以扩展设备的功能。启威测实验室是一家专业的电子产品和通信设备测试实验室,拥有先进的测试设备和丰富的行业经验。深入理解SDIO技术的标准和要求,并且提供一系列针对SDIO接口的信号质量测试服务。

启威测实验室提供材料的物理性能检测服务,塑料的物理性能测试项目标准及送样要求一网打尽

启威测实验室提供塑料材料的物理性能和热学性能测试服务,涵盖聚乙烯、聚丙烯、聚对苯二甲酸乙二醇酯、聚氯乙烯、聚苯乙烯、聚碳酸酯和ABS等材料。服务包括硬度、拉伸强度、冲击强度等多种测试项目,满足不同塑料材料的检测需求。

启威测与世强硬创达成合作,提供信号完整性及失效分析等测试服务

合作双方共同为用户提供开封测试、超声波扫描、接口类信号量测、传输类信号量测、Memory信号量测、低速总线信号量测等服务。

USB 2.0电气兼容性测试用户手册

描述- 本手册为SIGLENT公司生产的FX-USB2测试夹具与SDS7000A数字示波器配合使用的USB 2.0电气合规性测试指南。内容包括测试项目、设备、夹具、软件设置和应用说明。涵盖了主机、设备和集线器的各种电气性能测试,包括信号质量、包参数、时序、电压水平等。提供详细的测试步骤和参考值,帮助用户完成USB 2.0产品的电气合规性验证。

型号- FX-USB2

启威测带您了解DisplayPort AUX的秘密及其测试服务

在这个视觉体验日益重要的时代,DisplayPort技术作为连接高清显示器和计算机的重要桥梁,已成为众多高性能系统的首选。然而,许多人可能不知道,DisplayPort技术中一个关键但经常被忽视的组成部分——DisplayPort AUX通道(辅助通道)。

电子商城

服务

深圳市启威测实验室,面向所有企业提供信号完整性测试服务,主要包括USB、HDMI 、DP、MIPI、PCIe 、SD/EMMC、DDR接口信号测试。测试手段有波形测试、眼图测试、抖动测试等。

提交需求>

根据用户的接口模块,使用是德示波器及夹具查看实时眼图演示,测试USB/MIPI/DDR/SATA/HDMI协议,支持最高到1.2GHz的实时眼图协议测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论