【测试那点事儿】信号的过冲咋处理?-Debug 案例1

信号过冲

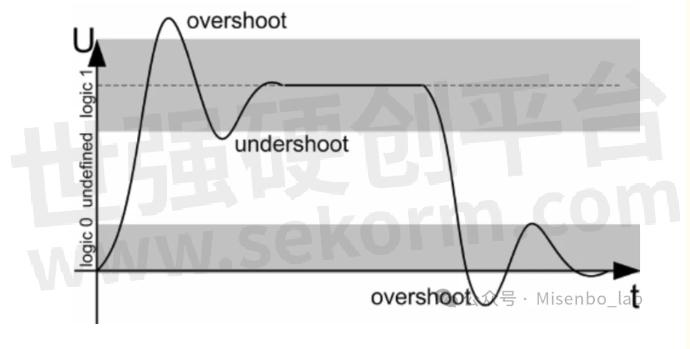

信号过冲(Overshoot)是指在数字信号传输过程中,信号幅度暂时超过其稳态值的现象。这通常发生在信号快速切换时,如从低电平到高电平或从高电平到低电平的过渡期间。

Part.01 信号过冲有哪些影响

信号过冲可能会对电子系统造成以下影响:

信号完整性问题:过冲可能导致信号失真,影响信号的完整性和数据传输的准确性(振铃产生的电压波动,可能会多次跨越逻辑电平的电压阈值,造成接收端的误判)。

电磁干扰(EMI):过冲会增加电磁辐射,从而可能干扰其他电路或设备。硬件损害:严重的过冲可能会损坏接收器端的电路,尤其是对于CMOS器件,过冲可能会导致器件损坏(当过冲幅值较大或持续时间较长时,可能会导致电路元器件的失效)。

传输距离限制:过冲会随着传输线路的长度增加而变得更加严重,限制了信号的传输距离。

Part.02 分析原因——什么引起的信号过冲

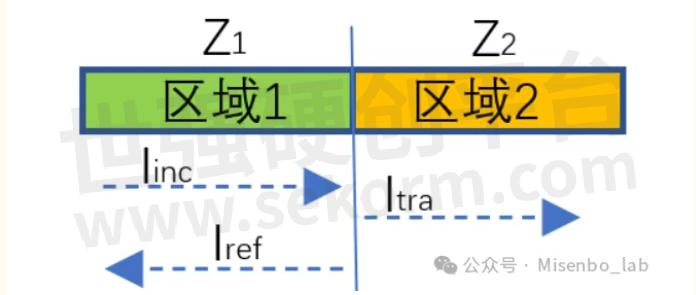

信号过冲的产生本质上是由于信号在传输过程中遇到阻抗不匹配,导致反射波在信号传输线和接收器之间来回反射。

Part.03 解决方法

调节阻抗匹配:比如在长时钟信号链路中,为了解决信号反射问题,通常会在时钟输出信号线上串接一个小电阻,这样可以减小反射波,从而避免反射波叠加引起过冲。增加电阻可以使振铃现象减少。

适当减小驱动:如果是主芯片发出来的信号过冲,则可以适当减小驱动电流。

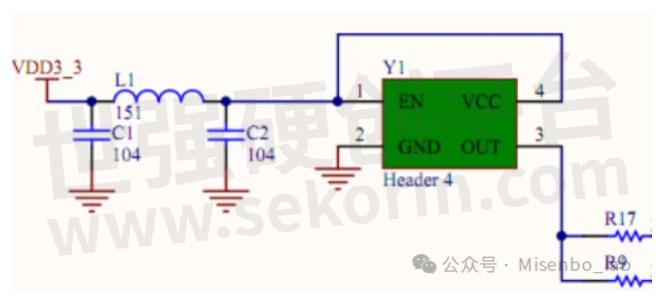

使用缓冲器或驱动器:使用适当的缓冲器或驱动器来控制信号的上升和下降时间,减少过冲。

添加滤波器:在信号线上添加滤波器,如RC滤波器,以平滑信号边缘,减少过冲。

使用差分信号:如LVDS,差分信号可以提供更好的抗干扰能力和减少过冲。

物理设计优化:优化PCB布局和布线,减少传输线长度,避免走线过长或过于紧密。

Part.04 时钟信号实测案例

通过更改设备驱动电流来减小过冲信号。

【测试环境】

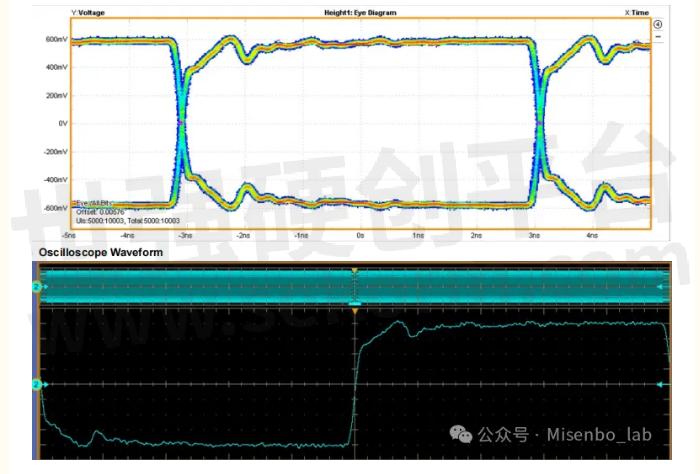

【未改变驱动电流前眼图及波形】

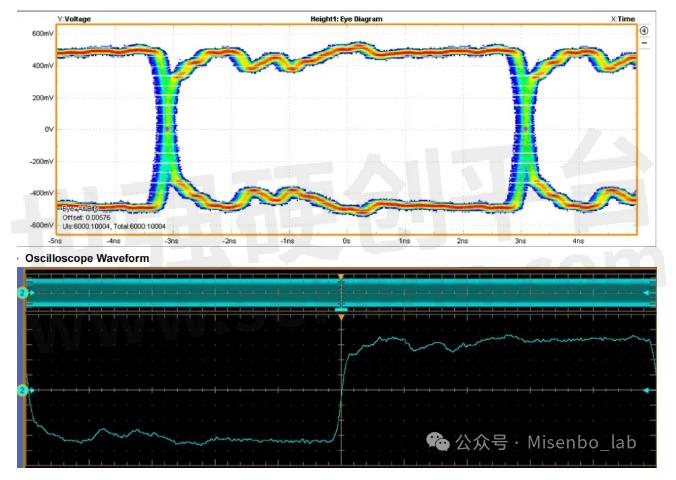

【减少驱动电流后眼图及波形】

从眼图中可以明显看到过冲有被降低。

虽然适当减少驱动端的输出电流可以降低过冲,但其根本原因还是阻抗不匹配。因此,在电路设计过程中,必须特别注意阻抗的准确计算。

淼森波实验室服务简介:

主要业务:芯片物理层验证测试、芯片验证测试的Demo板研发、AI加速卡测试、服务器测试、汽车智能座舱测试、高速信号SI/PI仿真、硬件产品故障Debug、硬件项目研发服务;仪器租赁;硬件工程师培训 。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由雪飘梦飞转载自Misenbo(淼森波公众号),原文标题为:【测试那点事儿】信号的过冲咋处理?-Debug 案例1,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【经验】时钟链路信号完整性过冲与振铃两大问题浅析

时钟在电子产品系统中占据着绝对的重要位置,为整个系统数据传输提供参考基准。简单来讲,时钟信号主要分为矩形波,正弦波两种。过冲和振铃是时钟信号完整性的两个主要问题。本文大普通信就时钟链路信号完整性过冲与振铃两大问题进行分析。

【技术大神】LVDS电平标准时钟信号匹配电路介绍

笔者本次通过femto基站产品调试过程中遇到的时钟信号质量不佳的案例来介绍LVDS电平标准时钟信号的匹配电路。推荐Silicon Labs公司的Si5338时钟芯片。

【经验】一种去抖时钟信号发生器SI5345匹配问题引起的失锁问题解决方法

Silicon Labs公司推出的高性能去抖时钟信号发生器SI5345是一款经典的时钟产品,目前已经应用于各种通信、工业、医疗、仪器等行业中,其强大的抖动抑制能力让同行产品相形见绌,这得益于其集成的第四代高性能DSPLL核心技术。有如此优良的表现,使得SI5345的应用越来越多,但是工程师们在使用SI5345的时候也碰到一些应用问题,需要引起大家的注意。

国内数字补偿技术先驱金科泰通信授权世强硬创代理全线时钟信号产品

金科泰通信旗下晶振系列、滤波器系列、时钟模块系列等全线产品上线世强硬创平台。

【应用】抖动衰减和时钟合成器AU5315用于高清接口矩阵时钟信号分配,具有4输入到10输出频率转换选项

大量视频数据的处理,需要高宽带的FPGA或处理器,对系统的时钟信号也有更高的需求。针对高要求高标准的时钟信号解决需求,国产奥拉半导体推出了基于可编程四分频转换的抖动衰减和时钟合成器AU5315,适用于高清接口矩阵时钟信号分配。

应达利2016超小尺寸50MHz温补振荡器TCXO-2016,为智能电表提供精准的时钟信号

应达利的晶振TCXO-2016 50MHz(料号TC950-50.000-DRAKC)成功通过联芯通平台认证,尺寸参数为2.0mm×1.6mm,可完美应用于智能电表中。

满足AEC-Q100车规标准的实时时钟模块RA8000CE上市,支持多计算芯片时钟信号同步互联

针对汽车中需要进行时间同步的电子系统,可以采用带I2C总线的时钟模块来进行时钟信号的互联,这种总线支持多计算芯片间的通信。目前EPSON推出了一款支持I2C总线的实时时钟模块RA8000CE,这款时钟模块稳定可靠,满足AEC-Q100的车规认证标准,可以帮助汽车电子厂商设计出更现代化的电子系统,值得用户选用信赖。

胜金微电子时钟发生器SJWCH5351具备低抖动,低功耗等优势,为激光测距仪提供高精度时钟信号

随着电子产品应用的不断发展,高精度时钟芯片的需求也不断提高,同时持续地技术迭代与降低成本一直是各大芯片厂商的核心竞争力。胜金微电子自主研发的SJWCH5351系列高精度多通道时钟芯片,采用自研高端的时钟技术,在保证高性能的前提下,同时降低了系统成本、功耗和芯片面积,在消费、工业及通讯等多领域提供了最具竞争力的高端SJWCH5351系列时钟芯片。

【技术】针对时钟信号复制、格式转换、电平转换三种功能,解析扇出型时钟缓冲器的典型应用

通常讲的扇出型时钟缓冲器(Buffer),主要功能可以分为时钟信号复制,时钟信号格式转换,时钟信号电平转换。本文就由大普通信为大家针对这些功能介绍几种典型的应用场景。

锐星微邀您观展慕尼黑华南电子展!将介绍模拟时钟信号链领域全系列产品

慕尼黑华南电子展将于2024年10月14-16日在深圳国际会展中心(宝安新馆)举行;锐星微邀上下游行业伙伴莅临1G27号展位现场观展交流。

YXC恒温晶振超高精度、超高可靠性时钟信号解决方案

恒温晶振(OCXO)是一种利用恒温箱技术精确控制晶体振荡频率的高性能振荡器。通过将晶体置于一个恒温环境中,OCXO能够极大程度地减少环境温度变化对振荡频率的影响,从而提供超高的频率稳定性和精确性。OCXO广泛应用于通信、导航、测量仪器、军工、航空航天以及电力系统等高科技领域。

【应用】奥拉时钟发生器芯片AU5329B00-QMR助力多路数字可调电源设计,具有双时钟信号输入、十通道输出特性

在如今的仪器内部电源设计与工业生产中,越来越多的人选择使用多路数字可调电源来实现内部各模块的供电需求,国内一厂商在设计FPGA的时钟信号输入部分时,考虑到FPGA的全局时钟需要的驱动能力与多种时钟信号,客户选择了奥拉的时钟发生器AU5329B00-QMR。

基于6G场景对时钟信号的高要求,赛思自研出一款时钟输出抖动优于200飞秒的高性能SOC时钟芯片

新华社最新消息,我国率先搭建了国际首个通信与智能融合的6G外场试验网,实现了6G主要场景下通信性能的全面提升。基于6G场景对时钟信号的高要求,赛思设计了一种开环结构的小数分频锁相环量化噪声校准技术,并自研了高性能SOC时钟芯片产品。

【经验】抖动衰减器Si5345如何匹配选择8K单端输入时钟信号?

Silicon Labs的Si5345的输入时钟最低频率刚好是8kHz信号,通常对于这个最低频率的处理,需要特别注意。很多应用时会直接采用直流耦合的方式进行匹配,但是对于Si5345来说,这个8k不能简单直接使用DC耦合。通常8kHz时钟信号在通信吕一般由两种,一种是正常的占空比40~60%之间的时钟信号,还有一种是占空比远远小于1%的窄脉冲时钟信号,这两种时钟信号的处理实际应用是完全不同的。

YXC恒温晶振,超高精度、超高可靠性时钟信号解决方案

恒温晶振(OCXO,Oven Controlled Crystal Oscillator)是一种利用恒温箱技术精确控制晶体振荡频率的高性能振荡器。通过将晶体置于一个恒温环境中,OCXO能够极大程度地减少环境温度变化对振荡频率的影响,从而提供超高的频率稳定性和精确性。OCXO广泛应用于通信、导航、测量仪器、军工、航空航天以及电力系统等高科技领域。

登录 | 立即注册

提交评论