USB3.0 RX一致性测试,不能进入测试模式,怎么办?Debug案例3

Part 01 什么是USB3.0RX一致性测试?

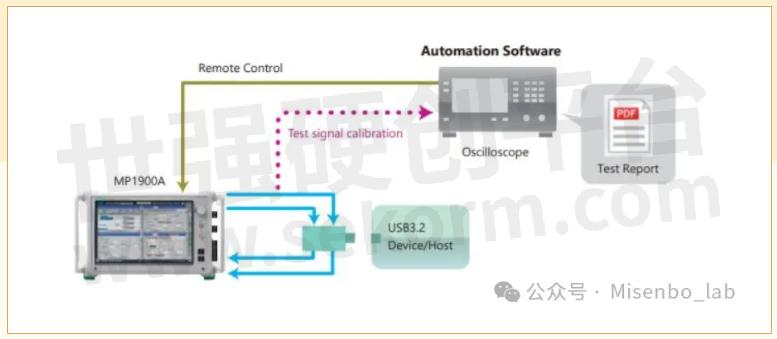

USB 3.0 RX一致性测试是对USB 3.0 (也称为SuperSpeed USB)接收端(RX)的性能进行验证的一种测试。它主要用于确保USB 3.0设备的接收端能够正确接收和处理来自发送端的数据,符合USB 3.0标准的规定。

Part 02 认识LTSSM链路训练状态机

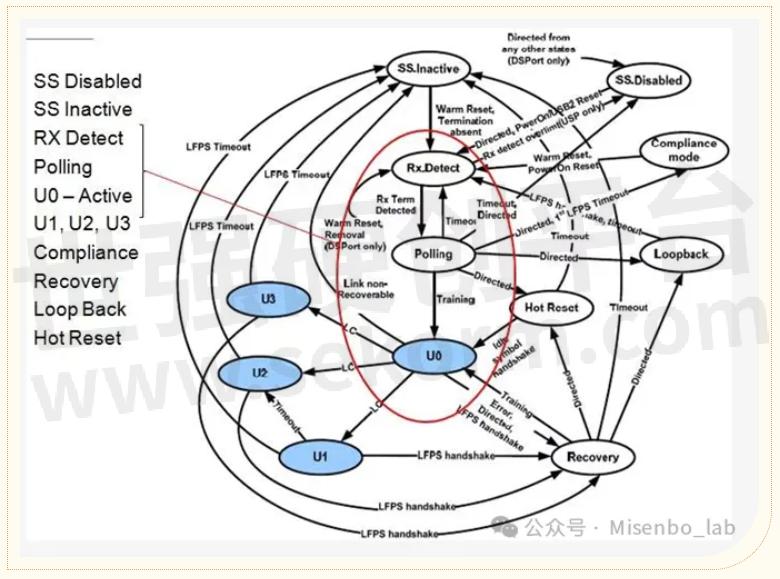

为了进行USB 3.0的 RX 测试,我们首先需要将设备配置为回环模式(Loopback Mode)。在配置之前,了解链路训练状态机(LTSSM)的概念是非常重要的。

链路训练状态机(LTSSM),即 Link Training and Status State Machine,是用于控制USB 3.0链路的连接状态和电源管理的关键机制。LTSSM定义了链路在不同操作模式下的状态,包括以下四种工作状态:

U0状态:表示超高速连接处于正常的工作状态。在此状态下,数据包正在传输或数据连接处于空闲状态。U0是USB 3.0的标准操作模式,支持正常的数据传输速率。

U1状态:为低功耗数据连接状态。此时,虽然数据连接仍然存在,但没有数据包在传输。U1状态允许超高速数据连接处于非活动状态,以节省功耗。

U2状态:也是一种低功耗模式,比U1状态进一步减少功耗。然而,设备从U2状态恢复到正常操作状态需要较长的等待时间。

U3状态:表示数据连接中断,设备进入挂起状态。这是最节能的状态,可以最大程度地减少功耗。

理解LTSSM的工作状态对于正确配置设备和执行测试非常关键。通过正确设置LTSSM的状态,可以确保设备在回环模式下的性能和稳定性。

从上图中我可以看到,在LTSSM链路训练状态机中有8种状态,分别如下:

Rx.Detect(接收检测模式)

Polling(轮询模式)

Recovery(数据恢复模式)

Host Reset(主机重置模式)

Loopback Mode(环回模式)

Compliance Mode(合规性模式)

SS.Inactive(超速模式非激活)

SS.Disabled(超速模式禁用)

其中要进行USB3.0 RX的测试一致性测试并不是直接进入Compliance Mode,而是需要进入Loopback Mode,那么如何进入该模式呢,下面我们将进行详细介绍。

Part 03

进入回环模式最常见的方法是通过信号源或者码型产生器作为Loopback master,发送特定码型序列给待测物(Loopback slave),强制其进入回环模式,期间Loopback master应发送必要的SKPs有效8b/10b数据,Loopback slave应该重传接收到的10-bit符号.

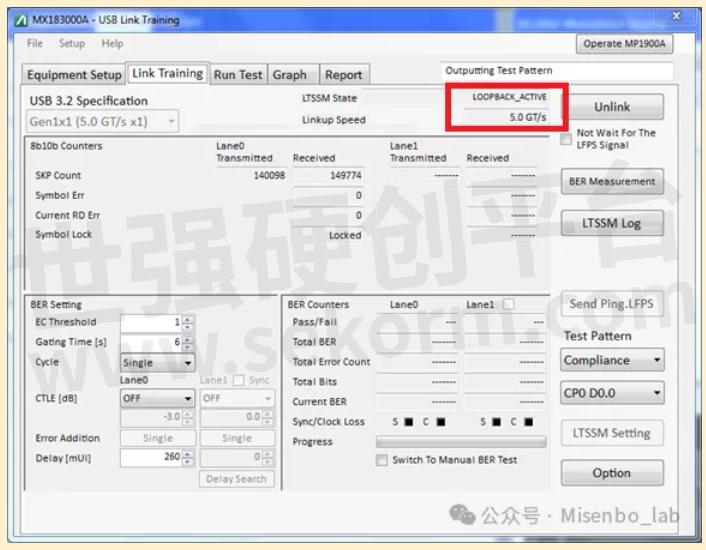

下图为使用安立MP1900A误码仪附带的MX183000A的USB Link Training进行Loopback训练时发送的数位码型产生器和参数设置。

具体解决办法

用户通过软件或者借助其它的USB3.0设备等办法诱使DUT进入一致性测试模式。

通过信号源或者码型发生器定制码型序列发送给DUT,强制其进入环回模式。

码型序列

USB3.0规范规定进入环回模式以及进行误码测试需要的码型序列为:

给被测DUT上电;

发送2ms的Polling LFPS;

发送65536 TSEQ;

发送256 TS1;

发送256 TS2(Loopback位设置为1);

开始发送码型并计算BER;

在进行误码计算之前需要先发送2ms的BDAT;

DUT必须无误码的运行3x109symbols或者3x1010 bits的BDAT码:且每354 symbols插入一个 SKP;

下图所示为DUT顺利进入环回模式,连接状态处于Loopback.Active,在该模式下即可进行USB3.0RX的一致性测试。

淼森波实验室服务简介:

主要业务:芯片物理层验证测试、芯片验证测试的Demo板研发、AI加速卡测试、服务器测试、汽车智能座舱测试、高速信号SI/PI仿真、硬件产品故障Debug、硬件项目研发服务;仪器租赁;硬件工程师培训 。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由雪飘梦飞转载自Misenbo(淼森波公众号),原文标题为:【测试那点事儿】USB3.0 RX 一致性测试,不能进入测试模式,怎么办?Debug 案例3,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【经验】解析如何识别不同工作速度的USB3.0设备

USB3.0设备在开发之前就已经确定其工作模式:低速、全速还是高速。本文步步精科技将为你解析如何识别不同工作速度的USB3.0设备。

DP1.4眼图信号质量差解决方案详解

眼图测试是验证信号质量的基本方法。通过观察信号眼图的眼宽和眼高,以及是否触碰到Eye Mask,可以判断源设备输出的信号是否足以被接收设备识别。此外,数字信号的眼图还包含丰富的信息,能够反映数字信号的整体特性,帮助评估信号质量。因此,眼图分析是数字系统信号完整性分析的关键之一。 想要解决DP1.4眼图质量差的问题,需要从多个方面进行深入分析。

解析LPDDR4硬件设计及测试注意事项

LPDDR4(Low Power Double Data Rate fourth generation)是一种低功耗的存储器标准,用于移动设备和便携式应用。本文中Misenbo为大家介绍LPDDR4硬件设计及测试注意事项。

电科星拓发布PCIE转USB产品,将PCIe2.0通道转换为USB3.0接口,广泛应用于服务器、个人PC及工业设备等产品

电科星拓自主研发的PCIe转USB芯片(XUSB系列)已成功实现规模化量产。该系列芯片是一种用于将PCIe2.0通道转换为USB3.0接口的芯片,实现PCIe设备与USB3.0设备之间的数据传输。最多支持1x 5Gb/s PCIe2.0通道、4x5Gb/s USB3.0接口,USB可以协商支持480Mb/s、12Mb/s和1.5Mb/s,芯片支持从外部flash、系统BIOS或者系统软件加载固件。

详解DDR技术内核 及Layout注意事项

这些是一些常见的DDR走线规则,当然,具体的规则可能因DDR版本、芯片厂商和PCB设计要求而有所不同。在进行DDR走线设计时,务必参考相关的DDR规范和芯片厂商的建议,以确保良好的信号完整性和性能。

DDR芯片的PCB设计要点

DDR PCB布局设计需要考虑诸多因素,包括DDR规格、频率、时钟速度等。因此,确保与DDR芯片厂商的规格和设计要求保持良好的沟通和协作,是非常重要的。

解析DDR信号完整性测试内容、技巧及注意事项

DDR(双数据速率)信号完整性测试是对DDR系统中信号传输的稳定性和准确性进行验证的过程。那么关于DDR信号完整性测试的内容、技巧及注意事项您有了解吗?本文将为您进行详细介绍。

10G的SFP+_Rx如何测试?干货供收藏

10G的SFP+_Rx测试技术要求及方法介绍,SFP+_Rx测试是确保光纤模块性能的重要环节,通过系统化的测试流程和方法,可以有效验证设备的接收性能,保障通信的可靠性与稳定性。

【经验】淼森波实验室DDR测试案例,如何区分DDR1,DDR2,DDR3,DDR4还有DDR5?

DDR1、DDR2、DDR3、DDR4和DDR5都是不同类型的同步动态随机存取存储器,它们提供了不同的性能和带宽,并不断演进和发展。 都是不同类型的内存规格,它们的速度、带宽、工作电压和能耗等方面都有所不同,DDR5 内存规格最高,速度最快,带宽最宽,能耗最低。

SI/PI信号完整性测试

SI/PI信号完整性测试的重要性SI(Signal Integrity)和PI(Power Integrity)信号完整性测试在现代电子设备设计和制造中非常重要。以下是SI PI信号完整性测试的重要性、SI/PI信号完整性测试内容和案例。

HDMI闪屏故障的成因及相应的解决方法

在现代多媒体设备中,HDMI(高清多媒体接口)是连接显示器与电脑、游戏机等设备的主流方式。然而,许多用户在使用HDMI连接时会遇到闪屏现象。本文Misenbo将探讨该问题的成因及相应的解决方法,帮助用户快速排查和修复问题。

LVDS闪屏的原因及解决办法

LVDS(低电压差分信号)闪屏问题通常指的是显示屏在使用过程中出现闪烁或不稳定的现象。本文将为您介绍 LVDS(低电压差分信号)闪屏的原因及解决办法。

【测试那点事儿】信号的过冲咋处理?-Debug 案例1

信号过冲(Overshoot)是指在数字信号传输过程中,信号幅度暂时超过其稳态值的现象。这通常发生在信号快速切换时,如从低电平到高电平或从高电平到低电平的过渡期间。

MIPI接口闪屏怎么解决?

在现代移动设备中,MIPI(移动行业处理器接口)因其高速串行数据传输能力被广泛应用于显示屏和摄像头模块。然而,用户在使用这些设备时可能会遇到闪屏现象,即图像频繁闪烁或不稳定。本文将深入探讨MIPI接口闪屏的成因及解决方案。

【经验】解析HDMI Sink一致性测试及眼图测试案例

HDMI测试主要有Source端测试、Sink端测试、单项眼图信号质量测试。Source端测试已介绍、接下来淼森波实验室分享HDMI的Sink端一致测试、Sink端眼图文测试。

服务

根据用户的接口模块,使用是德示波器及夹具查看实时眼图演示,测试USB/MIPI/DDR/SATA/HDMI协议,支持最高到1.2GHz的实时眼图协议测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

可根据用户的wifi模块,使用无线连接测试仪MT8862A,测试IEEE802.11a/b/g/n/ac (2.4Ghz和5Ghz)设备的TX、RX射频特征,输出测试报告。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论