Jitter简介及仿真案例分析

在高速信号传输系统中,Jitter是指信号到达时间的不可预测变化,这种变化可能会导致信号失真、数据错误以及系统性能下降,尤其是在高频应用中,如数据通信、视频传输和高速数字电路,Jitter直接影响着信号的完整性和系统的可靠性。本文巨霖科技来与大家分享Jitter简介及仿真案例分析,希望对各位工程师朋友有所帮助。

Jitter的定义及优化策略

Jitter的定义

理想的数字信号的时钟周期不会产生变化,每个数据UI(Unit Interval, 即每个bit的时间长度)也都严格相等,但在真实世界里,由于热噪声和各种因素的影响,时钟或数据的边沿往往存在不确定性,其真实位置和理想位置之间的偏差,就是所谓的抖动。当时钟信号或数据信号存在较大的抖动时,接收端在识别信息时就会出错,导致信息传递出现“误码”(Bit Error)。

时序抖动的来源多种多样,数字信号中总抖动的大小很大程度上取决于不同噪声源的影响程度。依据不同噪声源引起的时序抖动的概率密度函数特征,可以将时序抖动分为确定性抖动(deterministic jitter, DJ)和随机抖动(random jitter, RJ)两大部分。确定性抖动又可以分为周期性抖动(periodic Jitter,PJ)和数据相关性抖动( data dependent jitter, DDJ),周期性抖动由由系统时钟或周期性干扰引起,通常表现为可预测的模式,由于任何周期波形都可以分解成傅里叶序列的谐波相关正弦曲线,这类抖动又被称为正弦曲线抖动(sinusoidal jitter,SJ)数据相关性抖动与数据的码型有关,数据当前比特位的波形会受到之前几个比特位跳变时刻的影响。占空比失真(duty cycle distortion, DCD)和符号间干扰( inter-symbol interference, ISI)是数据相关性抖动的两个主要组成部分。随机抖动由随机噪声或信号干扰引起,无法预测,通常通过统计方法来分析,随机抖动符合高斯正态分布。随机抖动的峰峰值和测量的样本数(总bits数量)息息相关,理论上只要测量的时间足够长,随机抖动可以增加到无穷大。抖动分析时,随机抖动的测量值一般用RMS值来表示,即正态分布的σ值。

Jitter的优化策略

在实际电路中Jitter主要由以下几个方面引起:时钟源本身的不稳定性带来的抖动,电路设计中的缺陷:如电源噪声、地弹效应等,都可能引起信号抖动。信号传输过程中,信号的反射、串扰,信号经历衰减和噪声干扰,会导致信号波形畸变,进而产生Jitter。当采样时钟与数据信号之间的相位差发生变化时,会导致采样点偏离理想位置,产生Jitter。

为了降低接收端的Jitter,可以采取以下措施:选用低jitter时钟源,确保时钟信号的稳定性。使用适当的滤波器和去耦电容,减少噪声。使用高性能的连接器和电缆,减少传输中的信号损失确保信号路径短且直接,降低信号损耗。使用差分信号传输,减少共模噪声影响。加强信号滤波和噪声抑制技术,降低噪声对信号的影响。精确匹配阻抗,减少反射和信号干扰。改进时钟恢复算法,提高时钟恢复精度。使用锁相环(PLL)等同步技术,保持采样时钟与数据信号的同步。

使用SIDesigner进行实际应用

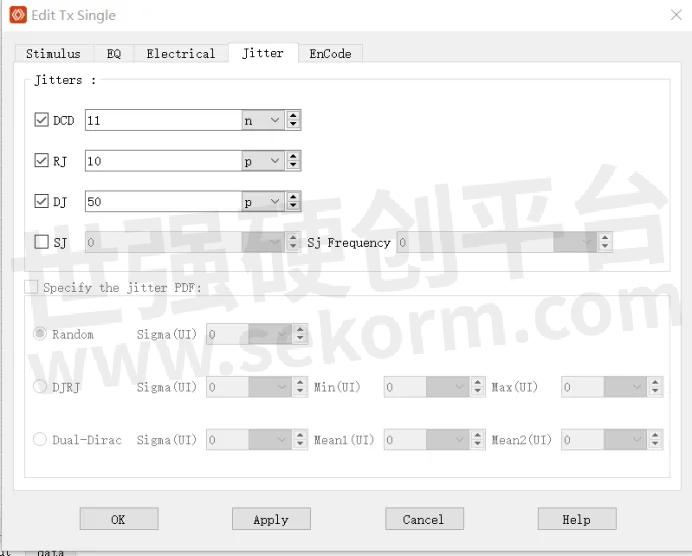

在仿真中,可以主动加入Jitter,在通过调整时钟源的稳定性、优化电路设计、改善信号完整性等方法来降低Jitter,达到信号的高质量传输。在巨霖的SIDesigner中,可以在发射端和接收端添加Jitter。

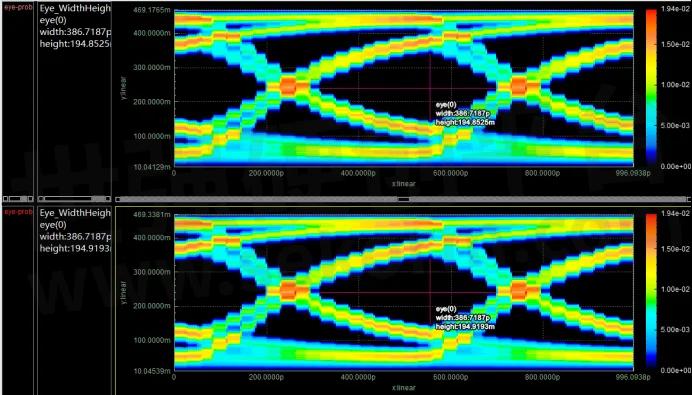

添加完Jitter进行仿真,通过眼高眼宽的测量对比前后眼图差异。

综上可知,通过巨霖SIDesigner进行Jitter仿真可帮助工程师更好地理解和控制信号在传输过程中的不稳定因素,为信号的高质量传输提供可靠支持。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由ll转载自巨霖科技公众号,原文标题为:Jitter简介及仿真案例分析,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

高速信号仿真中的FFE均衡技术原理及SIDesigner仿真案例分析

我们就一起来看看FFE均衡技术。前馈均衡器(FFE)是一种用于信号处理的线性均衡技术,类似于有限脉冲响应(FIR)滤波器。它通过放大或衰减信号的特定频率成分来补偿信号在传输过程中的衰减。FFE 电路通过均衡器抽头调整滤波器系数,以增强或减弱信号的高频成分。抽头的数量决定了滤波器的复杂性和补偿通道损伤的能力。

高速信号中DFE均衡技术原理、应用及SIDesigner仿真案例分析

随着数据速率的不断提高,DFE均衡技术也在不断发展和优化。多抽头DFE技术也在逐步得到研究和应用,以应对更高速度、更复杂信道环境下的通信需求。使用巨霖SIDesigner软件进行典型应用场景channel-DFE-Sim仿真结果:能够有效地抑制信道引起的失真和干扰,提高信号的可靠性和稳定性。

单端S参数到混合模式S参数的仿真与转换

S参数(Scattering Parameters),也称为散射参数,是描述多端口网络电气特性的基本工具。它们主要用于表征网络的反射和传输特性,提供关于网络性能的关键信息,如增益、损耗、匹配度等,在射频(RF)、微波工程、高速数字电路设计以及通信系统中广泛应用。

巨霖科技携EDA核心产品亮相CCIC 2024并发表《高精度通用EDA平台,助力探索未来世界》重要演讲

6月20日-21日在青岛胶州举办了“第21届中国通信集成电路技术及应用大会暨上合新区集成电路产业创新发展大会”(CCIC 2024)。 作为行业领军企业受主办方邀请巨霖科技携带其核心产品参展出席本次大会并发表了重要演讲,成为了本次活动的亮点之一。在展会现场,巨霖的工程师们向与会者详细介绍了巨霖“高精度EDA通用电路仿真平台” 包含的多款核心产品及其技术优势。

时域反射计(TDR)仿真简介

TDR全称为时域反射计(Time Domain Reflectometry),是一种基于时域的阻抗测量方法。它通过测量电压来获取阻抗信息,由信号发生器、探头和采样示波器三部分组成。作为PCB厂商和信号完整性工程师常用的阻抗测量仪器,TDR比频域测量(VNA)更加简单快捷,省去了复杂的校准过程,并且价格更为实惠。因此,在高速数字电路领域得到广泛应用。

一文解析S参数转宽带SPICE模型仿真

S参数,即散射参数,是用于描述传输通道频域特性的一种参数,广泛应用于射频和微波领域。本文中巨霖科技来为大家介绍S参数转宽带SPICE模型仿真,希望对各位工程师朋友有所帮助。

IBIS功能简介及仿真案例分析

本文中巨霖科技将为大家介绍IBIS功能,并通过SIDesigner仿真工具为例,给大家介绍如何选择并设置IBIS模型。

传输线简介及SIDesigner仿真案例分析

巨霖产品的模型库中含有多种传输线模型:理想传输线、耦合理想传输线、还有上述提到的传输线类型,并计划增添有损传输线模型,并增添能修改介质的隔离度等复杂功能。本文介绍传输线简介及仿真案例分析。

IBIS文件中的Series Model简介及设计仿真实例

本文详细了解一下文件中的一类特殊模型——Series Model。以巨霖科技的信号完整性仿真工具SIDesigner为例,查看如何在信号完整性分析中使用Series Model。

IBIS-AMI模型简介及巨霖科技SIDesigner仿真案例分析

巨霖的SIDesigner软件提供了IBIS-AMI模型的仿真功能。工程师可以对电子系统进行全面的系统性能评估、优化系统可靠性及稳定性,加速产品研发、迭代过程。

使用SIDesigner进行高速信号仿真中的CTLE均衡仿真分析

CTLE是一种在高速信号传输中常用的均衡技术。它主要用于补偿由于信道引起的信号失真,特别是在高频信号传输过程中,信号可能会因为传输媒介的特性而受到衰减、失真和时延的影响。巨霖SIDesigner是一款基于图形化交互界面的信号完整性仿真工具,可以在该平台上进行案例的仿真。

巨霖工具SIDesigner仿真软件,对统计眼图进行查看和测量,确保数据传输和系统的可靠性

介绍巨霖工具SIDesigner统计眼图的仿真测量实例。

S参数去嵌:在高速电路设计与测试中的精确化探索

在高速电路设计与测试领域,S参数(散射参数)扮演着至关重要的角色。然而,由于实际测试环境中存在的夹具、连接线等非电路元件的影响,直接测量得到的S参数往往无法真实反映电路本身的性能。因此,S参数去嵌技术的出现,为高速电路设计师们提供了一种有效的方法,用于从测量数据中剥离非电路元件的影响,从而获取更为准确的电路性能参数。

铜箔粗糙度及巨霖SIDesigner仿真应用

巨霖SIDesigner可以提供高速信号完整性解决方案,支撑客户当下和未来高速设计仿真需求。通过简单易用的操作界面,用户可以方便地进行铜箔粗糙度建模,快速评估铜箔粗糙度对传输线和系统SI的影响,提早发现设计隐患,可靠评估系统SI设计方案,为未来产品化落地打下坚实基础。

电子商城

现货市场

登录 | 立即注册

提交评论