HqFpga软件使用小技巧二则

智多晶EDA工具HqFpga软件经过更新和改进,增加了一些实用的小技巧,旨在帮助用户更便捷地操作软件并提升工作效率。

01 Hq使用小技巧

在Windows系统中Hq通过File_list.f快速导入.v文件

1.创建脚本文件

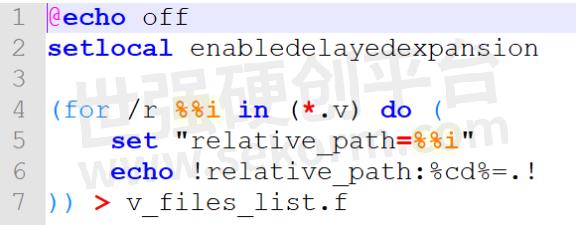

首先,新建一个txt文本文件,将特定的tcl内容(如图1所示)编辑到新建的txt文件中,并将此txt文件重命名为.bat的批处理文件。

图1:File_list.bat脚本

2.放置脚本

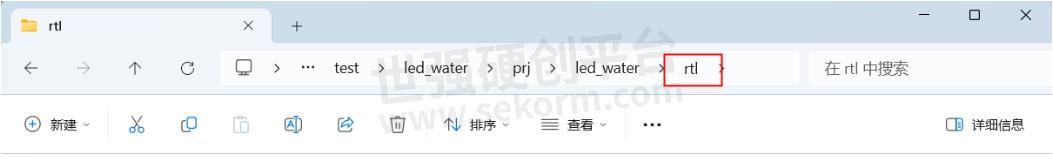

将该.bat文件放入到rtl文件夹的最顶层。如果你的所有.v文件都存放在rtl文件夹及其子文件夹中,那么.bat文件就应当被放置在rtl文件夹的根目录下(如图2所示)。

图2:所有.v文件所在的文件夹最顶层

3.运行脚本并生成文件列表

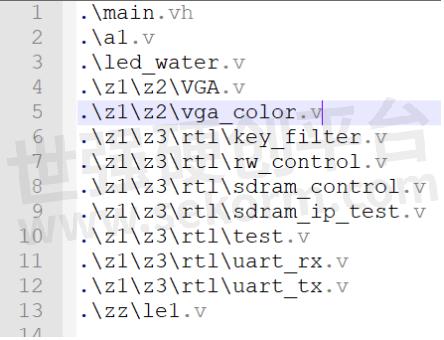

运行.bat脚本,它会自动搜索并列出.bat文件所在文件夹及其所有子文件夹下的所有.v文件的相对路径和名称信息,然后将这些信息导入到一个名为“v_files_list.f”的文件中(生成的.f文件如图3所示,你也可以在.bat文件的最后一行自定义生成的.f文件的名称,)。

图3:生成的.f文件例子

4.通过Hq导入文件列表

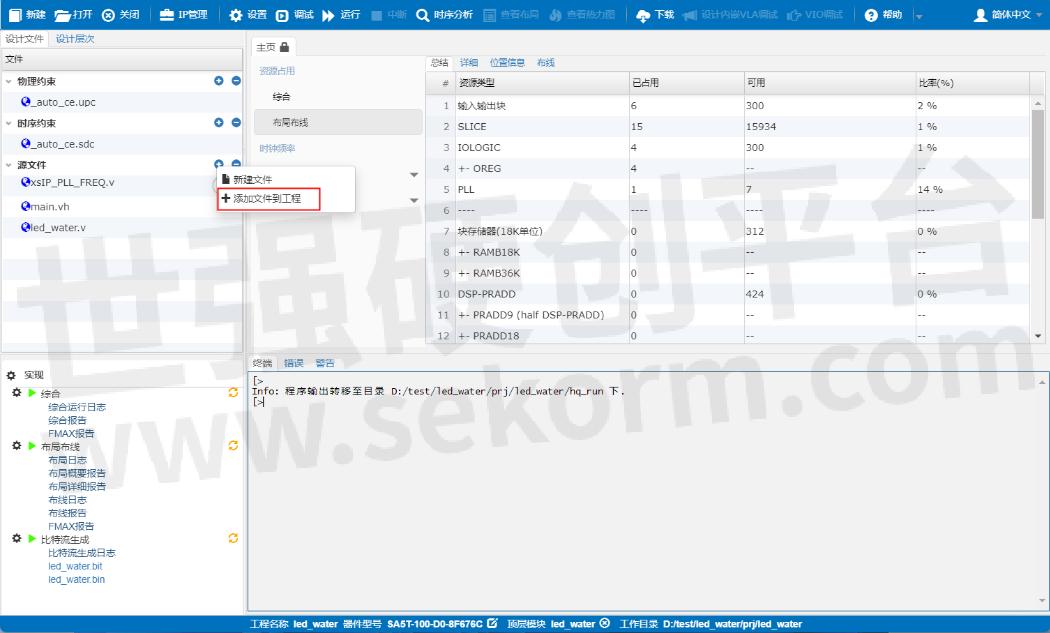

最后,在Hq软件中,通过“添加文件到工程”功能选择这个生成的.f文件,就可以一次性地将rtl文件夹及其子文件夹下的所有.v文件全部导入到工程中(如图4所示)。

图4:通过Hq添加.f文件

注:这一技巧在官网的“服务与支持”栏目下的“产品讲解”中“软件”视频讲解部分也有详细介绍。

02 Hq使用小技巧

Hq软件对宏定义的支持

在使用Hq时,你可能会用到宏定义来管理一些常用的参数或设置。Hq软件提供了多种方式来支持宏定义的使用。

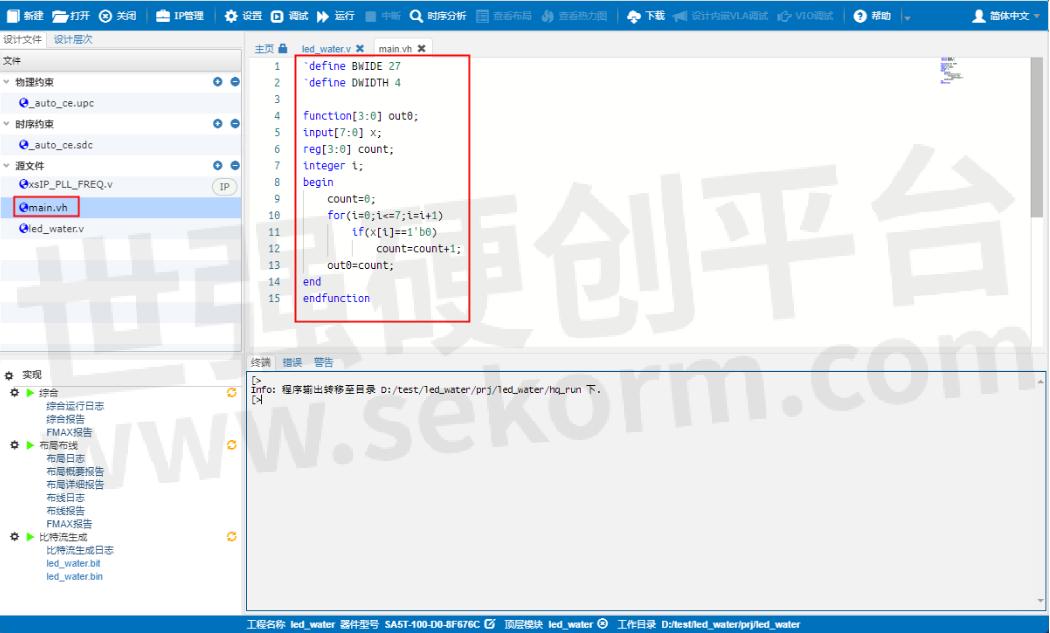

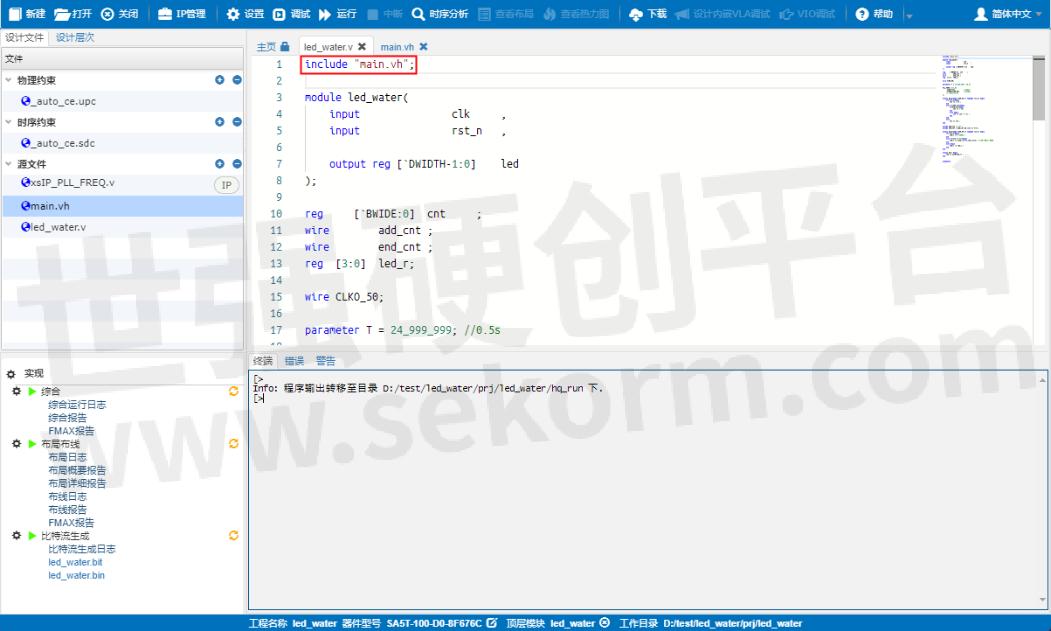

第一种方式:创建一个名为main.vh的文件(Hq软件支持.vh、.h、.v等多种文件后缀,这里以.vh为例),并在该文件中定义你需要的参数(如图5所示)。然后,在需要使用这些参数的模块开头,通过include语句引入这个main.vh文件,就可以在模块内部调用这些参数了(如图6所示)。

图5:定义参数文件main.vh

图6:模块内调用定义好的参数

第二种方式:将main.vh文件放置在“源文件”列表的最顶部位置。这样,在模块内部调用宏定义时,就无需在每个模块开头都进行include操作了(如图7所示)。

图7:main.vh放到“源文件”下的第一位

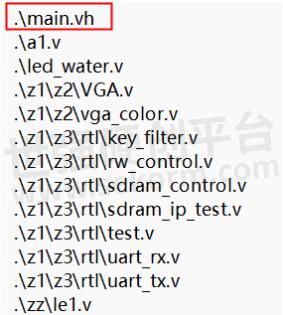

第三种方式:在通过.f文件导入工程文件之前,将main.vh文件的相对路径和名称信息添加到.f文件的最顶部位置(如图8所示)。这样,在导入.f文件后,main.vh文件就会自动被放置在“源文件”列表的最顶部位置。需要注意的是,在使用这种方式导入main.vh文件之前,应确保“源文件”列表中没有其他工程文件存在;如果已有其他文件存在,则需先将其移除后再进行导入操作。

图8:将main.vh的相对路径和名称信息编辑到.f文件的第一位

注:这一技巧同样可以在官网的“服务与支持”栏目下的“产品讲解”中“软件”视频讲解部分找到相关介绍。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由samsara转载自智多晶官网,原文标题为:HqFpga软件使用小技巧二则,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关研发服务和供应服务

相关推荐

【经验】如何在Modelsim上仿真智多晶FPGA IP core

对于安装了智多晶FPGA编译软件的小伙伴们来说,也许会关注如何调用Modelsim来仿真Hqfpga软件中自带的IP,本文笔者将分步骤带大家走一遍流程,分编译库文件、仿真IP core来介绍。

【经验】HqFPGA中如何对设计进行物理约束?

物理约束是FPGA软件开发过程中不可或缺的步骤,决定了HDL代码映射到硬件芯片上的效果。本文以一个流水灯工程为例讲解在设计中做物理约束的整个过程。约束语句中的pin脚号是根据西安智多晶FPGA开发板上连接LED的pin号定,实际应用中应根据需求设定。约束文件编辑好后就可以对设计进行综合,布局/布线。

【经验】智多晶FPGA开发环境HqFPGA海麒在Windows系统中的搭建

集成开发环境在FPGA开发过程中扮演着举足轻重的作用,优秀的开发软件能够减少设计者的工作量,降低设计实现的难度,让项目更快更好地部署。本文介绍一款来自国产厂商智多晶的FPGA开发软件HqFPGA,中文名“海麒”。软件界面的风格非常简约,并且设计流程一目了然,能够让初学者轻松上手。

【产品】基于28纳米技术工艺的Seal 5000系列 FPGA,20K到200K的查找表逻辑单元

西安智多晶推出的Seal 5000 FPGA同样采用正向设计,芯片软件设计流程和ISE/Quartus II/Diamond 类似。智多晶的芯片架构可以接受ISE和Quartus II的代码,使用自主研发的FPGA开发软件“HqFpga”, 完成综合、布局布线、时序分析、配置编程和片内逻辑分析。智多晶的Seal 5000系列FPGA芯片和Virtex-7系列的FPGA芯片相容。

采用28nm先进工艺,国内首颗高性价比带Arm Cortex-M3 FPGA,助力客户战略升级

描述- 智多晶,成立于2012年,专注于可编程逻辑电路器件技术研发,提供高集成度、高性价比的FPGA、IP核、软件设计工具及系统解决方案。公司拥有自主开发的HqFpga软件,支持RTL-to-FPGA全流程。产品线涵盖Shark、Seal、Sealion、Seagull等多个系列,满足不同应用需求。Seal5000系列采用28nm工艺,性能、功耗和资源配置达到国内领先水平。

型号- SL2D-25E,SA5-325,SA5Z-30-D1,SEAL5000 系列,SEAL5000 30K,SG1064,SL2D-25V,SL2S-12V,SEAGULL-1000,SG1128,SL2S-25E,SA5-100,SL2-12E,SA5-200,SL2-25E,SL2S-12E,SL2-7E,SEAL-5000,SL2-12V,SL2-5E,SEALION2000 系列,SL2-25V,SL2S-25V,SEAGULL 1000系列,SG1256,SEALION-2000

HqFpga FT 软件版本下载说明

描述- 西安智多晶微电子有限公司发布的HqFpga FT软件版本下载说明,介绍了HqFpga FPGA开发系统的特点、版本信息、下载流程和注意事项。HqFpga是一款集成FPGA实现功能的开发系统,支持SEALION和SEAL系列FPGA器件。软件提供稳定和测试版本,用户可根据需求下载。

HqFpga V2 软件版本下载说明

描述- HqFpga V2 软件版本下载说明,介绍了西安智多晶微电子有限公司开发的FPGA开发系统HqFpga V2。该软件支持SEALION和SEAL系列FPGA器件,集成了综合、布局、布线等功能,并提供一键式运行模式。软件版本包括稳定版和测试版,支持Windows 64和Linux系统。下载说明详细介绍了软件的版本更新、下载链接、文件说明以及历史版本。

西安智多晶(XIST)FPGA软件开发系统用户手册--适用HqFpga软件版本V2.6.3 及以上版本

描述- HqFpga 是西安智多晶微电子有限公司(XIST)开发的FPGA开发系统。HqFpga目前支持SEALION系列FPGA器件。

HqFpga V3 软件版本下载说明

描述- HqFpga V3软件版本下载说明,介绍了西安智多晶微电子有限公司开发的FPGA开发系统HqFpga V3的下载和使用。该软件支持SEALION和SEAL系列FPGA器件,集成了综合、布局、布线等功能,提供一键式运行模式。软件分为稳定版和测试版,支持Windows和Linux系统,提供多种下载文件,包括不同界面和系统版本的安装包。用户可从官网下载最新版本或历史版本。

智多晶EDA工具HQfpga软件可进行迭代式时序优化

智多晶的EDA工具HQfpga软件对于资源占比较高且时序难以跑出收敛的工程,可以使用循环迭代式(loop/iterative)进行时序驱动优化(tdo–timing driven optimization),使工程可以以不同的优化策略跑出多个时序收敛的结果。

我想问一下,你们代理的西安智多星fpga,IP核都有哪些,有资料介绍吗?IP核都免费使用吗?

您好,目前智多晶平台提供DSP、BlockRAM、FIFO、PLL等常用IP核,IP核全部免费使用。请参考:西安智多晶(XIST)FPGA软件开发系统用户手册--适用HqFpga软件版本V2.6.3 及以上版本西安智多晶(XIST)Sealion(海狮)2000/2000s系列FPGA产品数据手册

DSP_IP 用户指南

描述- 本指南介绍了西安智多晶微电子有限公司提供的DSP IP模块,包括FFT、DSP\_MULT、DSP\_MULTADDSUB、DSP\_MULTADDSUBSUM等。用户可通过HqFpga EDA工具配置这些模块,并生成、例化到用户逻辑中。指南详细说明了每个模块的配置参数和功能,如数据位宽、数据类型、数据源、复位模式等,以帮助用户根据需求进行灵活配置。

这个FPGA现在有哪些主流客户在用了,FPGA相关的EDA工具是否有介绍

合作企业包括:汇川技术、广州数控、中兴通信、诺瓦科技等知名企业。 EDA开发软件HqFpga,2017年收购北京飘石公司。HqFpgaTM – RTL-TO-FPGA软件在单一的可执行文件中集成了RTL to-FPGA的所有功能。各功能模块共享统一的数据模型、器件模型及时序分析引擎,从而得以完成简单、快速、高效及优化的FPGA开发。HqFpga 在单一的可执行文件中集成了从综合、布局、布线等所有 FPGA 实现功能。HqFpga 在同一可执行环境下所集成各项功能可以共享所有的信息,例如统一的数据模型、时序分析结果等,HqFpga 还提供一键式(Push-Button)的运行模式,并提供多种界面语言,方便用户完成简单、快速、高效及优化的 FPGA 开发。HqFpga的另一革命性特点在于提供开放式、平台化的解决方案,即第三方厂商可以在HqFpga的基础上进行二次开发,构建厂商自己的专用系统,极大地简化FPGA厂商软件开发流程。 下载地址:http://www.uptops-dt.com/col.jsp?id=128

【经验】如何使用HqFPGA软件对设计进行时序约束?

时序约束是FPGA软件开发过程中不可或缺的步骤,HqFPGA是西安智多晶自主开发的FPGA开发软件,在HqFPGA中目前支持UI界面(约束编辑器)对时钟、信号等关键路径进行时序约束,也支持约束文件导入。本文介绍如何使用约束编辑器添加时序约束,以一个流水灯工程为例讲解在设计中做时序约束的整个过程。

BlockROM_IP 用户指南

描述- 本指南介绍了西安智多晶微电子有限公司的BlockROM_IP核,包括其不同工作模式(单端口、伪双端口、真双端口和ROM模式)的配置和使用方法。指南详细说明了每种模式的端口描述、时序图以及如何通过HqFpga软件进行初始化和数据导入。此外,还提供了相关文档列表和免责声明。

电子商城

服务

世强深圳实验室提供Robei EDA软件免费使用服务,与VCS、NC-Verilog、Modelsim等EDA工具无缝衔接,将IC设计高度抽象化,并精简到三个基本元素:模块、引脚、连接线,自动生成代码。点击预约,支持到场/视频直播使用,资深专家全程指导。

实验室地址: 深圳 提交需求>

提供稳态、瞬态、热传导、对流散热、热辐射、热接触、和液冷等热仿真分析,通过FloTHERM软件帮助工程师在产品设计初期创建虚拟模型,对多种系统设计方案进行评估,识别潜在散热风险。

实验室地址: 深圳 提交需求>

登录 | 立即注册

提交评论