灿芯半导体DDR4 IP在40纳米工艺上实现了2400 Mbps速率

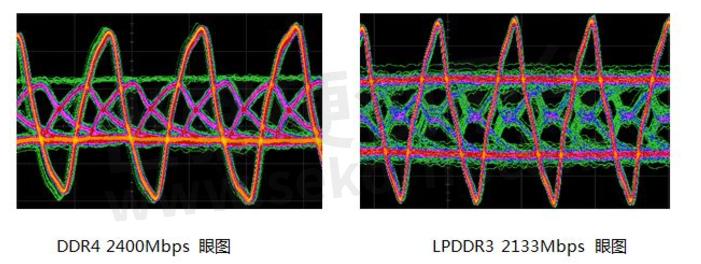

中国,上海—2016年11月15日—灿芯半导体(上海)有限公司(以下简称“灿芯半导体”),今天宣布其YouPHY-DDR系列DDR4,DDR3/LPDDR3子系统通过了40纳米低漏电工艺流片验证。根据实测数据,YouPHY-DDR子系统为客户带来了低功耗、小面积的高速DDR方案,其传输速率成功地在DDR4标准上实现了2400 Mbps,在DDR3/LPDDR3标准上实现了2133 Mbps。

YouPHY-DDR是灿芯半导体带来的一个完整DDR解决方案,不仅包括DDR控制器(controller),PHY和I/O,而且包括特别开发的调试和测试软件,是一个完整的子系统。该方案是基于从40纳米到28纳米的各种先进工艺而开发,可支持DDR3、LPDDR3、DDR4和LPDDR4等应用,支持从2133Mbps 到3200Mbps的数据传输速率。其特有的动态自校准逻辑(DSCL)和动态自适应比特校准技术(DABC),可自动补偿芯片级、封装级、板级和存储器级别的工艺/电压/温度(PVT)波动而产生的器件性能差异,以及实现传输字节间的斜交自动补偿。YouPHY-DDR可以为客户提供高性能、低功耗、较小面积和较快上市时间的DDR接口IP方案。

基于此技术,灿芯半导体将会持续为客户提供先进的高性能、高可靠性的DDR接口IP解决方案,其可实现3200 Mbps传输速率的28纳米DDR/LPDDR4将会很快通过流片验证。我们相信YouPHY-DDR将会是您DDR接口IP的合适方案选择。

关于灿芯半导体

灿芯半导体(上海)有限公司是一家ASIC设计服务公司,定位于90nm/65nm/40nm/28nm 及更高端的SoC设计服务,灿芯半导体为客户提供从源代码或网表到芯片成品的一站式服务,并致力于为客户复杂的ASIC设计提供一个低成本、低风险的完整的芯片整体解决方案。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由扶摇转载自灿芯半导体官网,原文标题为:灿芯半导体宣布其DDR4 IP在40纳米工艺上实现了2400 Mbps速率,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

灿芯半导体运用Cadence®数字设计实现和Signoff工具,提升了4个SoC设计项目的质量并缩短了上市时间

灿芯半导体(Brite Semiconductor Corporation)运用Cadence® 数字设计实现和signoff工具,完成了4个28nm系统级芯片(SoC)的设计,相比于先前的设计工具,使其产品上市时间缩短了3周。通过使用Cadence设计工具,灿芯半导体的设计项目实现了提升20%的性能和节省10%的功耗。

灿芯半导体推出由USB控制器和PHY构成的USB IP完整解决方案,助力系统制造商设计高质量的ASIC/SoC产品

2022年9月9日,一站式定制芯片及IP供应商——灿芯半导体日前宣布推出可用于ASIC/SoC的USB IP完整解决方案。该解决方案由一系列USB控制器和PHY构成,可以助力系统制造商、个人电脑原始设备制造商和IC公司等设计高质量的ASIC/SoC产品。

灿芯半导体ONFI 4.2 IO及物理层IP采用全数字设计,并通过流片验证测试

定制芯片设计、生产及IP授权的高新技术企业——灿芯半导体ONFI 4.2 IO及物理层IP,该IO支持SDR/NV-DDR/NV-DDR2 1.8V, NV-DDR3 1.2V, 该物理层IP采用全数字设计,具有低功耗、面积小等特点。ONFI IP已通过流片验证,将助力客户快速实现量产。

安全芯片设计/流片/封装

提供从安全芯片架构设计到芯片成品的整体解决方案,包括厂家的选择、工艺节点的应用、IP的提供、后端设计、封装和测试方案与逻辑等方面,工艺节点主要包含180nm/130nm/110nm/90nm/65nm/55nm/40nm/28nm/14nm/等节点。

服务提供商 - 灿芯半导体 进入

灿芯半导体上线芯片设计/流片/封装服务

灿芯半导体的芯片设计、流片、封装服务已于8月上线平台,并支持IP采购和定制化服务。用户可以在平台定制14nm先进工艺的芯片、提交流片生产与对应的封测服务需求、采购灿芯自主开发的IP,包含YouPHY/YouRF/YouSiP/YouAnalog/YouIO/YouSecure/YouCrypto等七大系列,及其第三方合作伙伴的IP,有特殊需求的IP也可以进行定制。

面向低功耗智能互联设备,灿芯半导体推出音频/语音DSP参考设计平台

该音频/语音DSP参考设计平台基于CEVA-TeakLite-4 DSP核开发,融合了多种传感器技术、信号处理技术和无线互联技术,旨在为手持移动设备、可穿戴设备和智能家居单芯片(SoC)设计提供原型参考,降低设计风险,加快上市时间。

【产品】灿芯半导体新推出xSPI/Hyperbus™/Xcella™控制器和PHY整体解决方案

日前,灿芯半导体日前宣布推出xSPI/Hyperbus™/Xcella™存储器(闪存、PSRAM、MRAM 等)的控制器和PHY解决方案,适用于客制化SoC;采用自动流量控制和反馈采样技术等创新技术来达到小面积和高速率。

灿芯半导体发布通用高性能小数分频锁相环IP及相关解决方案,支持24bits高精度小数分频

灿芯半导体(上海)股份有限公司宣布成功研发出一款通用高性能小数分频锁相环(fractional-N PLL)IP,支持24bits高精度小数分频,最高输出频率4.5Ghz,另外还支持扩频时钟(SSC)功能,可以为客户提供多功能的小数分频 PLL解决方案。

灿芯半导体多速率Serdes IP方案,具有优异性能、面积和功耗

灿芯半导体为客户提供1.25-12.5Gbps多速率SERDES IP方案。该方案平滑地集成了多SERDES通路,具有同级产品中最优的性能、面积和功耗。可编译的PHY可以支持众多主流接口。

【产品】300mA输出线性稳压器OCP1303/OCP2820 ,IQ典型耗电38uA,工作电压2.2V-5.5V

灿瑞科技推出的 0CP1303 | 0CP2820 300mA输出线性稳压器,具有简单外围,仅3个陶瓷滤波电容;宽幅工作电压,工作电压: 2.2V-5.5V;静态低功耗,1Q典型耗电38uA;高输出电流,提供高达300mA输出电流。

灿芯半导体与成都纳能、芯启源合作推出完整的USB 3.0 IP解决方案

一站式定制芯片及IP供应商灿芯半导体(上海)有限公司(以下简称“灿芯半导体”)与成都纳能、芯启源电子科技有限公司(以下简称“芯启源”)共同合作,集成USB3.0物理层设计(PHY)与控制器 (Controller)并应用于40nm和55nm的工艺技术,推出完整的USB 3.0 IP解决方案。

灿芯半导体一站式定制芯片解决方案,快速满足客户的差异化需求

灿芯半导体(灿芯股份,688691)作为领先的一站式定制芯片及IP供应商应邀参展,现场展示了公司ASIC定制芯片解决方案及其成功案例。利用自身丰富的定制芯片设计经验与现有系统级芯片设计平台方案相结合的优势,针对客户产品具体应用需求,进行IP及系统方案定制,可快速满足客户的需求。

【选型】灿芯提供200Mbps到4800Mbps的IO,用于各芯片间的接口通信,有阻抗校准功能

Brite灿芯半导体 DDR IO库覆盖了广泛的DDR标准,数据速率从200Mbps到4800Mbps,Brite提供了具有竞争力的DDR IO特性,包括OCD、ODT、DCC和VREF校准以及TX去加重等可选项配置,以实现高速性能、低抖动、低功耗和紧凑的单元尺寸。

灿芯半导体第二代DDR低功耗物理层IP基于40LL工艺,提高DDR速度

一站式定制芯片及IP供应商灿芯半导体(上海)有限公司(以下简称“灿芯半导体”)基于40LL工艺的第二代DDR低功耗物理层IP,该IP与第一代的低功耗DDR PHY相比面积减少20%, 功耗减少37%,物理实现时间减少50%。

登录 | 立即注册

提交评论