【产品】国产FPGA开发板XSSL25-F256-V1,具有丰富的硬件资源和外围接口

XSSL25-F256-V1 FPGA开发板的核心器件为西安智多晶微电子有限公司的SL2-25K FPGA 器件,该 FPGA 基于低功耗工艺,通过最低的成本实现较高的功能性,可用于无线、有线、广播、工业用户以及通信等行业中的低成本应用领域。

该开发板提供全正向设计的软硬件工具链,编译软件采用全自主开发的 HQFPGA 软件开发系统,在同一可执行环境下集成了从综合、布局、布线等 所有 FPGA 实现功能。HQFPGA 还提供一键式(Push-Button)的运行模式, 并提供多种界面语言,方便用户完成简单、快速、高效及优化的 FPGA 开 发。

XSSL25-F256-V1 开发板具有丰富的硬件资源和外围接口,秉承简洁、 实用、可靠的设计原则,旨在引导客户快速熟悉智多晶的 FPGA 产品。适用 于软件无线电、工业控制、多媒体应用等项目开发初期验证,同时也可用于教学及培训。

图1 开发板实物图

开发板套件

XSSL25-F256-V1 开发板套件包括:

XSSL25-F256-V1 开发板

Xist CPLD/FPGA 通用 USB 下载线:XSKIT-CABLE-USB

5V 电源供电线(MINI USB 口)

XSSL25-F256-V1 用户手册

图 2 开发板套件

硬件框图

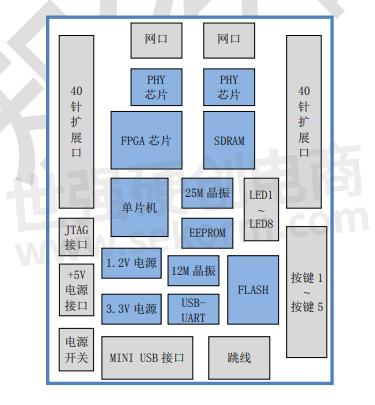

图 3 开发板硬件框图

功能及特点

FPGA

25K LE

864Kb Block RAM

BGA256 封装,引脚个数 256

电源

5V 电源输入,具有过流保护功能

板上电压:5V、3.3V、1.2V

时钟资源

25MHz 有源晶振

按键

1 个单片机复位按键

4 个用户按键

LED

1 个电源指示灯

1 个配置完成指示灯

8 个用户 LED

扩展口

2 个双排 40 PIN 插针

1 个双排 24 PIN 插针

提供 5V、3.3V 和数字地

单片机

STC12LE5604AD,增强型 8051 内核

加密性强,有全球唯一 ID 号

8 通道,10 位 ADC

以太网

2 个博通公司 B50610M PHY 芯片

1000BASE-T/100BASE-TX/10BASE-T Gigabit

支持 RGMII MAC interface

SDRAM

Hynix 公司 HY57V283220-6

存储容量:4 Banks x 1M x 32Bit

最高时钟频率:166MHz

USB-UART

支持 5V 戒 3.3V 电源

全速 USB 设备接口

提供 12MHz 时钟源输入

硬件全双工串口,支持通讯波特率 50bps~2Mbps

FLASH

Winbond 公司 W25Q16

存储容量:16Mbit

接口类型:Standard SPI、Dual SPI、Quad SPI

EEPROM

Microchip 公司 24LC04

存储容量:4Kbit

IIC 接口

配置模式

JTAG 模式

AS 模式

PS 模式

- |

- +1 赞 0

- 收藏

- 评论 0

本文由小幸福转载自世强,原文标题为:XSSL25-F256-V1 用户手册,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【产品】基于智多晶SL2-25E FPGA芯片的软件无线电(SDR)评估板,适用于项目开发初期验证、教学及培训

为了更好让无线通信客户评估智多晶FPGA芯片,西安智多晶为客户打造了一个专业的软件无线电(SDR)评估板,可用于客户前期的项目预研,其核心器件是西安智多晶的SL2-25E FPGA芯片,F256封装。这个评估板卡非常适合小带宽、低成本的通信项目,专网或公网的应用。

【产品】基于低功耗28nm FPGA的开发板XSSA30-U213-V1,熟悉国产FPGA的优选平台

为了更好让客户评估智多晶28nm 30K逻辑FPGA芯片,西安智多晶设计了一款可用于前期评估和移植验证的平台,该开发板XSSA30-U213-V1的核心器件是西安智多晶的SA5Z-30-D1-8U213,基于低功耗28nm CMOS铜工艺,可用于工业控制、视频接口处理等领域客户的前期评估。

【IC】智多晶28nm FPGA家族SEAL5000系列新发SA5Z-100,采用低功耗28nm@LUT6工艺

2022年的下半年,西安智多晶28nm SEAL5000家族系列喜迎重量级新成员SA5Z-100,采用先进低功耗的28nm@LUT6工艺,集成高达8个通道13.1Gbps的高速SerDes,支持PCIe2.0 x4以及HDMI2.1等接口协议。

【经验】智多晶FPGA上实现LTE削峰算法PC-CFR

CFR算法是一种直接在数字域上面处理的方法,对于超出设定门限值的信号,直接在数字域上进行处理和消除。目前CFR算法有PW-CFR、NS-CFR和PC-CFR,常用的还是PC-CFR,其削峰能力最佳,本文就针对PC-CFR算法,在智多晶AD9365射频开发板上进行测试和实现。

SA5Z-30 FPGA 开发板 FPGA 参考设计

描述- 本文档提供了西安智多晶微电子有限公司SA5Z-30 FPGA开发板的FPGA参考设计,旨在帮助用户快速上手。文档详细介绍了开发环境、相关文档、工程目录结构、工程复现过程,并提供了多个参考设计示例,包括UART、DDR_TEST、PHY_LOOP、HDMI_UART和HDMI_OV5640等。

型号- SA5Z-30,SA5Z-30-D1-8U213C

XSSL25-F256-V1 用户手册

描述- 本手册为西安智多晶微电子有限公司的XSSL25-F256-V1 FPGA开发板用户手册。内容涵盖开发板概述、硬件电路、软件系统及注意事项。开发板以SL2-25K FPGA为核心,具备丰富的硬件资源和外围接口,支持多种配置模式,适用于软件无线电、工业控制等领域。手册详细介绍了开发板的硬件资源、电路设计、软件安装和工程案例,旨在帮助用户快速上手和正确使用开发板。

型号- 2000S,AX3514A,2000,8051,24LC04,STC12LE5604AD,AX3514ASA,W25Q16,B50610M,XSSL25-F256-V1,HY57V283220T-6,CH340G,SL2-25K,HY57V283220-6

SA5T-100 FPGA 开发板用户指南

描述- 本指南详细介绍了西安智多晶微电子有限公司的SA5T-100 FPGA开发板。该开发板基于28nm CMOS铜工艺的SA5T-100 FPGA芯片,适用于工业控制、视频接口处理等领域的前期评估。开发板具备丰富的硬件资源和外围接口,包括电源、时钟、ADC、QSPI、I2C、DDR3、以太网、HDMI、摄像头模组、微矩形连接器、USB-UART、按键、LED指示灯和FMC接口等。指南详细描述了各接口的原理图、引脚描述和功能,为用户提供了全面的使用指导。

型号- SA5T_100_D0_8F676C,SA5T-100

【应用】智多晶FPGA驱动LCD屏,基于55nm制程逻辑单元可达25K在片内实现任何LCD接口时序电路

市面上的LCD屏类别很多,在需要屏幕的产品开发阶段往往需要对屏幕进行测试,就需要设计驱动板点亮LCD屏幕继而进行亮度,色域等参数的评估,而目前很难有一款集成芯片能够兼容不同接口、不同分辨率的屏幕。智多晶FPGA基于55nm制程逻辑单元可达25K,轻松在片内实现任何LCD接口时序电路,并且可编程重配置能够实现在一款板子上兼容不同屏幕的需求。

FTDI Chip USB方案 USB 桥接解决方案专家

描述- FTDI Chip 提供全面的 USB 解决方案,包括芯片、开发工具、应用笔记和软件支持。其产品涵盖 USB 桥接器、模块、电缆等,支持多种接口和操作系统。FTDI Chip 的解决方案旨在缩短设计时间,提高系统性能,并提供强大的系统实现。

型号- FT311,FT600Q,USB-RS232-WE-5000-BT5.0,USB-RS485-WE-1800-BT,USB-RS422-WE-1800-BT,FT232H,FT234XD,UMFT602A-B,USB-RS232-WE-1800-BT_0.0,USB-RS232-WE-1800-BT 3.3,TTL-232R-3V3-WE,TLL-232R-5V,FT230XQ,FT260Q,FT230XS,FT260S,FT232RQ,USB-RS485-WE-5000-BT,TIL-232R-3V3,FT4222,FT601,FT600,UMFT12XEV,LTC4053,TLL-232RGVIP-WE,C232HD-DDHSP-O,VNC2,FT200XD,US232R-10,C232HM-EDHSL-O,C232HD-EDHSP-0,FT231X,FT4232H-56Q,V2DIP1-48,UMFTXXXXB*,FT4232H,TTL-232R-5V,D89,FT2232H-56Q,LC231X,FT602Q,C232HD-DDHSP-0,FT60X,TTL-232R-3V3-2MM,USB-RS232-WE-5000-BT_0.0,FT2232H-56,FT2232H,TIL-232R-3V3-VE,USB-RS232-WE-1800-BT_3.3,F T4232HL,UMFTXXXXA*,TTL-234X-3V3,FT601Q,FT232RNQ,T200XD,V2DIP1-32,UMFT260EV1A,TIL-234X-5V-AJ,TTL-232R-3V3,USB-RS422-WE-5000-BT,USB-RS232-WE-5000-BT_5.0,US232R-500,VNC2-48Q,TTL-232R-3V3-AJ,US232R-100,VNC2-48L,UM245R,VINCO,FT2232HL,FT600 系列,UMFT311EV,TTL-232RG-VSW5V-WE,FT232RNL,FT2232HP,TTL-234X-3V3-AJ,UT232R-200,FT245RQ,TTL-234X-3V3-WE,FT4222H,FT4233HP,USB-RS232-WE-5000-BT3.3,UM232H,TTL-232RG-VSW3V3-WE,UMFT4222H,TTL-232RG-VREG1V8-WE,TIL-232RG-VSW5V-WE,V2DIP2-32,UM232R,USB-RS232-WE-1800-BT5.0,UMFT600A,TIL-232R-5V-WE,FT602Q-B,CHIPI-X10,UB232R,FT245RNL,FT233HP,TTL-234-3V3,TTL-232R-5V-AJ,TTL-232RG-VREG3V3-WE,TTL-232RG-VIP-WE,US232R-200,UT232R-500,FT245RNQ,MM232R,FT245RL,FT221XS,FT240XQ,FT2233HP,TTL-234X-5V-WE,FT221XQ,FT240XS,UMFT120DC,FT4232HP,FT201XS,UMFT231XC,USB-RS232-WE-5000-BT0.0,EVAL232R,UMFT601X,TTL-234X-3V3-2MM,TTL-232R-5V-WE,UMFT602X-B,C232HM-EDHSL-0,FT312D,C232HD-EDHSP-O,FT4232HA,FT4232H-56,USB-RS232-WE-1800-BT_5.0,FT231XQ,UM232H-B,FT4232HL,FT231XS,FT232RL,FT260,FT232HL,UMFTXXXXE*,TTL-234X-5V,UMFT600X,FT232HP,LC234X,USB-RS232-WE-5000-BT_3.3,VNC2-32L,UMFTPD3A,FT311D,FT220XQ,C232HM-DDHSL-0,FT120T,FT201XQ,UMFT4222EV,FT220XS,V2DIP2-48,UMFT601A

SA5Z-50 FPGA 开发板用户指南

描述- 本指南详细介绍了西安智多晶微电子有限公司的SA5Z-50 FPGA开发板。该开发板旨在评估和验证基于28nm CMOS铜工艺的SA5Z-50 FPGA芯片。开发板具备丰富的硬件资源和外围接口,包括电源、上电配置接口、时钟引脚、ADC接口、QSPI NOR FLASH接口、I2C EEPROM接口、DDR3 SDRAM接口、以太网接口、HDMI接口、RS485接口、UART接口、CAN接口、按键、LED指示灯、拓展IO接口和LVDS接口等。指南还提供了详细的接口描述和原理图,以帮助用户进行开发和应用。

型号- SA5Z-50,EN25QX128A-104HIP,M15T4G16256A(2S),DC-091-A200,SA5Z-30-D0-8U324C,SA5Z-50-D0-7F484C,3710M080046G3FT01,CFEON QX128A-104HIP

【经验】HqFPGA中如何对设计进行物理约束?

物理约束是FPGA软件开发过程中不可或缺的步骤,决定了HDL代码映射到硬件芯片上的效果。本文以一个流水灯工程为例讲解在设计中做物理约束的整个过程。约束语句中的pin脚号是根据西安智多晶FPGA开发板上连接LED的pin号定,实际应用中应根据需求设定。约束文件编辑好后就可以对设计进行综合,布局/布线。

XSSL12-F256-V1 用户手册

描述- 本手册为西安智多晶微电子有限公司的XSSL12-F256-V1 FPGA开发板用户手册。内容涵盖开发板概述、硬件电路、软件系统及注意事项。开发板基于SL2-12K FPGA,具备丰富的硬件资源和外围接口,适用于软件无线电、工业控制等领域。手册详细介绍了开发板的硬件组成、电路设计、软件安装与使用方法,并提供了例程说明。

型号- XSSL12-F256-V1,2000S,AX3514A,2000,8051,24LC04,STC12LE5604AD,AX3514ASA,W25Q16,B50610M,SL2-12K,HY57V283220T-6,CH340G,HY57V283220-6

SA5Z-30 FPGA 开发板用户指南

描述- 本指南介绍了西安智多晶微电子有限公司的SA5Z-30 FPGA开发板。该开发板基于28nm工艺的SA5Z-30 FPGA芯片,适用于工业控制和视频接口处理等领域的前期评估。开发板具备丰富的硬件资源和接口,包括SPI FLASH、SD卡、以太网、HDMI、摄像头接口等,并提供了用户接口如GPIO、按键、LED指示灯等。指南详细描述了开发板的硬件特性、接口连接和功能说明。

型号- MT3420B,SA5Z-30,SCT2432,SA5Z-30-D1-8U213C,SA5Z-30-D0-8U324C,W25Q64JVSSIQ,LN1134A252MR-G

电子商城

服务

可加工PCB层数:1-30层;板材类型:FR4板/铝基板/铜基板/刚扰结合板/FPC板/高精密板/Rogers高频板;成品尺寸:5*5mm~53*84cm;板厚:0.1~5.0mm。

最小起订量: 1 提交需求>

可加工PCB板层数:0-60层,板材类型:高频板/高速板/高频混压板/盲埋孔板/HDI板/无卤素板/厚铜板/刚柔结合板;最大加工尺寸:622*1200MM;板厚:0.05-8.0MM;铜厚:0.33-30OZ;

最小起订量: 1 提交需求>

登录 | 立即注册

提交评论