【经验】MCU通过SPI接口实现升级FPGA的方法

西安智多晶Sealion2000系列SL2E-5E是集成了Flash的FPGA,含有5K LUTs、12个M9K、16个18x18乘法器以及2个PLL,可考虑用于替换XO2、XO3器件,以及MAX II、MAX V等国外性价比不高的CPLD,在项目应用时,用户往往会考虑远程更新程序的功能,防止设备需要升级程序带来的麻烦,本文介绍一种MCU通过SPI接口实现FPGA程序升级的方法,已经成功应用于客户的实际项目中。

SL2E-5E内部Flash的主存储阵列共16K个地址,每个地址可存储128bit数据,分为CFG和UFM两个区域,其中CFG占12K地址,用于存放用户FPGA程序,剩下4K地址是UFM区域,用于存放用户数据,其中UFM区域的读写控制IP,用户可以在Hq工具里直接调用。

SPI接口

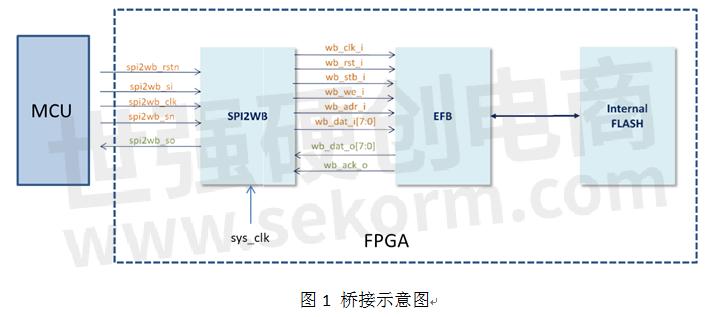

我们会提供给用户一个Verilog程序块,可看成是一个桥接的接口,连接MCU与内部Flash的通道,用户将此程序模块例化到工程里,引出SPI接口到芯片GPIO端口与MCU相连,MCU工程师可以按照一定的送数步骤来实现工作状态中的程序功能更新。桥接原理如图1所示:

注:SPI2WB是智多晶提供的Verilog程序块,用户可当一个黑盒子使用。SPI2WB接口信号描述如下所示:

写接口时序

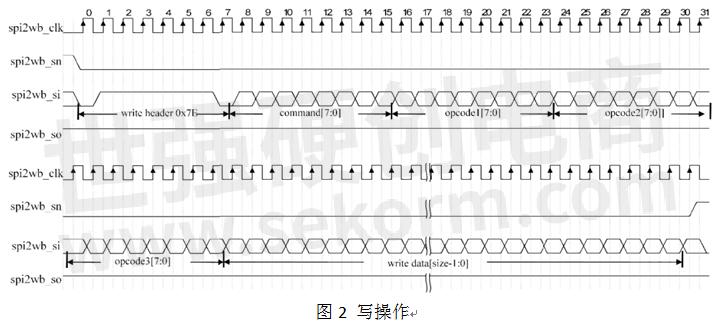

MCU需要按照一定的时序步骤来进行读写操作,写操作图2所示:

1) 先发0x7E表示要写操作

2) Command是8bit指令编码

3) 24bit操作码opcode1~opcode3,无特殊说明时,操作码为0

4) Write data是写入的数据,注意不是每条指令都带此数据

其中指令编码的定义如下所示:

MCU写操作的步骤

升级程序主要涉及到写操作,用户可以编译一个闪灯的FPGA程序,用于观察更新后是否正常运行的指示,MCU会把FPGA编译后的xfb文件一行行写入到Flash中,并且必须严格按照如下步骤:

1)写 0x74指令 ISC_ENABLE_X 使能EFB 后台模式,opcode1 设为0x08 ,选择访问FLASH ,有效数据长度为5字节,即0x7e头 + command + opcode1\2\3

2)写0x0e擦除指令ISC_ERASE ,opcode1 设为0x01 时,擦除CFG、UFM 区域,需要时间约为8.3ms,有效数据长度为5字节,即0x7e头 + command + opcode1\2\3

3)写0xb4指令 WRITE_ADDR 设定flash地址 以0 开始 ,有效数据长度为9字节,即

0x7e头 + command + opcode1\2\3 + 32位0

4)写0x70指令 PROG_INCR_NV 将数据写入设定的FLASH 地址 ,opcode3为0x01,有效数据长度为21字节,即

0x7e头 + command + opcode1\2\3 + 128位数据

每条0x70指令后需要跟随0xff noop指令 ,noop指令有效数据长度为5字节,格式为:

0x7e头 + 0xff + opcode1\2\3(均为0xff)

Noop指令发送后需要等待 40us以确保flash写入完成。

连续发送xfb文件直到文件发送完成。

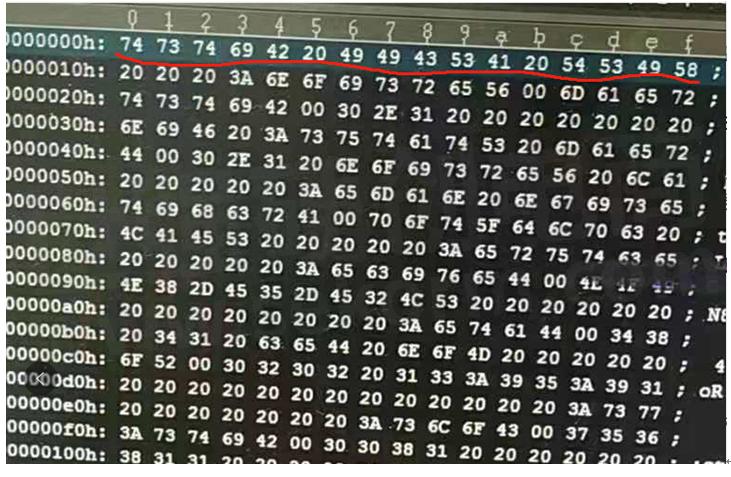

注意,xfb文件数据每一行的写入需要倒序,举个例子:

第一行数据从左到右拼成128bit,MCU需要把这128bit数据倒序发送,最低位先发。我们可以提供倒序操作的小工具,可实现xfb文件每一行的倒序。

5)写0xb4指令 WRITE_ADDR 跳转到flash地址 0x2fff ,有效数据长度为9字节,即

0x7e头 + command + opcode1\2\3 + 0x00 + 0x00 + 0x2f + 0xff

6)写0x70指令 PROG_INCR_NV 将数据0x0900000000写入,才能使用内部FLASH 进行正确配置,opcode3为0x01,有效数据长度为21字节,即

0x7e头 + command + opcode1\2\3 + 128位数据(即0x0000_0000_0000_0000_0000_0009_0000_0000)

跟随0xff noop指令 ,noop指令有效数据长度为5字节,格式为:

0x7e头 + 0xff + opcode1\2\3(均为0xff)

Noop指令发送后需要等待 40us以确保flash写入完成。

7) 发送 0x26 指令 ISC_DISABLE 关闭EFB 使能,在访问FLASH 结束后需要发送此指令,有效数据长度为5字节 0x7e头 + command + opcode1\2\3

8)发送 0x79 指令 REFRESH 触发重新配置,有效数据长度为5字节

0x7e头 + command + opcode1\2\3

注:

* 每次cs拉高后,需要等待至少16个sys_clk,此时钟由fpga程序内部自己提供

* 若未特别说明,opcode为0.

* nConfig脚保持为高电平。

总结

SPI2WB接口模块占用2%的逻辑资源,在可接受范围内,用户使用这种方法实现远程升级,需要预留5根GPIO出来与MCU相连,但是第一次烧写可以先用USB下载器来烧程序,或者通过DATA0、DCLK、nCS发送xfb文件到SRAM运行,让FPGA运行起来,之后在正常工作状态下就可以随时随地更新FPGA程序,无需人为到场插线更新。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由干饭机器转载自西安智多晶,原文标题为:MCU通过SPI接口升级SL2E-5E的方法步骤,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关推荐

【经验】如何在FPGA上实现低成本开根号运算?

开根号运算是科学计算和工程应用中基本而重要的运算之一,在QuartusII和ISE开发软件中,都集成了开根号的ip核,这些底层源码对于用户来说是不可见的,那么如何在西安智多晶的FPGA中实现开根号运算,是本文要探讨的课题。

【经验】西安智多晶5000系列FPGA内嵌MCU调试测试指南

西安智多晶推出的Seal 5000 FPGA SA5Z-30系列内部合封Cortex M3硬核,最高主频可达200Mhz,32KB数据RAM和128KB指令RAM。本文针对FPGA内嵌M3硬核的使用做简洁的开发过程。

【经验】智多晶FPGA上实现LTE削峰算法PC-CFR

CFR算法是一种直接在数字域上面处理的方法,对于超出设定门限值的信号,直接在数字域上进行处理和消除。目前CFR算法有PW-CFR、NS-CFR和PC-CFR,常用的还是PC-CFR,其削峰能力最佳,本文就针对PC-CFR算法,在智多晶AD9365射频开发板上进行测试和实现。

【选型】国产FPGA SL2-25E-8U324替代XC6SLX16 CSG324用于工业伺服控制器,有效应对交期问题

客户在工业伺服控制器中用到一款Xilinx FPGA,但因为交期问题需要国产化替代,使用型号是XC6SLX25-CSG324,主要用于做逻辑控制和与MCU交互数据、进行数据处理,给客户推荐了西安智多晶SL2-25E-8U324,可以兼容替代。

SA5Z-30 FPGA 配置用户指南

描述- 本指南详细介绍了西安智多晶微电子有限公司的SA5Z-30 FPGA的配置过程和用户接口。内容包括配置模式(SCM、SSPI、SCPU、MSPI、JTAG)、配置流程、重配置方法(手动和自动)、多片配置方式(ganged和daisy-chain),以及上电期间IO行为。指南还提供了配置接口列表、时序图和参数表,以帮助用户理解和实施FPGA配置。

型号- SA5Z-30

【应用】国产海狮系列FPGA SL2E-5E用于扩展外设接口,集成flash,工作频率高达300MHz

西安智多晶的SL2E-5E是一款集成了5K逻辑单元的小规模FPGA,但是比CPLD容量更大,能实现更多的逻辑设计,同时该FPGA内部集成了Flash,不需要再外接配置用的Flash,简化了电路设计。

SA5Z-30 FPGA 开发板 FPGA 参考设计

描述- 本文档提供了西安智多晶微电子有限公司SA5Z-30 FPGA开发板的FPGA参考设计,旨在帮助用户快速上手。文档详细介绍了开发环境、相关文档、工程目录结构、工程复现过程,并提供了多个参考设计示例,包括UART、DDR_TEST、PHY_LOOP、HDMI_UART和HDMI_OV5640等。

型号- SA5Z-30,SA5Z-30-D1-8U213C

Seal(海豹)SA5Z-30 FPGA 产品手册

描述- 西安智多晶微电子有限公司发布的SA5Z-30 FPGA产品手册详细介绍了该系列FPGA的特性、资源、结构和封装。该系列基于28nm工艺,具备丰富的逻辑资源和高性能可编程逻辑单元,适用于无线通信、工业控制、图像处理等领域。

型号- 海豹5000系列,SA5Z-30-D2,SA5Z-30-ES,SA5Z-30-D0-UBGA324,SA5Z-30-D0,SA5Z-30-D1,SA5Z-30-D1-UBGA213,SA5Z-30-D2-8U213C5,SA5Z-30,SA5Z-30-D1-8U213C4,SA5Z-30-D2-8U213C6,SA5Z-30-D2-UBGA213,SEAL 5000系列,SA5Z-100-D1-8U324C,SA5Z-30-D0-8U324C6,SA5Z-30 系列,SA5Z-30-D1-8U213C,SA5Z-30-D2-8U213C

Sealion 2000 FPGA PLL 动态调频应用指导

描述- 本资料为西安智多晶微电子有限公司发布的Sealion 2000 FPGA PLL动态调频应用指导,主要介绍了Sealion 2000系列FPGA中PLL(锁相环)模块的动态调频功能。内容包括PLL模块概述、动态调频测试环境、相关模块说明、PLL原语模块、wb2pll模块等,详细阐述了如何通过WISHBONE接口动态调整PLL输出时钟的频率,实现动态调频功能。

型号- SEALION 2000

【应用】国产智多晶FPGA助力自动化测试设备扩展上百GPIO口,解决MCU端口不足痛点,核电压为1.2V

在一款自动化测试设备上,需要控制5个步进电机、86个电磁铁和几十个指示灯,以及外部通讯接口,使用的雅特力的AT32F407RCT7,由于控制逻辑并不复杂,需要使用的IO会比较多,因此需要对MCU的IO口进行扩展。客户希望在扩展的控制芯片增加步进电机的驱动,只需要发送指令就可以控制电机的旋转。推荐了智多晶的FPGA SL2E-5E-8M121I。

Sealion(海狮)2000 系列 FPGA数据手册

描述- 西安智多晶微电子有限公司的Sealion 2000系列FPGA是一款基于55nm工艺的低功耗FPGA,适用于低成本、低功耗应用。该系列FPGA具备丰富的逻辑资源和存储器模块,支持多种I/O标准和配置模式,并提供内置Flash和SDRAM等功能。

型号- SL2D-25E,2000S,SL2E-5E,SEALION 2000S,SL2E-5E-8M121I,2000E,SL2-12E-8F256C,SEALION 25K,SL2-18,SEALION 5K,2000E 系列,SL2S-25 V,SEALION 2000E 系列,SL2-12,SL2S-12E,2000,SL2E-7V-8U400I,SL2S-25 E,SL2-25 V,2000 系列,SL2E-7 E,SL2E-7V,SL2E-5 E,SEALION 2000,SL2S-12E-8E176C,SL2S-12 V,SL2E-5E-8N84I,SL2E-7 V,SL2-25 E,SL2D-25 V,SL2E,SL2S-25,SL2S-12 E,SL2D,SL2S-12E-8F256C,SEALION 2000 系列,SL2-12 V,SL2-5,SL2S-25E-8U213C,SL2D-25 E,SL2-7,SEALION 7K,SL2E-7E,SL2S-25E,SL2S,SL2-25E-8U324C,SL2-12 E,SL2S-12,SEALION 12K,SL2,SEALION 2000D,SEALION 2000E,SL2-25

SA5Z-30 FPGA 器件概述

描述- 西安智多晶微电子有限公司的SA5Z-30系列FPGA器件采用28nm工艺,具备丰富的逻辑资源、高性能可编程逻辑单元、低功耗特性、嵌入式和分布式存储、高性能灵活的I/O单元以及合封DDR2/3 SDRAM存储。适用于无线通信、工业控制、图像处理、人工智能、数据处理中心及云信息等行业。

型号- SA5Z-30-D3-U256,SA5Z-30,SA5Z-30-D0-U324,SA5Z-30-D1-U213,SA5Z-30-D2-U256,SA5Z-30 系列,SA5Z-30-D2,SA5Z-30-D0-8U324C,SA5Z-30-D3,SA5Z-30-D0,SA5Z-30-D1

智多晶FPGA选型表

FPGA选型参数:28nm hpc+工艺,自 LUT6 架构,嵌入MCU,30K~325K LUT4,内置100/200/400个25X18/18X18/9X9专用乘法器,硬核 Memory DDR controller,PCIe-Gen2/3,1Mbps/s 采样,12bit ADC,支持 DDR4-1866Mbps,LVDS 1.25Gbps,Serdes 3.1Gbps~12.5Gbps,3D 合封 DDR2、DDR3 、DDR4

|

产品型号

|

品类

|

封装

|

LUTS

|

Flip-Flops

|

Slices

|

CLB

|

Flash(Kbits)

|

Max Distributed Ram (Kbits)

|

Embedded memory

(Kbits)

|

Number of Block SRAM(9 Kbits/block)

|

Embedded

18x18multipliers

|

General purpose PLLs+DLLs

|

Global Clock Networks

|

User I/O Banks

|

Max user I/O(注1)

|

|

SL2E-5E-8W81I

|

FPGA

|

81-ball WLCSP,0.4mm

|

5040

|

5040

|

2520 (LUT:FF=1:1)

|

630

|

512

|

40

|

108

|

12

|

16

|

2+2

|

16

|

6

|

199

|

选型表 - 智多晶 立即选型

【经验】解析智多晶合封系列FPGA中DDR2的应用

合封系列FPGA可以应用在需要大量缓存数据的场合,比如工业数据采集卡、视频处理应用以及无线通信中的数据采集板,如果各位读者朋友们有需要用到FPGA+DDR2架构的,可以联系智多晶,智多晶会提供完整的DDR2 Control IP,甚至亲手为用户写好应用层部分的程序,并为用户调试好。

SA5Z-30 FPGA 数据手册

描述- 本资料为西安智多晶微电子有限公司的SA5Z-30 FPGA数据手册,详细介绍了SA5Z-30 FPGA的特性和应用。该器件属于Seal(海豹)5000系列,基于28 nm工艺,提供丰富的逻辑资源、高性能可编程逻辑单元、灵活的片内时钟、嵌入式和分布式存储、高性能I/O单元等特性,适用于无线通信、工业控制、图像处理、人工智能等领域。

型号- SA5Z-30-D1-U213,SA5Z-30-D2-U256,SA5Z-30-D2,SA5T-325,SA5Z-30-D3,SA5Z-30-D0,SA5Z-30-D1,SA5T-100,SA5T-366,SA5Z-50,SA5Z-30,SA5Z-30-D0-U324,SA5Z-30-D0-8U324C

电子商城

现货市场

登录 | 立即注册

提交评论