【应用】去抖时钟AU5329作为时钟发生器的GUI软件怎么配置?

AU5329是奥拉推出的一款高性价比去抖时钟,其广泛应用于传输网OTN、SDH设备中,可支持2路外部时钟源输入也可选用Crystal/XO/TCXO输入,并提供10路时钟输出,芯片内部有2个PLL,时钟输出可通过PLL灵活导出,输出时钟可高达2.1GHz。本文主要介绍Au5329作为时钟发生器时使用GUI软件的配置方法。

1、根据客户的原理图或要求选择I2C或者SPI接口。

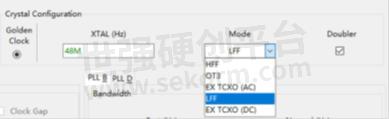

2、配置参考源,Au5329外置参考源可以选晶体也可以选晶振,一般晶体或晶振推荐48MHZ或54MHZ,不推荐50MHZ或25MHZ,因为我们常见输出时钟有100MHZ,125MHZ等,而输出时钟频率不能和参考源有线性关系,否则容易产生串扰,相噪较差。如果参考源选用晶体,Mode选LFF。如果用晶振,外部连接是AC耦合输入,Mode选择EX TCXO (AC);外部连接是DC耦合输入,Mode选择EX TCXO (DC)。

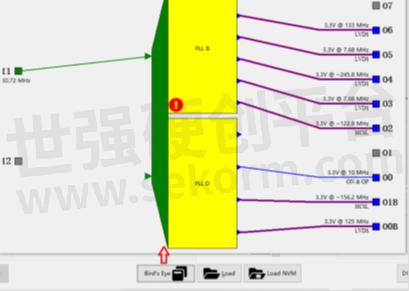

3、Au5329作为时钟发生器使用,用晶体或晶振作为参考源输入参考时钟,无需设置PLL,直接配置输出时钟即可。注意输出频率、电压、格式必须和原理图保持一一对应。

4、配置完成需校验工程文件是否正确,点UGI右上角“send 2 Chip”进行工程文件校验,如果频率或配置有问题,会提示告警,需要重新调整配置。

5、校验完成后可使用“BirdEye”按钮,检查输入和输出时钟配置是否和客户频率要求一致。如符合要求,保存工程文件。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由Barry提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【经验】关于奥拉时钟发生器Au5329监控PLL loss of lock实时状态的配置方式

奥拉Au5329是具有2个PLL的时钟发生器,抖动150fs,支持10路输出,广泛应用于基站上。在测试验证时,需要检查PLL的锁定状态,那么该如何验证?本文中将为大家介绍奥拉时钟发生器Au5329监控PLL loss of lock实时状态的配置方式。

【经验】奥拉Au5329时钟发生器外部参考源选择及GUI配置方式

奥拉Au5329是具有10路输出的时钟发生器,时钟输出可以以高度灵活的方式从两个PLL输出。Au5329支持IIC及SPI通信接口配置频率计划,也可支持NVM烧录两次配置。奥拉Au5329需要外部晶体作为参考源,本文将介绍外部参考源的选择及GUI配置。

【经验】关于奥拉Au5619抖动衰减器兼容Au5329设计注意事项

奥拉Au5619双锁相环频率抖动衰减器,是Au5329的升级版,抖动从150fs优化至小于85fs的典型RMS抖动,并支持12路输出,内部ZDB模式,可实现输入到输出的相位延迟变化小于0.5ns。广泛应用于5G基站中。

奥拉(Aurasemi)时钟和电源管理产品选型指南

目录- 公司简介 Timing BU Introduction VRM LDO & BuckBoost

型号- AU4562,AU5424,AU5425,AU5426,AU5327BC1-QMR,AU5325BC1-QMR,AU5620,AU5508,AU560X,AU5315AC0-QMR,AU5328,AU532X,AU8010AA-QNR,AU5329,AU8014EB-QNR,AU5329B-QMR,AU8310A0-WMR,AU5325BC2-QMR,AU5411A-QMR,AU5327BC2-QMR,AU8014EA-QNR,AU8013EB-QNR,AU4531,AU5X82,AU8941,AUXXXX,AU5410,AU5411,AU571X,AU531X,AU5615,AU5424G,AU5617,AU5317AC0-QMR,AU5424A,AU5410A-QMR,AU8014A,AU8013EA-QNR,AU8012AA-QNR,AU5X8,AU8011CA-QNR,AU4592

Au5329: Dual Frequency Translation and Jitter Clean Synthesizer

型号- AU5329BZZ-QM,AU5329A,AU5329B,AU5329CX-EVB,AU5329A00-QMR,AU5329B00-QMT,AU5329A00-QMT,AU5329B00-QMR,AU5329

Au5329: 10 路输出、兩路锁相环、频率转换抖动衰减器

型号- AU5329CX-EVB,AU5329A,AU5329B,AU5329B00-QMR,AU5329BZZ-QM,AU5329,AU5329B00-QMT

【选型】以太网板卡平台的去抖时钟选用Au5329,可同时满足客户去抖和时钟发生器的功能需求

某客户以太网板卡平台此前使用某国外大厂的多款时钟发生器产品及抖动衰减器产品,由于项目较多,需求各不相同,时钟输出频率从100MHz~600MHz不等,输出时钟4-8路不等;笔者给客户推荐了奥拉去抖时钟Au5329,单颗物料可以覆盖客户全部的需求,客户只需要根据单个项目的实际需要通过GUI软件对Au5329进行配置即可。

AU5329C: Dual Frequency Translation and Jitter Clean Synthesizer

型号- AU5329CX-EVB,AU5329C,AU5329C00-QMT,AU5329C00-QMR

【应用】国产10路输出的抖动衰减时钟合成器AU5315在交换机数据转发系统的应用,支持频率范围广泛

据交换系统中应用最多的就是Serdes这种串并转换协议,随之而来的就是CDR中时钟恢复的问题,为了避免影响到我们恢复的时钟质量,需要一颗良好的低抖动特性的去抖时钟芯片,奥拉的AU5315就是数据交换板中理想的时钟芯片选择。

奥拉股份完成与SiTime的时钟IP授权交易的正式交割,短时间内实现了产品快速升级,性能达国际一流水平

近日,奥拉股份与全球知名MEMS时钟产品公司SiTime Corporation完成了时钟芯片IP授权协议的正式交割。本次交易之后,奥拉股份仍将保留所有授权IP的所有权和使用权,以及现有的时钟研发团队和业务能力。公司在时钟芯片领域深厚的技术积累,经验丰富的研发团队,为公司不断进行时钟芯片技术迭代、产品研发提供了充分的保障。

AU5329B06: DATASHEET ADDENDUM AND ORDERING INFORMATION

型号- AU5329B06-QMT,AU5329B06-QMR,AU5329-EVB,AU5329,AU5329B06

AU5329B07 Datasheet Addendum and Ordering Information

型号- AU5329B07,AU5329B07-QMR,AU5329B07-QMT,AU5329-EVB,AU5329

【产品】奥拉AU561x去抖时钟芯片:提供开创性的精度和同步性能,是5G通信优选时钟解决方案

奥拉半导体凭借其第三代去抖时钟芯片产品系列站在了时钟芯片业界的前列。既实现高端去抖时钟芯片的国产化,也实现了65fs rms抖动性能,同时还具有全面的数字锁相环功能,专为满足112Gbps PAM4 Serdes和5G无线单元而设计。

AU5329B05: DATASHEET ADDENDUM AND ORDERING INFORMATION

型号- AU5329B05-QMR,AU5329,AU5329-EVB,AU5329B05-QMT,AU5329B05

电子商城

登录 | 立即注册

提交评论