【选型】时钟发生器Si5382用于5G小基站,可简化时钟设计,具备低抖动、输出频率范围宽等优势

随着5G通信正式商用,用于室内覆盖的5G小基站也在准备进行实验站建设。5G通信小基站相对于上一代4G小基站,体积要求更小,性能要求更高,这对电路设计提出了更高的挑战。

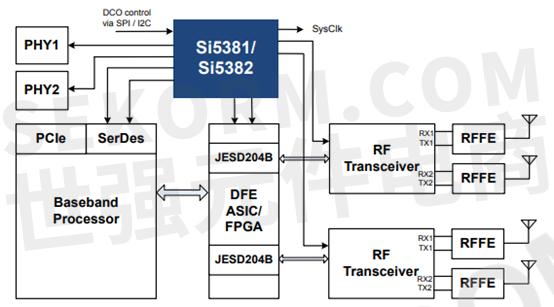

目前主流的5G小基站设计方案是FPGA+Triceiver,核心处理器、射频收发调制器都需要多路同步时钟参考信号才能保证通信的实时和准确性,传统设计是采用多个时钟发生器和压控振荡器提供参考信号,但电路复杂同时PCB面积较大。因此本文推荐SILICON LABS的多路时钟发生器Si5382,内部集成两个数字锁相环和多通道抖动衰减,任意频率/晶振输入到数字锁相环再经过频率合成电路,实现各种频点输出;最多支持12路输出时钟,通过独立路径可以支持拥有小于85fs典型相位抖动的JESD无线时钟、以太网和其他低抖动通用的时钟,以下是Si5382在5G小基站系统中的典型时钟树应用方案:

图1 Si5382时钟树应用方案

从上图中可以看出,Si5382不仅可以产生专用的LTE专用时钟频点,如30.72MHz、25MHz等频点,也可以任意配置成PHY交换芯片参考时钟等常用通信接口时钟;其差分输入频率8 kHz -750 MHz、LVCMOS单端输入频率8 kHz-250 MHz,JESD204B输出频率480 kHz -2.94912 GHz、差分输出频率1 Hz- 712.5 MHz、LVCMOS输出频率480 kHz-250 MHz,采用一片Si5382基本可以满足5G小基站通信配置时钟频率的所有需求,降低BOM成本和PCB面积;同时Si5382时钟芯片的配置软件业及其简化,界面容易操作。

综上所述,Silicon Labs的时钟发生器Si5382具有多达12路输出、85fs RMS典型值(DSPLL_B输出 12 kHz ~ 20 MHz)的低抖动、输出频率范围宽和数字频率合成节省PCB面积的特性,是5G小基站时钟树应用的优秀解决方案。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由北冥之鲲提供,版权归世强硬创平台所有,非经授权,任何媒体、网站或个人不得转载,授权转载时须注明“来源:世强硬创平台”。

相关推荐

【选型】光模块误码仪时钟源推荐高性能时钟发生器SI5340配合京瓷晶振CX3225SB,精度极高

误码设备本身需要测试不同速率的光模块,针对不同速率的光模块还需要不同的频率源作为倍频的信号时钟源。高性能的时钟发生器推荐Silicon Labs高性能时钟发生器SI5340系列,输入的参考晶振推荐京瓷,CX3225SB系列,经过了大量市场验证可放心使用。

器件选型 发布时间 : 2021-06-30

【选型】无线时钟发生器SI5386A-E-GM可以完美替换AD9528,同时支持整数和小数分频

Siliocn Labs推出的一款高性能、超低抖动无线时钟发生器SI5386A-E-GM,是其中一款非常优秀的无线去抖时钟,支持12路时钟输出,且支持输入4路输入,且支持5个时钟域,典型的抖动值可以限制在72fs左右,且最高可达3Ghz的频率输出,在5G小基站的应用中十分优秀,与另一款无线时钟AD9528相比,其性能优势非常明显。

器件选型 发布时间 : 2019-11-12

【选型】Silicon Labs 时钟和振荡器芯片选型指南

目录- 计时解决方案 晶体振荡器(XO) 压控晶体振荡器(VCXO) 时钟发生器 时钟缓冲器 抖动衰减器 无线时钟 网络同步器

型号- SI56X,SI5382,SI5383,SI5380,SI5381,SI5386,SI5331X,SI5384,SI590,SI5315X,SI591,SI595,SI510,SI598,SI511,SI596,SI597,SI514,SI515,SI512,SI513,SI516,SI52142,SI52143,SI52144,SI51210,SI5394,SI5391,SI5392,SI5397,SI5332X,SI5395,SI569,SI54X,SI567,SI52111,SI52112,SI570,SI571,SI5344H,100G,SI53212,SI5332,SI53208,SI5330X,SI5335,SI53204,SI5334,SI5338,SI547,SI545,SI546,SI549,SL18860,SI5311X,SI5342,SL18861,SI5340,SI52208,SI5341,SI5346,SI52202,SI5347,SI5344,SI52204,SI5345,SI550,SI5348,SI554,SI552,SI5342H,SI5350,SI53306,SI5351,SI53102-AX,SI52212,SI5336X,SI561,SI562,SI560,SI565,SI566,SI564,SI51214,SI51211,SI51218,SI52146,SI52147,SI532,SI533,SI530,SI531,SI534,SI5334X,SI540,SI544,SI541,SI542

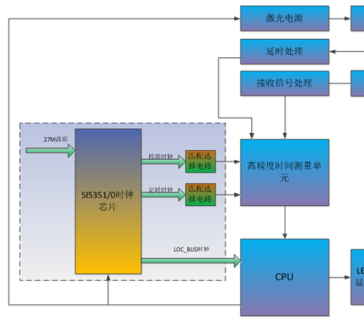

【产品】利用时钟发生器SI5351简化手持式激光测距仪设计

基于Silicon Labs SI5351单时钟芯片的手持式激光测距仪方案,测量部分多采用高精度时间测量单元电路实现测距。其中,SI5351可直接通过I2C接口配置,实现单一芯片取代锁相环、晶振、压控振荡器,能够有效减少系统BOM成本和PCB面积。

新产品 发布时间 : 2016-03-29

赛思拥有领先国内时频领域的核心技术,推出高集成度和小尺寸的同步时钟芯片和TCXO等产品,满足5G小基站设计需求

赛思拥有领先国内时频领域的核心技术, 在5G基站中可以提供完整端到端的时钟产品及解决方案, 包括但不限于IEEE1588同步时钟芯片、 时钟发生器、 时钟缓冲器、 OCXO/TCXO等。

原厂动态 发布时间 : 2023-07-02

【经验】时钟发生器Si5341型号定制以及输出串扰问题解决方法

Silicon Labs公司推出的时钟发生器Si5341最大能够支持10路差分输出,输出频率范围100Hz~712.5MHz,输出抖动范围均小于100 fs(0.1 ps),并且Si5341内部带有模拟锁相环,配合Silicon Labs的专利MultiSynth技术,能够以0 ppm合成所需的频点,本文将详细介绍Si5341型号定制以及输出串扰问题解决方法。

设计经验 发布时间 : 2020-08-21

【产品】最具频率弹性可编程的CMOS时钟发生器Si5351,非常适用于对成本敏感的消费性电子应用

Si5351采用优异的时钟技术,非常适用于对成本敏感的消费性电子应用,可在不牺牲性能的情况下大幅降低系统成本、功耗并能满足空间需求。

新产品 发布时间 : 2016-04-26

【经验】奥拉Au5329时钟发生器JESD204B SYSREF时钟输出的寄存器配置方式

Sysref时钟需要在GUI配置上勾选Sysref,否则就是普通时钟输出,这和DCLK有相位关系,奥拉时钟发生器Au5329可输出单个或多个DCLK时钟宽度,某客户在勾选GUI上的Sysref后仍无时钟输出,这应该怎么解决?本文将为你详细介绍。

设计经验 发布时间 : 2022-06-01

【经验】如何使用CBPro软件配置时钟发生器Si5332的晶体输入端电容

Silicon Labs的时钟发生器Si5332支持外置晶体/晶振/参考时钟输入,也支持内置晶体的版本,目前使用较多的是内置晶体版本,但部分用户在设计时由于自身需求仍然选择外置晶体,而选择外置晶体时通常会发现配置的晶体无法正常启动或者启动时间不太理想,如果使用CBPro软件适当配置Si5332,可以避免大部分问题。本文就将介绍如何使用CBPro软件配置Si5332的晶体输入端电容。

设计经验 发布时间 : 2019-09-24

芯科Silicon Labs低抖动时钟芯片 | 晶体振荡器 | 压控振荡器 | 时钟发生器 | 时钟缓冲器

芯科科技Silicon Labs时钟芯片代理商世强,提供Silicon Labs低抖动时钟芯片参数选型服务,芯科低抖动时钟芯片供应服务,芯科低抖动时钟芯片资料。业界抖动系数超低的低抖动时钟芯片,包括XO/VCXO晶体振荡器/压控振荡器、Clock/JA Clock时钟发生器、Buffer时钟缓冲器。推荐Si53xx系列,Si5342H,Si5344H,Si5347,Si5332,Si5381。

原厂动态 发布时间 : 2018-06-27

【经验】Silicon Labs时钟发生器SI5332时钟差分信号变单端输出问题及处理方法

Silicon Labs时钟发生器SI5332在使用CB Pro软件配置好电平之后,有工程师会有疑问,原本配置好的3.3V 125MHz lVDS电平 OUT/OUTB是否可以在配置不动的情况下单独分开做两个125MHZ单端时钟输出?本文将为你解析。

设计经验 发布时间 : 2022-03-21

时钟发生器Si5351的版本B和版本A有什么变化,推荐使用哪个版本?

时钟发生器Si5351目前主推版本B,版本B和版本A的主要变化有:(1)RevB:频率输出范围是2.5 kHz到200 MHz;RevA:8 kHz 到160 MHz。(2)输出阻抗RevB是50欧姆,RevA是85欧姆。(3)RevB不支持24-QSOP封装。

技术问答 发布时间 : 2017-05-05

【应用】十路输出时钟的时钟发生器Si5341用于5G CU平台的时钟链路设计,时钟频点范围100Hz~1028MHz

本文推荐使用Silicon Labs高性能时钟发生器Si5341用于5G CU的主控平台时钟设计,有多达十路输出时钟,时钟频点范围是100Hz~1028MHz,涵盖了5G CU主控平台所需的全部频点,时钟路数足够多,可以尽量减少晶振的用量。

应用方案 发布时间 : 2020-05-27

【经验】时钟发生器Si5332接地PAD引起的频率计划烧录失败问题及解决方式

Si5332支持多个输出端,每个输出端有独立的输出电压,使用ClockBuilder Pro可以快速轻松地配置频率计划,并且有专门的烧录器可通过I²C接口烧录到芯片内的NVM,但是有时候接地PAD引起的频率计划烧录失败,本文将简要分析。

设计经验 发布时间 : 2022-01-29

【应用】时钟发生器SI5351A-B-GTR用于智能音箱,以0 ppm误差产生200 MHz的任意频率合成输出

本文推荐Silicon Labs的SI5351A-B-GTR这颗小封装的时钟发生器作为智能音箱的参考时钟源,替代相关的各种时钟源。SI5351芯片是可通过I2C接口配置的时钟发生器,能以0 ppm误差产生高达200 MHz的任意频率合成输出。

应用方案 发布时间 : 2020-11-30

电子商城

现货市场

服务

提供是德(Keysight),罗德(R&S)测试测量仪器租赁服务,包括网络分析仪、无线通讯综测仪、信号发生器、频谱分析仪、信号分析仪、电源等仪器租赁服务;租赁费用按月计算,租赁价格按仪器配置而定。

提交需求>

提供全面表征产品器件耗电特征及功耗波形、快速瞬态效应、电源优化、表征和仿真测试服务,使用直流电源分析仪测量精度达50µV,8nA,波形发生器带宽100kHz,输出功率300W,示波器200kHz,512 kpts

实验室地址: 深圳/苏州 提交需求>

登录 | 立即注册

提交评论