【经验】解析HDMI Sink一致性测试及眼图测试案例

HDMI测试主要有Source端测试、Sink端测试、单项眼图信号质量测试。Source端测试已介绍、接下来淼森波实验室分享HDMI的Sink端一致测试、Sink端眼图文测试。

HDMI Sink物理层一致性测试

接收器(sink)测试

●接收器Sink

-抖动容限(8-7)

jitter tolerance

-接收灵敏度(8-5)

Min/Max differential swing tolerance

-信号对内时间偏移容限(8-6)

Intra-Pair skew tolerance

01.抖动容限测试

接收端(Sink)抖动容限测试

●接收端(Sink)抖动容限测试

-标准的抖动注入方法,适用于通常的HDMI客户,将时钟抖动成分和数据抖动成分同时注入时钟信号上。

-可选的抖动注入方法,适用于对测试精度要求非常高的客户,将时钟抖动成分和数据抖动成分分别注入时钟和数据信号上。

●Tektronix提供的方案:泰克的HDMl一致性测试方案支持标准的抖动注入方式和可选的抖动注入方式。

标准抖动注入方法:使用AFG3102

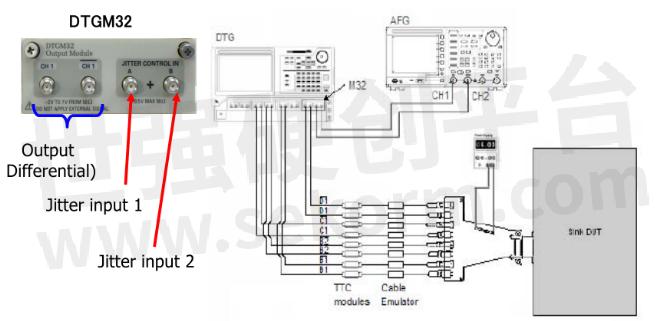

●DTGM32-允许注入两种抖动成分,速率可达350MHz

图 1

直接合成的方法实现抖动容限的测试

图 2

接收端(Sink)抖动容限测试步骤一

●进行下列Sik所支持的像素时钟速率的测试:

27MHz,74.25MH2,148.5MHz,222.75MHz,297MHz。如果设备的分辨率高于上述的分辨率,则需要针对最高分辨率进行测试

●配置Sink被测设备为需要测试的分辨率:

●用下列方法配置TMDS信号源:

-按照测试的时钟速率输出需要Sink设备所支持的任意视颜格式.

·可选方法一

-设置TMDS signal的共模电压为3.0V

-设置TMDS单端信号的逻辑摆幅为0.6Vp-p

可选方法二

-设置TMDS signal的共模电压为3.1V

-设置TMDS单端信号的逻辑摆幅为0.4Vp-p

●标准的抖动注入方法

-Required:D_JITTER=500kHz (on TMDS_CLOCK).C_JITTER=10MHz

-Required:D_JITTER=1MHz (on TMDS_CLOCK).C_JITTER=7MHz

●可选的抖动注入方法

-Optional:D_JITTER=500kHz (on TMDS_DATA),C_JITTER=10MHz

-Optional:D_JITTER=1MHz (on TMDS_DATA),C_JITTER=7MHz

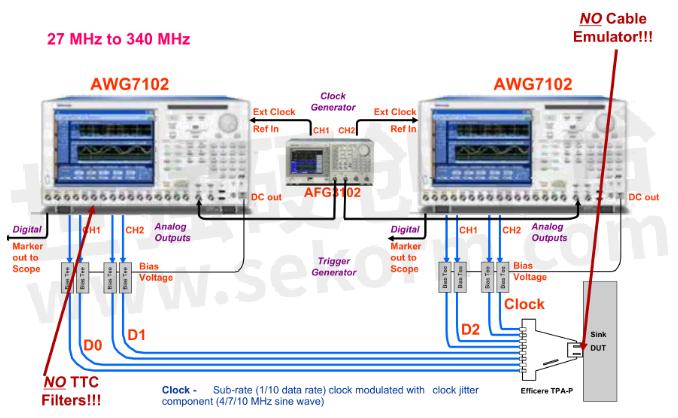

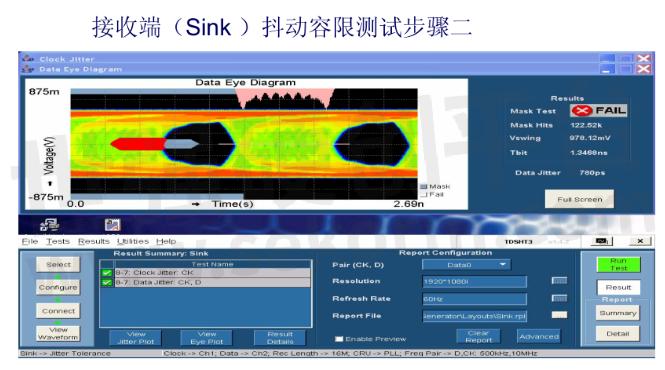

接收端(Sink)抖动容限测试步骤二

●获得TP1的眼图

·可选方法一

-按照340 MHz TMDS时钟频率的要求在TMDS的信号上加上相应的TTC,获得TP1的眼图。

·可选方法二

-按照每一种测试时钟频率的要求在TMDS的信号上加上相应的TTC,获得TP1的眼图。

在TP1上注入025*TBIT的时钟抖动成分和0.3*TBIT的数据抖动成分(可以使用两种抖动注入的方式)

通过Cable Emulator将TMDS信号输入被测的Sink设备。

逐步调节TMDS_CLOCK与TMDS_DATA之间的skew值:以0.1TBIT的步进进行扫描:例如0.0TBIT,0.1TBIT..1.0TBIT.如果Sink设备在任意一个测试点出现fails'则测试结果Fail

图 3

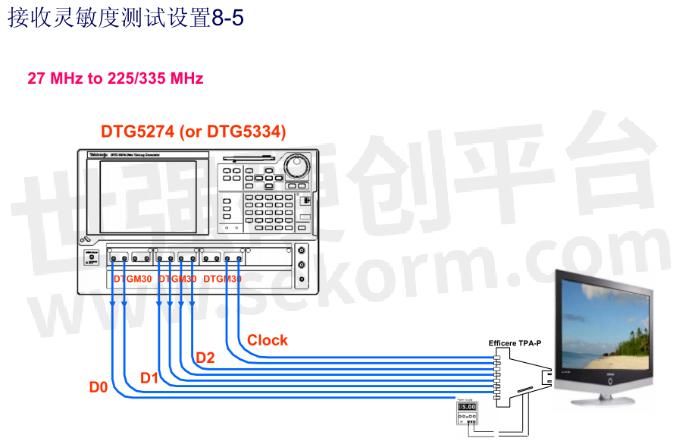

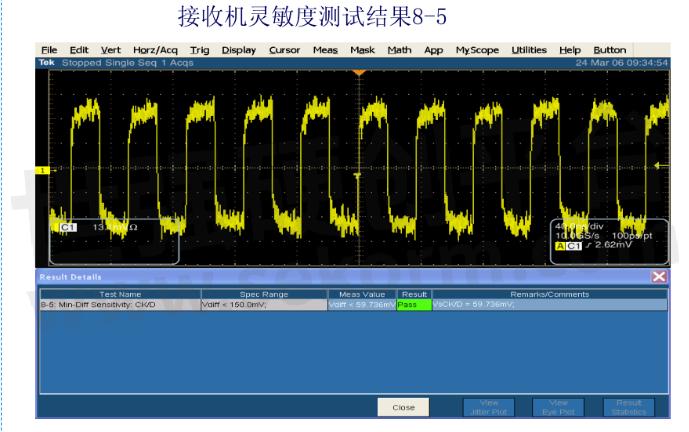

02.接收灵敏度

图 4

接收机灵敏度测试流程8-5

●第1步:为DTG配置RGB灰色锯齿码型

●第2步:如果TMDS Clock Rate>165hz,把DTG共模电压设为2.9V,如果TMDS Clock Rate<165hz,把DTG共模电压设为3V。

●第3步:把差分电压摆幅设为170mV

●第4步:检查DUT,如果工作正常,则转入下一步:如果设备测试不合格

●第5步:以每步20mV降低差分电压摆幅Vswing

●第6步:检查设备什么时候测试不合格

●第7步:把信号连接到示波器上

●第8步:测量差分电压摆幅Vswing

●第9步:如果差分摆幅大于150mV,设备测试不合格。如果差分摆幅小于150mV,设备测试合格

●第10步:将共模电压设置为3.3V,重复以上测试。

●第11步:将共模电压设置为3.3V,逻辑摆幅设置为1.2V,观察Sink设备是否支特此电平信号。

图 5

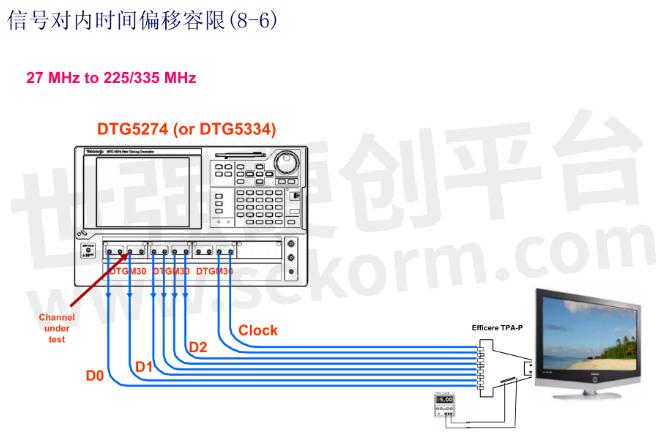

03.信号对内时间偏移容限

图 6

信号对内时间偏移容限(8-6)

●配置TMDS信号源输出Sink所支持的最高时钟速率的信号,

-设置所有的TMDS信号的共模电压为3.05V逻辑摆幅为500mV

-连接TPA-P到HDMI Sink DUT.

-针对每一对TMDS clock和data均进行下面的测试:

·配置TMDS信号源使其可以对TMDS+和-信号调节Skew

·以小于等于0.1*TBIT步进(Differential Timing Offset)逐步增大直到Sink DUT出现输出错误或着到达0.6*TBIT或1nsec.

·如果出现输出错误:

-以一个步进减少skew,直到Sink DUT不出现输出错误.

-如果TMDS clock frequency<=222.75MHz:intra-pair skew 0.4*TBIT,then FAlL.

-如果(TMDS clock frequency>222.75MHz:intra-pair skew 112psecs +0.15TBIT,then FAIL.

·在相反的方向增加skw再进行一遍测试。

·在所有的TMDS信号上进行测试

·由干DTGM30模块不能在差分输出之间调节skew,所以必须将敲测的差分对分别连接到两组差分输出的DATA+信号上,这也是为什么要使用3个DTGM30模块的原因。

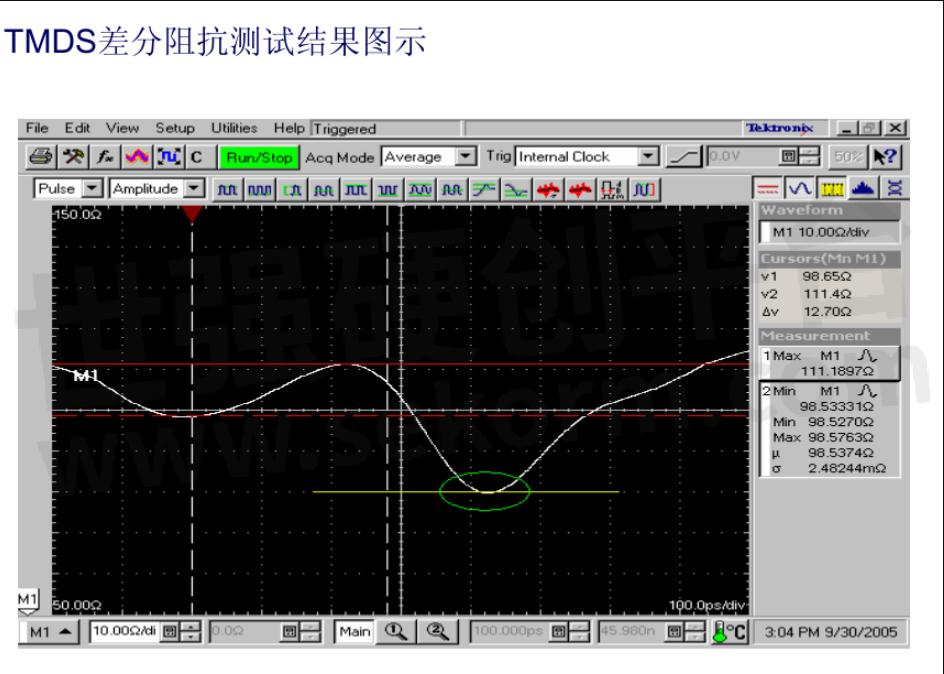

03.差分阻抗测试

图 7

TMDS差分阻抗测试步骤

·第1步:按照图示连接Fixture和DUT

·第2步:通过Filter的设置使TDR的Rise time为200ps.

第3步:进行Skew的校准

当DUT power on时:

-如果(ZDIFF_LOW <750Ω) OR (ZDIFF_HI>1250Ω)then FAIL

-如果(ZDIFF_LOW<85Ω) OR (ZDIFF_Hl>115Ω)则当偏离区间大于250ps,then Fail.

·当DUT power off时:

-如果(ZDIFF_LOW<750OΩ) OR (ZDIFF_HI>1250Ω)then FAIL

-如果(ZDIFF_LOW<850Ω) OR (ZDIFF_HI>115Ω)则当偏离区间大于250ps,then Fail.

·注意ATC只进行Power off情况下测试。

TMDS差分阻抗测试结果图示

图 8

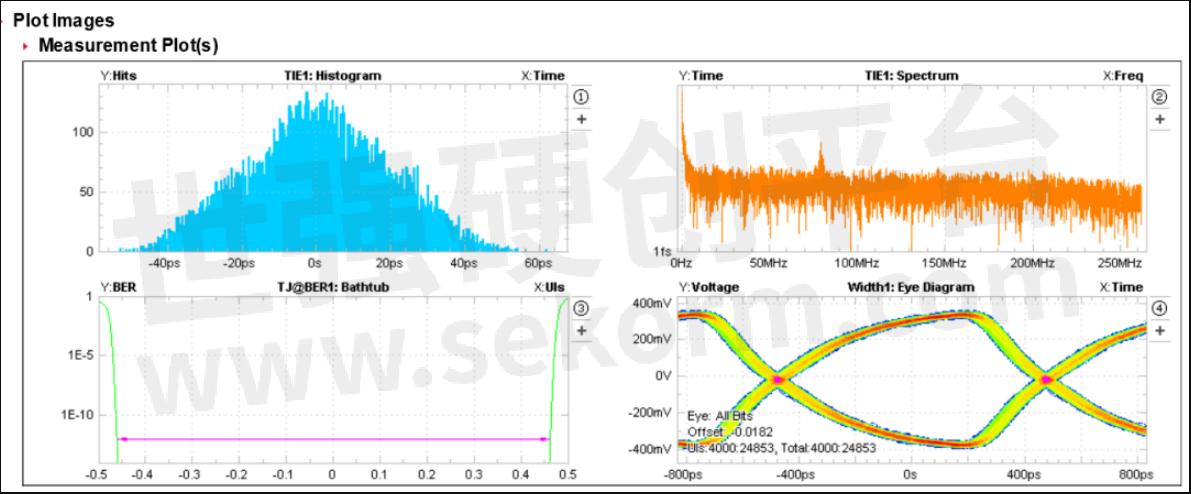

HDMI Sink 眼图测试

HDMI Sink 端眼图测试环境

●P7516 16G 差分探头

●眼图及抖动分析软件

测试实物图

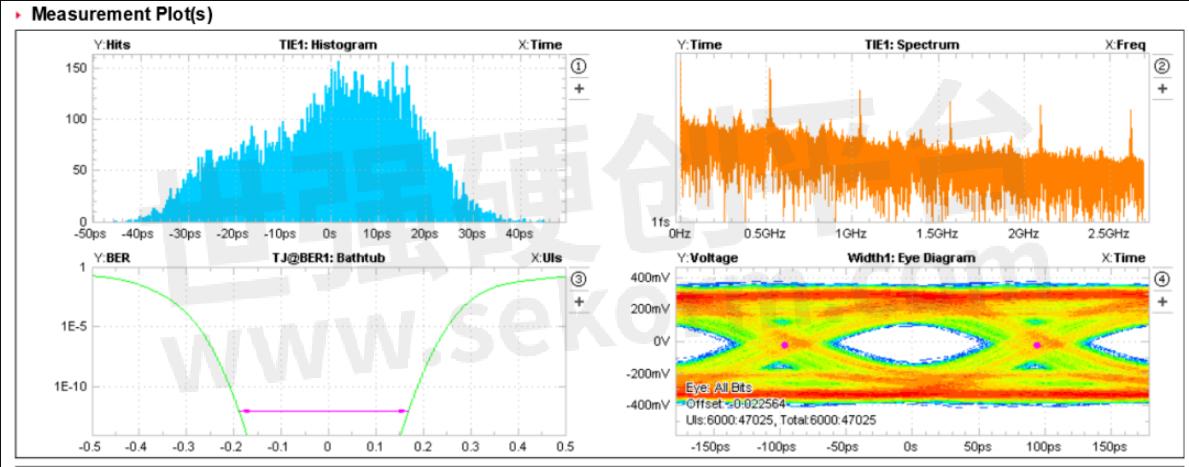

●CLK眼图:

图 9

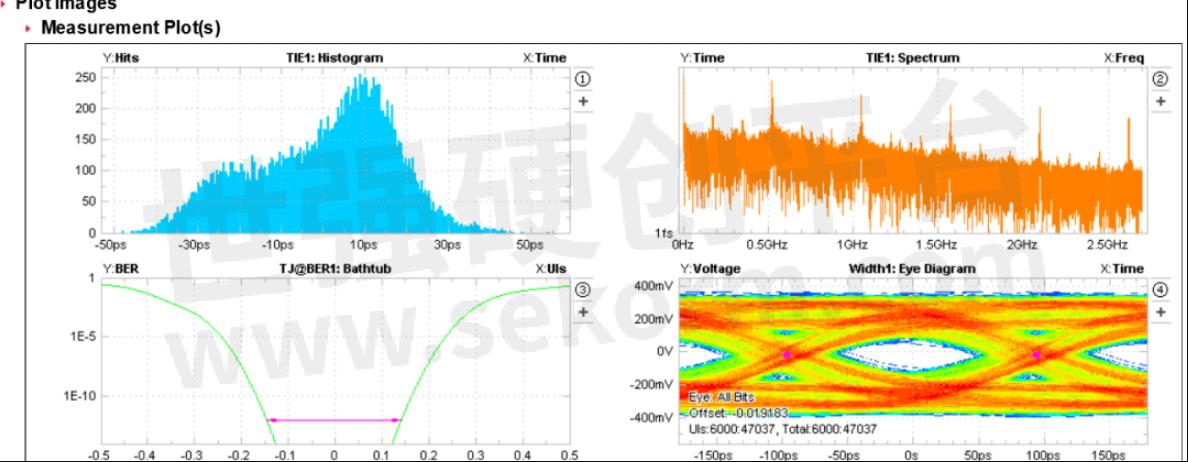

●D0眼图:

图 10

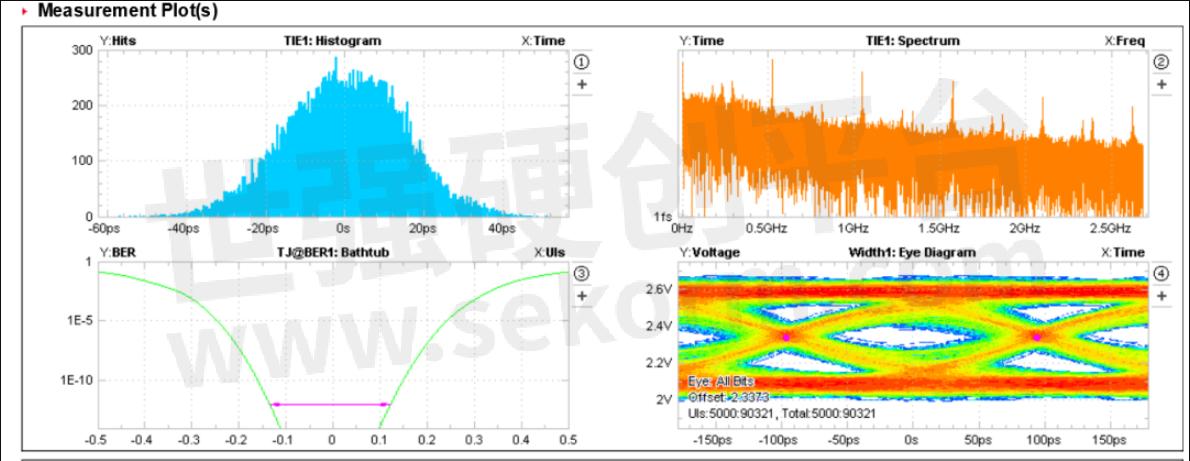

●D1眼图:

图 11

●D2眼图:

图 12

淼森波HDMI 测试夹具:

图 13

在进行HDMI sink端测试时,有几个注意事项:

1. 确保连接正确:将HDMI输出源设备(如电脑、DVD播放器、游戏机等)的HDMI输出接口与HDMI sink端连接起来。确保连接稳定,并且插头没有异常。

2. 分辨率设置:在进行测试之前,确保HDMI sink端的分辨率设置与源设备的输出分辨率匹配。这可以通过源设备的设置菜单或HDMI sink端的设置菜单进行调整。

3. 输入源选择:如果HDMI sink端有多个HDMI输入接口,确保正确选择与源设备连接的输入接口。有些HDMI sink端可能会自动切换输入源,但其他可能需要手动选择。

4. 输出信号检测:在进行测试之前,检查HDMI sink端是否能够正确地检测到输入信号。通常会有一个指示灯或显示屏来指示输入信号的状态。

5. 高质量的HDMI线缆:选择质量可靠的HDMI线缆,确保信号传输的稳定性和可靠性。低质量的线缆可能导致信号丢失或图像质量下降。

6. 多功能测试:在测试HDMI sink端时,可以进行多个方面的测试,例如音频输出测试、色彩准确性测试、图像质量测试等。这样可以全面评估HDMI sink端的性能和功能。

以上是进行HDMI sink端测试时需要注意的一些事项。如果遇到问题或需要进一步帮助,可以提供更具体的情况,测试先生将尽力提供相关支持。

- |

- +1 赞 0

- 收藏

- 评论 0

本文由三年不鸣转载自淼淼波公众号,原文标题为:【测试那点事儿】HDMI Sink 一致性测试及眼图测试案例,本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关研发服务和供应服务

相关推荐

MIPI接口闪屏怎么解决?

在现代移动设备中,MIPI(移动行业处理器接口)因其高速串行数据传输能力被广泛应用于显示屏和摄像头模块。然而,用户在使用这些设备时可能会遇到闪屏现象,即图像频繁闪烁或不稳定。本文将深入探讨MIPI接口闪屏的成因及解决方案。

设计经验 发布时间 : 2024-11-08

解析LPDDR4硬件设计及测试注意事项

LPDDR4(Low Power Double Data Rate fourth generation)是一种低功耗的存储器标准,用于移动设备和便携式应用。本文中Misenbo为大家介绍LPDDR4硬件设计及测试注意事项。

设计经验 发布时间 : 2023-12-30

【经验】淼森波实验室DDR测试案例,如何区分DDR1,DDR2,DDR3,DDR4还有DDR5?

DDR1、DDR2、DDR3、DDR4和DDR5都是不同类型的同步动态随机存取存储器,它们提供了不同的性能和带宽,并不断演进和发展。 都是不同类型的内存规格,它们的速度、带宽、工作电压和能耗等方面都有所不同,DDR5 内存规格最高,速度最快,带宽最宽,能耗最低。

设计经验 发布时间 : 2023-08-01

一文带您了解什么是Cable S参数验证测试

线材S参数测试是电子测量技术中的一个重要环节,主要涉及到微波、射频、高速数字和高速串行通信领域。S参数(散射参数)是描述网络输入与输出之间关系的一组参数,它们反映了信号在网络中的传输性能。本文中Misenbo来给大家介绍Cable S参数验证测试,希望对各位工程师有所帮助。

技术探讨 发布时间 : 2024-06-30

解析Cable S参数验证测试

线材S参数测试是电子测量技术中的一个重要环节,主要涉及到微波、射频、高速数字和高速串行通信领域。S参数(散射参数)是描述网络输入与输出之间关系的一组参数,它们反映了信号在网络中的传输性能。本文Misenbo淼森波将为您进行介绍。

技术探讨 发布时间 : 2024-06-20

TDR信号完整性测试案例

Misenbo淼森波硬件共享实验室分享TDR信号完整性测试案例。

应用方案 发布时间 : 2024-06-11

淼森波测试共享实验室接受板外接口一致性测试和板内信号质量测量,主要适用于仪器设备、无人机等场景

宁波淼森波信息技术有限公司棣属于北京淼森波信息技术有限公司,是一家技术服务型公司,即为中小型、初创型企业提供硬件开发配套服务和硬件测试服务。秉承“为中小型企业降低成本,提高工作效率”的服务宗旨。主要提供开放实验室测试、硬件单板测试、实验室的信息化管理、仪器租赁等业务。

原厂动态 发布时间 : 2023-09-05

淼森波荣获“AAA”级信用企业、质量管理体系认证资质,可提供多种测试与仿真业务

恭喜淼森波实验室获得《企业信用等级证书》、《质量管理体系认证证书》。北京淼森波信息技术有限公司(Misenbo)主要致力于智能硬件共享实验室服务、物联网产品研发、硬件测试外包服务、仪器设备租赁服务、硬件工程师培训等。

原厂动态 发布时间 : 2023-02-14

详解DDR技术内核 及Layout注意事项

这些是一些常见的DDR走线规则,当然,具体的规则可能因DDR版本、芯片厂商和PCB设计要求而有所不同。在进行DDR走线设计时,务必参考相关的DDR规范和芯片厂商的建议,以确保良好的信号完整性和性能。

技术探讨 发布时间 : 2023-11-01

DDR芯片的PCB设计要点

DDR PCB布局设计需要考虑诸多因素,包括DDR规格、频率、时钟速度等。因此,确保与DDR芯片厂商的规格和设计要求保持良好的沟通和协作,是非常重要的。

技术探讨 发布时间 : 2023-12-01

解析DDR信号完整性测试内容、技巧及注意事项

DDR(双数据速率)信号完整性测试是对DDR系统中信号传输的稳定性和准确性进行验证的过程。那么关于DDR信号完整性测试的内容、技巧及注意事项您有了解吗?本文将为您进行详细介绍。

技术探讨 发布时间 : 2024-05-09

DDR3信号速率问题详解

MISENBO实验室探讨了DDR3内存速率不足的问题,指出时序、信号质量、串扰、电源噪声和等长匹配是主要原因。建议使用等长设计、差分信号、优化电源和终端电阻来解决这些问题。实验室提供高速信号测试和硬件研发服务,帮助提升DDR性能。

技术探讨 发布时间 : 2024-11-04

LVDS闪屏的原因及解决办法

LVDS(低电压差分信号)闪屏问题通常指的是显示屏在使用过程中出现闪烁或不稳定的现象。本文将为您介绍 LVDS(低电压差分信号)闪屏的原因及解决办法。

设计经验 发布时间 : 2024-09-06

1000M以太网信号测试不过,咋办?

1000M以太网物理层一致性测试中模板测试不过,通常表明被测试设备(DUT)在物理层上未能满足IEEE 802.3标准中规定的要求。物理层是OSI模型的第一层,主要负责在介质上发送和接收原始比特流。要解决此类问题,通常需要从以下几个方面去入手。

设计经验 发布时间 : 2024-10-26

服务

根据用户的接口模块,使用是德示波器及夹具查看实时眼图演示,测试USB/MIPI/DDR/SATA/HDMI协议,支持最高到1.2GHz的实时眼图协议测试。支持到场/视频直播测试,资深专家全程指导。

实验室地址: 深圳 提交需求>

深圳市启威测实验室,面向所有企业提供信号完整性测试服务,主要包括USB、HDMI 、DP、MIPI、PCIe 、SD/EMMC、DDR接口信号测试。测试手段有波形测试、眼图测试、抖动测试等。

提交需求>

登录 | 立即注册

提交评论